1)实验平台:正点原子领航者ZYNQ开发板

2)平台购买地址:https://item.taobao.com/item.htm?&id=606160108761

3)全套实验源码+手册+视频下载地址:http://www.openedv.com/thread-301505-1-1.html

4)对正点原子FPGA感兴趣的同学可以加群讨论:994244016

5)关注正点原子公众号,获取最新资料更新

第三章 硬件资源详解

本章,我们将向大家详细介绍领航者ZYNQ开发板各部分的硬件原理图,让大家对领航者ZYNQ开发板的各部分硬件原理有个深入理解,并向大家介绍开发板的使用注意事项,为后面的学习做好准备。

本章包括以下几个部分:

1.1 领航者ZYNQ的IO分配

1.2 核心板外设详解

1.3 底板外设详解

1.4 开发板使用注意事项

1.5 ZYNQ的学习方法

1.1 领航者ZYNQ的IO分配

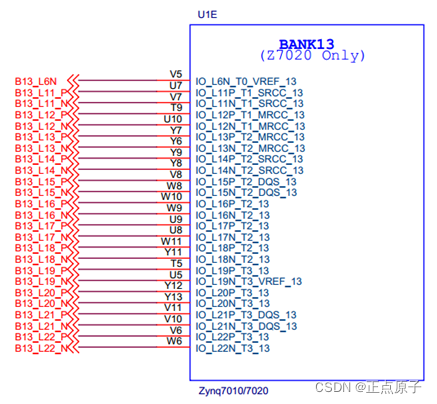

ZYNQ-7020核心板的主控芯片为XC7Z020CLG400-2,ZYNQ-7010核心板的主控芯片为XC7Z010CLG400-1。XC7Z020芯片比XC7Z010芯片多出一个BANK,即BANK13,我们将BANK13的IO引出至J4扩展口,因此J4扩展口仅ZYNQ-7020核心板支持。

XC7Z020芯片有6个用户I/O BANK(比XC7Z010多一个BANK)和最大253个用户I/O,了解器件的IO分配方式,有助于我们在硬件设计时根据器件的一些约束,对设计进行合理的IO分配,减少硬件出错的可能性。ZYNQ的IO口分成了PL和PS两部分,我们将分别介绍PL和PS两部分的IO分配。

1.1.1 PL端的IO分配

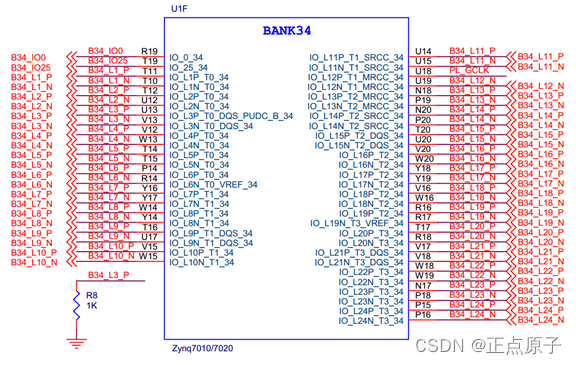

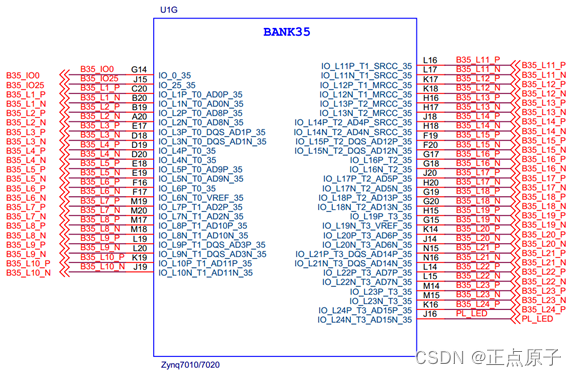

ZYNQ的PL侧和传统FPGA一样,可以灵活地分配到不同的IO口上。在XC7Z020中,PL端的IO被分成了3组,每一组称为一个IO Bank,分别是BANK13、BANK34、BANK35。同一个Bank中的所有IO供电相同,而各个Bank的IO供电可以不同,领航者开发板都将它们连接到了3.3V的电源上。PL端的3个IO BANK分别如图 3.1.1.1、图 3.1.1.2和图 3.1.1.3所示:

图 3.1.1.1 PL端的BANK13

图 3.1.1.2 PL端的BANK34

图 3.1.1.3 PL端的BANK35

需要说明的是,XC7Z020芯片比XC7Z010芯片多出一个BANK13,XC7Z020芯片比XC7Z010芯片多出一个BANK,即BANK13,我们将BANK13的IO引出至J4扩展口,因此J4扩展口仅ZYNQ-7020核心板支持。

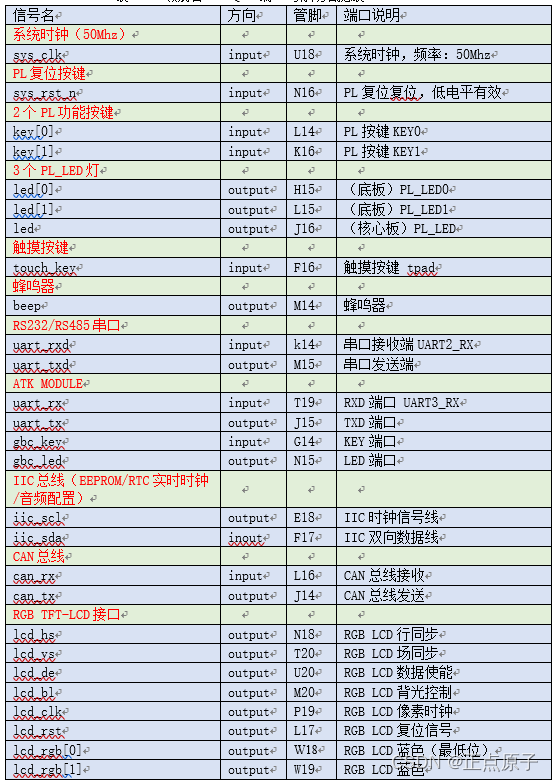

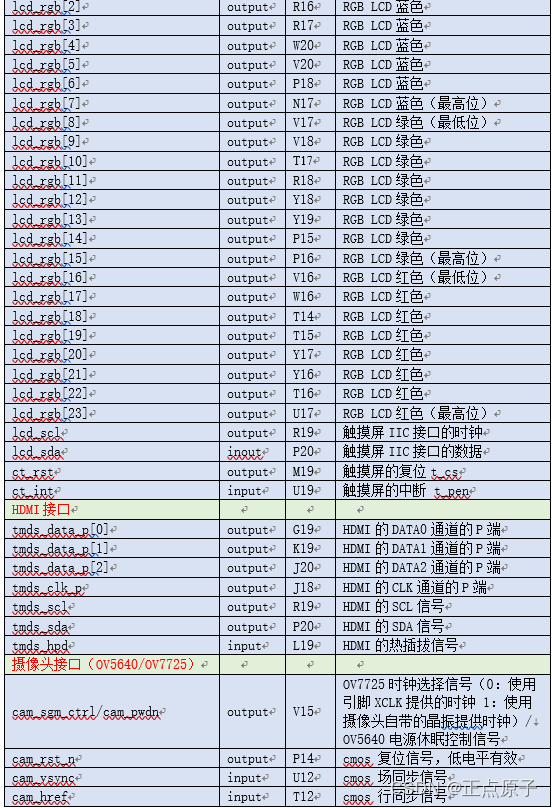

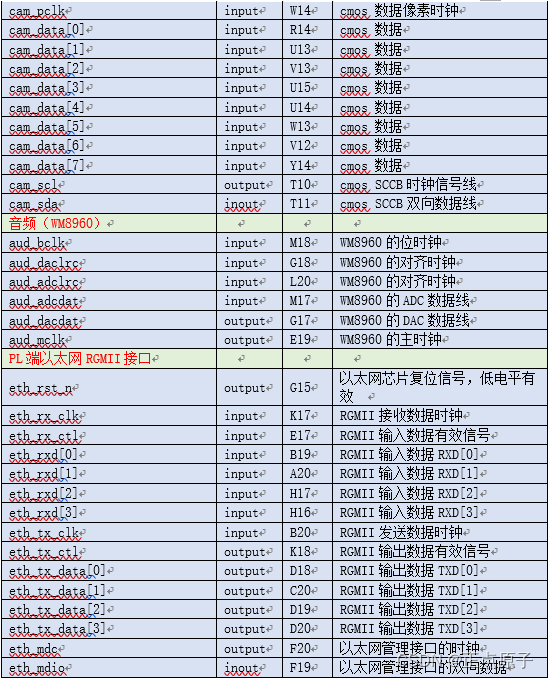

为了让大家更快更好的使用我们的领航者ZYNQ开发板,这里特地将ZYNQ PL端的IO引脚分配做了一个总表,以便大家查阅。领航者ZYNQ PL端IO引脚分配总表如下表所示:

表 3.1.1 领航者ZYNQ PL端IO引脚分配总表

在上表中,表格中列出来了除扩展口外,开发板上所有的PL IO引脚,扩展口上的引脚IO可以参考开发板的原理图或者直接查看开发板上的丝印标注。

另外在资料盘(A盘)→3_正点原子领航者ZYNQ开发板原理图文件夹下,有提供Excel格式的管脚分配表格,表格里共两个工作表,一个是“PL IO引脚列表”,另一个是“PS IO引脚列表”,方便大家查看。

1.1.2 PS端的IO分配

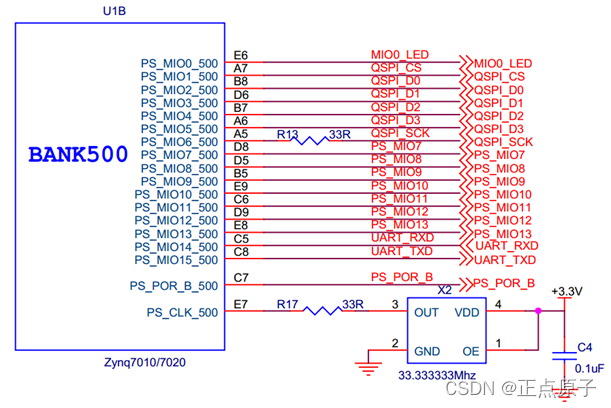

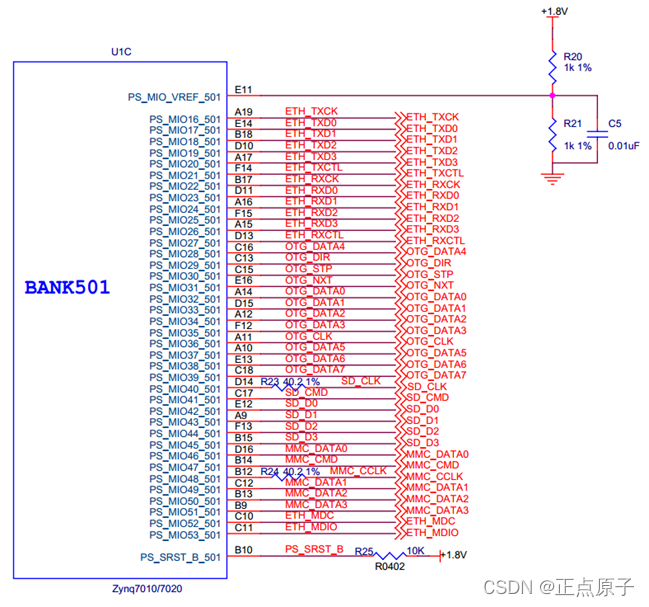

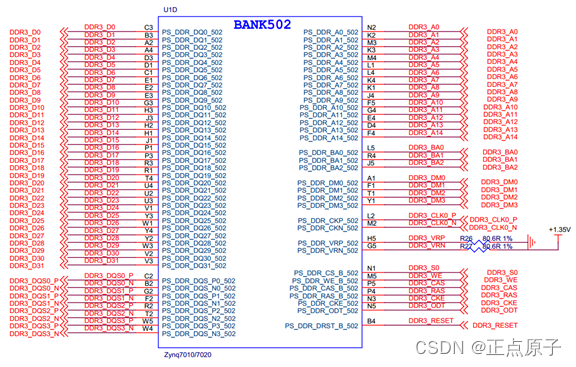

在ZYNQ PS端同样也包含了3个IO BANK,如下图所示:

图 3.1.2.1 PS端的BANK500

图 3.1.2.2 PS端的BANK501

图 3.1.2.3 PS端的BANK502

ZYNQ不同的IO BANK可以采用不同的供电电压,IO BANK的引脚电平和供电电压的电平保持一致,我们根据PS端连接不同的外设来选择不同的供电电压。BANK500、BANK501和BANK502分别采用3.3V、1.8V和1.35V供电。

与PL端IO BANK不同的是,PS端的IO连接是是相对固定的,用户不能够像PL引脚那样,将PS端的IO随意分配到某个外设。PS端外设的IO口与MIO(多路复用IO)之间,具有固定关系的映射,某个外设的IO口可能会映射到不同的MIO上,某个MIO也有可能会具有多个外设的IO口映射到其上面。两者之间的映射如下图所示:

图 3.1.2.4 PS端外设和MIO之间的映射

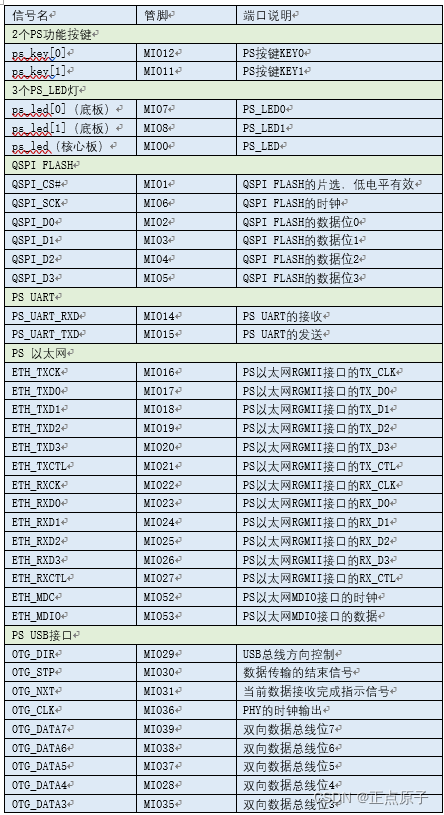

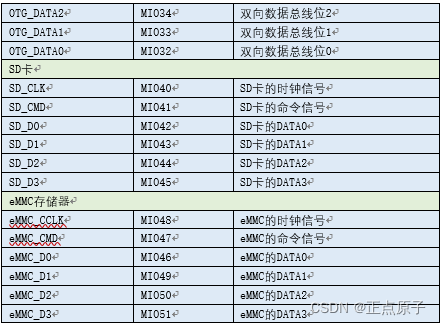

领航者ZYNQ开发板所使用到的所有外设与MIO之间所选择的映射关系如下表所示:

表 3.1.2 领航者ZYNQ PS端IO引脚分配总表

1.2 开发板底板原理图详解

1.2.1 底板电源

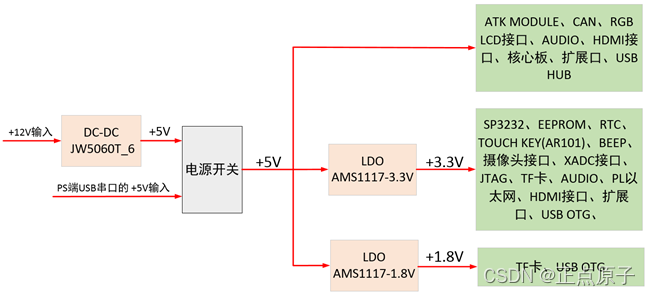

底板电源拓扑结构如下图所示:

图 3.2.1.1 底板电源拓扑

整个板子的电源来自电源适配器的12V供电电压,经过DC-DC芯片(型号为JW5060)之后,转变为系统+5V电压,再经过电源开关后,给系统供电,核心板的电源就来自系统+5V电压。PS端USB串口的+5V也可以用来给系统供电,但是需要特别注意,由于USB接口的驱动能力有限,所以不能驱动供电电流需求大的器件如LCD,这种情况下,请改用电源适配器供电。系统+5V电压除了直接驱动某些外设之外,还用于电压转换,LDO(线性稳压器)芯片AMS1117-3.3和AMS1117-1.8用于将系统+5V电压分别转变为+3.3V和+1.8V,然后给各个外设供电。

使用+5V电压供电的底板外设包括ATK MODULE、CAN、RGB LCD接口、AUDIO、HDMI接口、核心板、扩展口、USB HUB。使用+3.3V电压供电的底板外设包括RS232、EEPROM、RTC、TOUCH KEY、BEEP、摄像头接口、XADC接口、JTAG、Micro SD、AUDIO、PL以太网、HDMI接口、扩展口、USB OTG。使用+1.8V电压供电的底板外设包括Micro SD、USB OTG。电源适配器供电的电源接口原理图如下图所示:

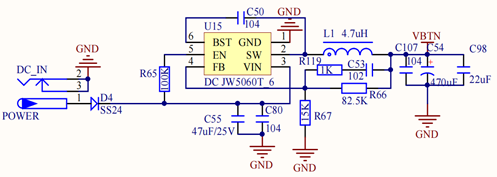

图 3.2.1.2 电源适配器供电电源接口

DC_IN用于外部直流电源输入,输入电压(12V)经过U15 DC-DC芯片转换为5V电源输出,其中D4是防反接二极管,避免外部直流电源极性接反的时候,烧坏开发板。

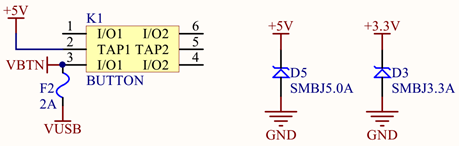

ZYNQ开发板底板的供电电源可以从电源适配器供电,也可以通过USB供电,无论通过哪种方式供电,都经过电源开关K1控制是否对开发板供电,其原理图如下图所示:

图 3.2.1.3 电源按键开关

VBTN为电源适配器输入的12V电压经电源转换芯片转换后得到的5V电压,VUSB为通过USB接口输入的电压。

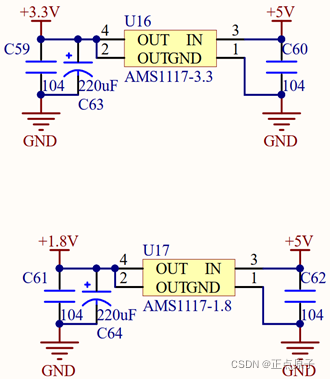

除了+5V电压之外, ZYNQ开发板底板还提供了3.3V、1.8V的电源电压,都是由5V电压转换而来,其电压转换电路原理图如下图所示:

图 3.2.1.4 电压转换电路

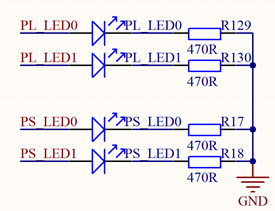

当电路接通后,LDO(线性稳压器)芯片AMS1117-3.3和AMS1117-1.8将系统+5V电压分别转变为+3.3V和+1.8V。通过电压转换芯片得到3.3V电压,点亮电源指示灯PWR,可以通过电源指示灯 PWR判断开发板供电是否正常。

除了这些之外,领航者ZYNQ开发板还板载了两组5V和3.3V输入输出接口,其原理图如下图所示:

1.4 开发板使用注意事项

为了让大家更好的使用领航者ZYNQ开发板,我们在这里总结该开发板使用的时候尤其要注意的一些问题,希望大家在使用的时候多多注意,以减少不必要的问题。

- 由于ZYNQ芯片工作电流较大,而USB供电电流最大500mA,所以使用USB串口进行供电可能会供电不足,建议大家使用一个电源适配器供电。

- 当你想使用某个IO口用作其他用处的时候,请先看看开发板的原理图,该IO口是否有连接在开发板的某个外设上,如果有,该外设的这个信号是否会对你的使用造成干扰,先确定无干扰,再使用这个IO。

- 开发板上需要连接跳帽的地方比较多,大家在使用某个功能的时候,要先查查实现这个功能是否需要连接跳帽,以免浪费时间。

- 当液晶显示白屏的时候,请先检查液晶模块是否插好(拔下来重新插试试),如果还不行,可以通过串口看看LCD ID是否正常,再做进一步的分析。

至此,本手册的实验平台领航者FPGA的硬件部分就介绍完了,了解了整个硬件对我们后面的学习会有很大帮助,有助于后面的管脚约束(分配),在编写程序的时候,可以事半功倍,希望大家细读!另外正点原子开发板的其他资料及教程更新,都可以在技术论坛www.openedv.com 下载到,大家可以经常去这个论坛获取更新的信息。

1.5 ZYNQ的学习方法

ZYNQ作为目前热门的SOC类处理器,正在被越来越多的公司选择使用。学习ZYNQ的朋友也越来越多,初学者可能会认为ZYNQ很难学,以前只学过51,或者甚至连51都没学过的,一看到ZYNQ就懵了。其实,万事开头难,只要掌握了方法,学好ZYNQ,还是非常简单的,这里我们总结学习ZYNQ的几个要点: - 一款实用的开发板。

这个是实验的基础,有时候软件仿真通过了,在板上并不一定能跑起来,而且有个开发板在手,什么东西都可以直观的看到,效果不是仿真能比的。但开发板不宜多,多了的话连自己都不知道该学哪个了,觉得这个也还可以,那个也不错,那就这个学半天,那个学半天,结果学个四不像。倒不如从一而终,学完一个再学另外一个。 - 掌握方法,勤学慎思。

ZYNQ不是妖魔鬼怪,不要畏难,ZYNQ的学习和普通单片机一样,基本方法就是: - 了解ZYNQ的基本结构。

学习ZYNQ之前需要先对ZYNQ的基本结构和其功能有个大概的了解,如PS、AXI总线、锁相环PLL、FIFO等。需要知道PLL是用来产生不同频率的时钟,如使用WM8960(音频编解码芯片)时需要生成12MHz的时钟;FIFO用于数据的缓存和异步时钟域数据的传递等。 - 了解Verilog HDL基本语法

没有软件的硬件就如同行尸走肉一般。软件是硬件的灵魂,硬件是软件的舞台。好的软件设计才能发挥硬件的性能,而软件的精髓在于代码。学习FPGA也是这样,Verilog HDL做为一种硬件描述语言,是对数字电路的一种描述,而数字电路是并行工作的,因而在编写Verilog HDL时要有并行的思想,不同于软件设计语言,软件设计语言是由CPU统一进行处理,一条指令一条指令的串行运行,所以软件设计语言是基于串行的设计思想,因而在写Verilog HDL代码的时候要注意这种差别。另外对于Verilog HDL的基本语法是务必要掌握的,如一般常用的module/endmodule、input/output/inout、wire/reg、begin/end、posedge/negedge、always/assign、if/else、case/default/endcase/parameter/localparam等关键字要清楚它们的作用和区别。掌握了Verilog HDL的基本语法和Verilog HDL的并行设计思想后,会觉得Verilog HDL和C语言一样简单。 - ZYNQ PS的学习

学习ZYNQ PS首先要了解C语言的基本语法。然后了解PS端基本的系统框架和外设,例如PS端架构、片内互连、AXI总线、DDR控制器等等。最关键的是PS端的C程序。软件系统可以被认为是建立于基于硬件的系统上的一个栈,或者说是一系列层,从底至上依次是基础硬件系统(来自Vivado的自定义硬件)、板级支持包、Operating System、软件应用。

初学者可以多看看官方的文档和资料,对于PS端的软件,xilinx提供了丰富的库函数,很多时候用户直接调用调用即可,读者要学会利用这些库函数。遇到问题时,读者可以借助xilinx的SDK开发环境中的各种调试功能来定位错误,以帮助解决问题。 - 多思考,多动手。

所谓熟能生巧,先要熟,才能巧。如何熟悉?这就要靠大家自己动手,多多练习了,光看或说是没什么太多用的。只有在使用ZYNQ的过程中,才会一点点的熟悉,也只有动手实练,才能对FPGA有切实的感受。

熟悉了之后,就应该进一步思考,也就是所谓的巧了。我们提供了几十个例程,供大家学习,跟着例程走,无非就是熟悉ZYNQ的过程,只有进一步思考,才能更好的掌握ZYNQ,也即所谓的举一反三。例程是死的,人是活的,所以,可以在例程的基础上,自由发挥,实现更多的其他功能,并总结规律,为以后的学习和使用打下坚实的基础,如此,方能信手拈来。

所以,学习一定要自己动手,光看视频,光看文档,是不行的。举个简单的例子,你看视频,教你如何煮饭,几分钟估计你就觉得学会了。实际上你可以自己测试下,是否真能煮好?机会总是留给有准备的人,只有平时多做准备,才可能抓住机会。

只要以上三点做好了,学习ZYNQ基本上就不会有什么太大问题了。如果遇到问题,可以在我们的技术论坛:开源电子网:www.openedv.com 提问,论坛FPGA板块有各种主题,很多疑问已经有网友提过了,所以可以在论坛先搜索一下,很多时候,就可以直接找到答案了。论坛是一个分享交流的好地方,是一个可以让大家互相学习,互相提高的平台,所以有时间,可以多上去看看。

233

233

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?