系列文章目录

计算机底层原理

前言

带你深入理解计算机底层原理,为日后写出更健壮更安全更高效的代码打下坚实的基础,计算机硬件最底层的实现就如同建筑物的地基,清晰地掌握底层原理对大家将来编程工作都会大有裨益,当然在为大家讲解的同时也会为大家先介绍一些辅助知识,为我们了解计算机底层原理做一个铺垫。

一、主机是什么?

1.主机的概念

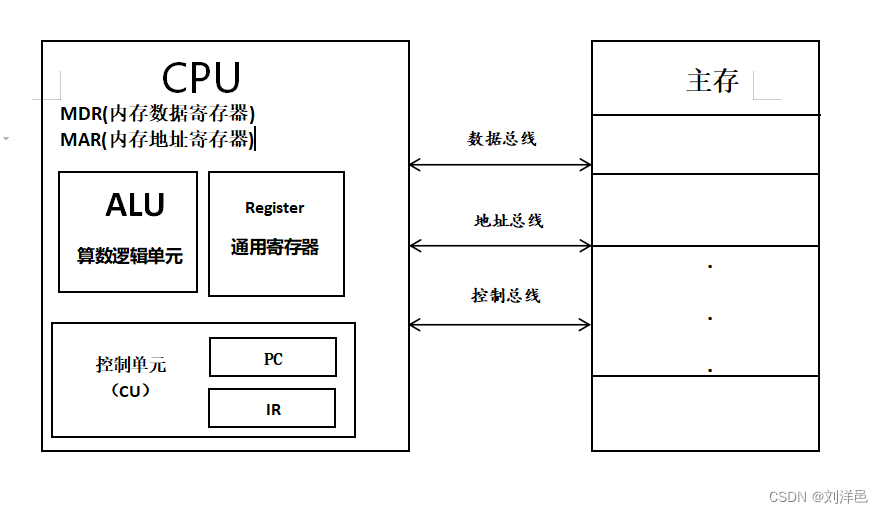

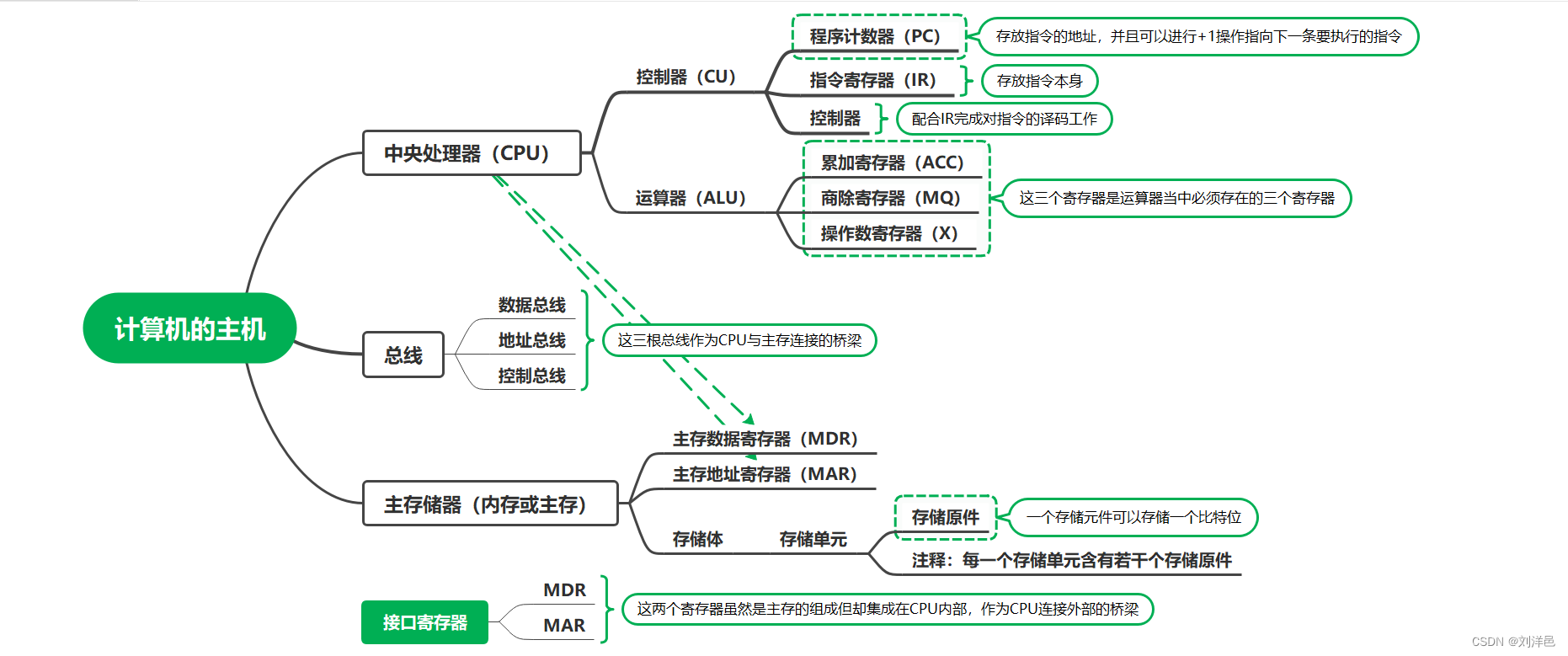

主机是由中央处理器(CPU)和主存储器(主存或者内存)构成。

2.CPU的组成

1)运算器:算术逻辑单元(ALU)以及一些列的寄存器构成,其中累加寄存器、商除寄存器、操作数寄存器(运算器必须含有的三大寄存器)等寄存器。

2)控制器:由三部分构成,包括控制单元、程序计数器(PC)、指令寄存器(IR)。

3)通用寄存器:暂时存放操作数的寄存器。

4)内存地址寄存器(MAR):存放来自内存的操作数的地址。

5)内存数据寄存器(MDR):存放来自内存操作数本身。

注意:MDR、MAR这两个寄存器是属于内存的,但是集成在CPU的芯片上。

3.概念图

详解: 处理器与主存是通过总线相连的,共有数据总线、地址总线、控制总线三条总线才可以实现二者的联通。

4.思维导图

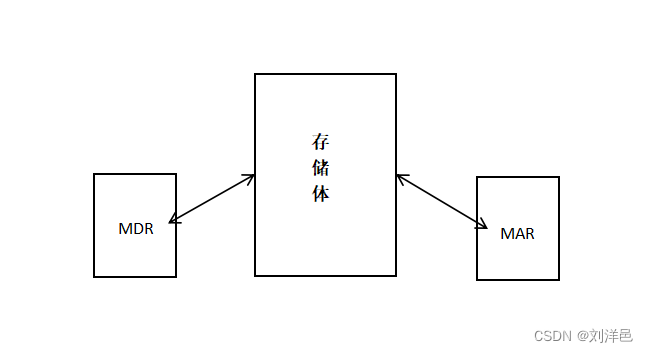

二、主存的构成

1.结构组成

1)存储体、MDR、MAR。

2)内存本质上是一个存储字节的线性数组,这个数组中的存储单元存储着数据、指令等内容,每一个存储单元旁边都有唯一的二进制地址来对其进行唯一的标识。

2.概念图

3.概念图详解:

1)存储体当中有着许多的存储单元,每个存储单元都有着一个存储元件,每一个存储元件都可以存储一个比特位(0或1)。

2)MDR存储着数据、MAR存放着数据的地址。

3)这两个寄存器虽然是主存的组成部分但是却集成在CPU的芯片上面,这两个寄存器是连接处理器(CPU)和主存的桥梁。

三、处理器与主存的信息传递

1.工作流程图

2.工作原理

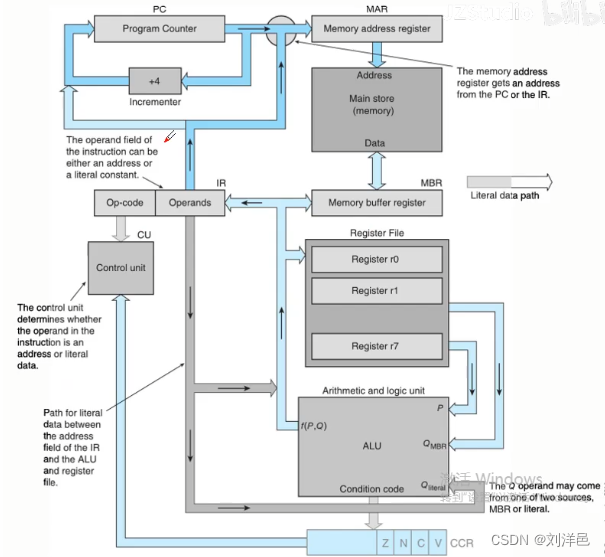

1、一个程序当中包含指令和数据两大部分,当一个内存中的进程(程序的一次运行、也可以看作是程序的抽象)运行需要调用处理器(CPU)时,处理器需要获取进程当中相应的指令以及数据。

2、CPU从内存中读取数据和指令的时候,二者之间的控制总线会提前发出命令,判断CPU要从内存当中进行读操作还是写操作,判断是读操作以后,内存中的指令的地址会通过地址总线到达MAR,然后由MAR传输给PC,由PC对指令进行保存。

3、接下来指令会通过数据总线到达MDR,由MDR传输给IR,由IR分析以后将指令的操作码传输给CU(控制单元)有控制单元对指令的操作码进行译码,来识别指令想要进行什么样的操作,而指令的地址码则会由IR传输给MAR,由MAR通过控制总线、地址总线去内存里面将相应的数据取出来,放到CPU的通用寄存器当中。

4、指令的格式:

举例:现在我在源程序当中定义了三个变量要进行加法操作,如下所示:

#include<stdio.h>

int main()

{

int x=2;

int y=3;

int z;

z=x+y;

printtf("%d",z);

return 0;

}

注释:

首先我们由I/O设备所书写的代码会议文件的形式呈现在外存(磁盘、磁带等外部存储设备),因为文件就是I/O设备的抽象,当我们用高级语言写好程序以后,这样的语言计算机时看不懂的,必须经过一系列的处理和翻译转换成机器语言(二进制文件),才能最终运行,大概介绍一下,翻译过程分为以下几个过程。

| 预处理 | 编译 | 汇编 | 链接 |

注释一:程序编译的相关基础知识

1)

预处理阶段:将头文件展开,并且和源文件包含在一起,我们定义的宏定义(define)也会用实际的数据替换。

2)

编译阶段:对高级语言进行编译(词法分析、语法分析等,想要详细了解的可以参照教材(编译原理)),将原有的高级语言翻译成为汇编语言(MOV、LOAD、STORE等汇编指令)。

3)

汇编阶段:将汇编指令翻译成为计算机可以识别的二进制文件。

4)

链接阶段:将汇编文件与库函数合并,比如说printf函数等库函数,最终生成可执行文件,此时我们点击运行就可以正常运行了。

注释二:操作系统有关的概念

1)进程的概念:

我们将代码写好以后会以文件的形式存放在磁盘当中,这个时候他是一个程序,当我们运行他以后,他会借助主机的一项技术(DMA,直接存储存取技术),此时磁盘当中的程序可以不经过CPU而直接复制到内存当中,这个就是我们平常所说的进程(进程就是程序的一次活动、进程就是程序的抽象,一个程序可以产生很多个进程)。

2)线程的概念:

既然提到了进程的概念那么就不得不谈一谈线程的概念,线程就是轻量级的进程,一个进程当中可以包含很多个线程,线程在进程当中资源共享并且相互独立,彼此间互不干扰。

可能说到这里依然会有很多的小伙伴感到很困惑,感觉线程还是很抽象,其实我只要举个例子大家就能很容易的明白了,相比大家都对360杀毒软件有着很深的了解,那么我们就以他为例,360这个软件本身只是一个程序,你只要不去碰它,他就是一个在磁盘的文件当中存放的一个程序,但是只要我们双击这个程序,这个程序就会立刻在内存当中形成一个进程,这个时候我们的任务管理器就有了360这个进程,那么360这个软件当中是由很多的子功能的,其中包括(木马查杀、垃圾清理、病毒扫描等等一系列的子功能),那么请问这些子功能之间的实现是否相互干扰呢?他们之间是否彼此独立呢?答案是肯定的,垃圾清理和病毒扫描之间是可以同时进行的,这些子功能就是这个进程里面的线程,如果没有这些线程的话,那么这些子功能只能按照顺序来执行,显然这样会降低程序执行的效率。

3)并发和并行的概念:

并发:指在一个时间间隔内进程或线程按照一定的次序(涉及到调度算法,这里就不做详细的介绍了)先后执行,从宏观上来看是同时发生的,但是从微观角度上来看的话其实是一个一个来执行的。

并行:这个就是严格意义上讲的同时运行,在同一时刻同时运行,并行是有着一定的物理极限的,一个CPU通常每次只能运行一个线程,现代计算机(四核八线程),四个CPU每次可以运行八个线程,这就好比我们每个人只有两只手同一时刻只能同时做两件事一样,但是在一个时间间隔内,虽然我们只有两只手但却可以做很多件事情,前者是并行后者是并发。

| 操作码(指令的类型) | 地址码(操作数的地址) |

注释:

指令由两个部分组成,一个是操作码另一个是地址码,操作码就是说明指令的类型,比如说ADD、LOAD、TEST等等,是为CPU说明操作数要进行的相关操作,我们在调度CPU进行运算的时候(此处专门说明一下,CPU就是专门做运算的硬件)不仅要把相应的数据复制到CPU中,还必须要把数据要进行怎样的操作告诉CPU,而地址码存放着的就是操作数(要进行运算的数据)的地址,CPU会根据操作数的从内存当中找到操作数。

3.高速缓冲存储器

1、静态RAM:静态RAM也叫高速缓冲存储器,之所以是静态的是因为他的集成芯片用到了六晶体管电路,这个电路抗干扰的能力非常强,不管断电还是电子信号干扰,只要信号回复以后,它里面所存储的数据都会恢复不会发生丢失。稳定性特别强。

2、动态RAM:也就是我们现在所使用的主存储器(内存)利用电容来实现,所以抗干扰的能力特别弱,基本上在10~100ms之间数据就会丢失,但是系统对于数据的读写是以ns为单位的,所以这就需要系统周期性的对内存当中的数据进行读入,并且重写这也就是数据的刷新。

总结:CPU的工作原理详细解说

在为大家介绍了上述的一系列的基础知识以后,现在将CPU到底是如何工作的为大家做一个详细的总结。

当程序(指令和数据的集合)运行进入到内存(存放字节序列的先行数组)以后,汇编指令、运算要用到的数据都按照一定的次序存放在内存当中,控制总线会最先决定CPU要到内存当中是进行读操作还是写操作,决定读操作以后,这个时候首先CPU要从内存当中通过MAR寄存器取走(复制)指令的地址,然后再由MAR寄存器将指令的地址复制给PC,PC会存放来自MAR的指令地址。

紧接着内存通过数据总线将指令本身传递给MDR寄存器,当然这个时候依然需要控制总线来决定CPU到内存当中进行读操作还是写操作,指令传递给MDR以后,MDR会将指令复制给IR寄存器,IR寄存器将指令进行拆分,其中指令的操作码部分(说明指令的类型,操作数要进行怎样的操作)传递给控制单元(CU),控制单元进行指令的译码,翻译以后CU会发出控制信号,告诉ALU(算术逻辑单元)接下来要进行怎样的操作。

而指令的另外一部分地址码(操作数的地址)则会被IR传送给MAR,MAR会根据操作数的地址通过地址总线将数据从内存当中取回。

取回的操作数会被存放在CPU当中的通用寄存器(通常由16个,每个操作数存占用一个寄存器)当中,这时候ALU由于已经接到了CU的控制信号,那么他就会从通用寄存器当中取出操作数,这个时候ALU会进行一系列的运算(算数运算、逻辑运算),当然ALU当中也有一系列的寄存器来辅助ALU进行运算,如ACC(累加寄存器)、MQ(商除寄存器)、X(操作数寄存器)等。

ALU运算工作完成以后会将结果在放回CPU的通用寄存器当中,CPU会将结果复制到MDR中,控制总线这个时候会发出控制命令,命令CPU到内存当中进行写操作,将运算结果再写入内存当中,传输数据的时候通过数据总线。

这个时候其实还会出现一个新的问题,就是ALU计算后将结果写回通用寄存器中所用的时间是CPU访问内存的1%,也就是CPU的性能远远超过了内存,两者之间相互访问的速度差太大,为了解决这一问题引入了高速缓冲寄存器。他的访问速度远远快与访问内存,所以将内存当中的数据在这里做一个备份,CPU可以直接访问缓存,这样就大大地提高了系统的效率。

结语:

近几年来我观察很多企业招聘面试环节(不仅仅只是大厂),我的一个学长今年在太原找实习面试的时候,面试官对于学生的计算机核心素养非常重视,针对计算机组成原理、操作系统、计算机网络面试时间长达一个半小时,起初我也觉得很不可思议,便立刻调整了学习方向,将更多的精力放在了计算机底层逻辑上,不过我的这位学长最终依靠自己强大的计算机知识底蕴通过了面试,拿到了太原一家企业的实习生offer,实习工资为8500元,转正以后月收入底薪1w+,每年14薪,要知道以太原的消费水平来看的话,这个收入已经至少超越了90%的人,而且我觉得在太原拿着这样的工资的幸福感绝对不比在一线城市拿着2w的工资差,而且太原的房价在1.6w左右远低于一线城市。我们学的大学(太原本地)教授有着几十年的教龄,他们的年收入也只有15w左右,所以我觉得这样的结果完全配得上他自己的努力了。

9670

9670

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?