计算机组成原理复习题

1. 某磁盘存储器转速为 3000 转/分,共有 4 个记录面,每毫米 5 道,每道记录信息为 12288字节,最小磁道直径为 230mm,共有 275 道。回答以下问题:

(1)磁盘存储器的容量是多少?

(2)最高位密度与最低位密度是多少?

(3)磁盘数据传输率是多少?

(4)平均等待时间是多少?

(1)12288B/道*275 道*4个面=13516800B(1 分)

(2)最高位密度12288B/(230mm*3.14)=17B/mm (1 分)

最低位密度12288B/(340mm*3.14)=11.5B/mm (1 分)

(3)磁盘数据传输率 Dr=r×N;(N 为每条磁道容量,N=12288B)

r 为磁盘转速,r=3000 转/分=3000 转/60 秒=50 转/秒

∴Dr=r×N=50×12288B=614400B/s; (2 分)

(4)磁盘旋转速度为50转/秒,磁盘旋转半周时间为 1/2r,即 10ms (2 分)

2.已知X和Y,用变形补码计算X-Y,同时指出结果是否溢出。

(1)X= 11011,Y= -11111

[x]补 = 00 11011;[y]补 = 11 00001;[-y]补 = 11 11111;

[x]补 = 00 11011

[-y]补 = 11 11111

[x-y]补= 00 11010 [x-y]原=00 00110 双符号位为00,结果为x-y = 00110

(2)X= 10111,Y= 11011

[x]补 = 00 11011;[y]补 = 00 11011;[-y]补 = 00 00101;

[x]补 = 00 11011

[-y]补 = 00 00101

[x-y]补= 01 00000 双符号位为01,结果为正溢

3.已知X= 00110011和Y= 10011110,求逻辑运算X∧Y、X∨Y和X⊕Y。

X∧Y=00010010

X∨Y=10111111

X⊕Y=10101101

4.某磁盘存储器的转速为M转/分钟,共有4个记录面,每磁道记录信息为N字节,共256道,问:

(1)磁盘存储器的存储容量是多少?

(2)数据的传输率是多少?

(3)平均等待时间是多少?

(1)存储容量=1024N字节

(2)D=rN=M/60×N=MN/60 B/s

(3)平均等待时间=1/2r=30/M s

5.设阶码3位,尾数6位,按浮点运算方法,完成下列取值的[x+y]计算:

x = 2011×0.100101, y = 2010×(-0.011110)

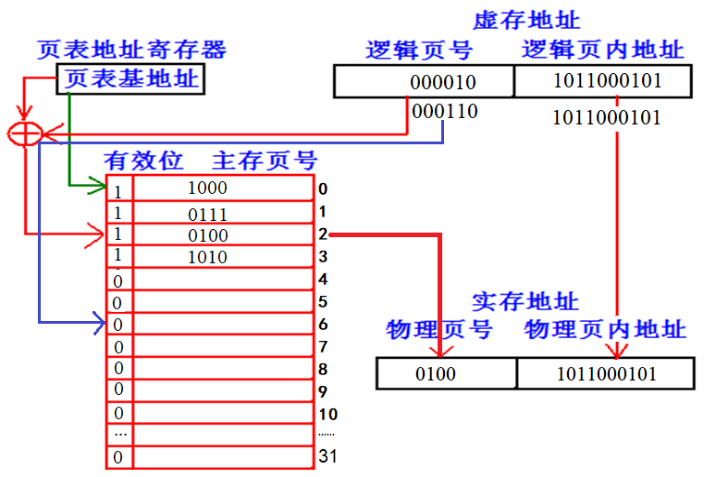

6.在一个分页虚存系统中,用户虚存地址空间为32页,页长1KB,主存物理空间为16KB。已知用户程序有10 页长,若虚页0、1、2、3已经被分别调入到主存8、7、4、10页中,请问虚地址0AC5和02C9对应的物理地址是多少?

7.设有一个具有12位地址和4位字长的存储器,问:

(1)该存储器能存储多少字节信息?

(2)如果存储器由1K*1的RAM芯片组成,需要多少片?

(3)画出该存储器的结构图

(1)4096×4/8=2K字节

(2)16片 12+4=16

(3)略

8.用8K*8位/片的存储芯片构成32KB存储器,地址线为A15(高位)~A0(低位)。

(1)需要几片这种存储芯片?

(2)32KB存储器共需要几位地址?是哪几位地址线?

(3)加至各芯片的片内地址线有几位?是哪几位地址线?

(4)用于产生片选信号的地址线是哪几位?

(1)32K/8K=4片

(2)存储器15位地址,A14(高位)~A0(低位)

(3)芯片片内地址13位,A12(高位)~A0(低位)

(4)A14(高)~A13(低)

9.某微机有5条微指令,每条微指令所发出的控制信号如下表所示,若控制字段为6位,请写出I1~I5每条微指令的编码。

微指令 控制信号

I1 a e c g

I2 a d e f

I3 a c g

I4 c d e

I5 a b e f

控制字段格式:

0 0 无

0 1 b

1 0 d

1 1 g

I1:111011;I2:101110;I3:11011;I4:011010;I5:101101;(每个编码 2 分)

10.请结合CPU内部框图,说明指令MOV R0,R1取指周期的六个步骤和执行周期的五个步骤?

取指周期

(1)程序技术器PC中装入第一条指令101;

(2)PC的内容被放到指令地址总线ABUS(I)上,对指存进行译码,并启动读命令;

(3)从101号地址读出的MOV指令通过指令总线IBUS装入指令寄存器IR;

(4)程序计数器内容+1,变成102,为取下一条指令做好准备;

(5)指令寄存器中的操作码(OP)被译码;

(6)CPU识别出是MOV指令。至此取指周期结束。

执行周期

(1)操作控制器(OC)送出控制信号到通用寄存器,选择R1(10)作源寄存器,选择R0作目标寄存器;

(2)OC送出控制信号到ALU,指定ALU做传送操作;

(3)OC送出控制信号,打开ALU输出三态门,将ALU输出送到数据总线DBUS上。注意,任何时候DBUS上只能有一个数据;

(4)OC送出控制信号,将DBUS上的数据打入到数据缓冲寄存器DR(10);

(5)OC送出控制信号,将DR中的数据10打入到目标寄存器R0,R0的内容由00变为10。至此,MOV指令执行结束。

11.流水中的主要存在哪三种问题?如表所示为五条指令进入流水线工作,请指出存在的问题,并给出解决方法?

一、结构相关

由于多条指令在同一时刻争用同一资源而形成的冲突称为结构相关,有以下两种解决办法:

(1) 前一指令访存时,使后一 条相关指令(以及其后续指令)暂停一 个时钟周期。

(2) 单独设置数据存储器和指令存储器,使两项操作各自在不同的存储器中进行,这属于资源重复配置。

类比操作系统中的互斥

二、数据相关

数据相关指在一个程序中,存在必须等前一条指令执行完才能执行后一条指令的情况,则这两条指令即为数据相关。当多条指令重叠处理时就会发生冲突,解决的办法有以下两种:

(1) 把遇到数据相关的指令及其后续指令都暂停 一至 几个时钟周期,直到数据相关问题消失 后再继续执行,可分为硬件阻塞(sta ll) 和软件插入“ NOP ”指令两种方法。

(2) 设置相关专用通路,即不等前一条指令把计算结果写回寄存器组,下一条指令也不再读 寄存器组, 而是直接把前一 条指令的 ALU 的计算结果作为自己的输入数据开始计算过程,使本 来需要暂停的操作变得可以继续执行,称为数据旁路技术。

(3) 通过编译器对数据相关的指令编译优化的方法,调整指令顺序来解决数据相 关。

类比于操作系统中的同步

三、控制相关

当流水线遇到转移指令和其他改变 PC 值的指令而造成断流时,会引起控制相关。解决的办法有以下几种:

(1) 对转移指令进行分支预测,尽早生成转移目标地址。分支预测分为简单(静态)预测和 动态预测。静态预测总是预测条件不满足,即继续执行分支指令的后续指令。动态预测根据程序 执行的历史情况,进行动态预测调整,有较高的预测准确率。

(2) 预取转移成功和不成功两个控制流方向上的目标指令。

(3) 加快和提前形成条件码。

(4) 提高转移方向的猜准率。

12.一个组相联cache由64个行组成,每组四行,主存储器包含4K个块,每块128个字。请表示内存地址的格式。

标记8位,组号4位,块内地址7位

13.有一个处理器,主存容量1MB,字长1B,块大小16B,cache容量64KB。若cache采用全相联映射,对内存地址B0010给出相应的标记和字号

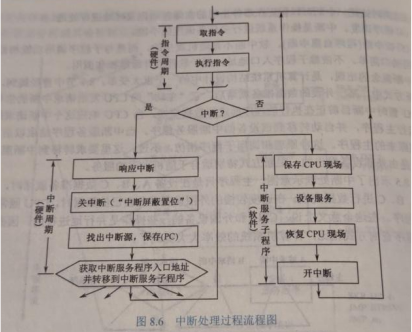

14.画出中断处理过程流程图

15. 某机有五个中断源,按中断响应的优先顺序由高到低为L0 L1 L2 L3 L4,现要求优先顺序改为L3 L2 L4 L0 L1,写出各中断源的屏蔽字

16.指令字长16位,每个操作数地址码长度6位 ,指令分为无操作数指令、单操作数指令和双操作数指令三类,若双操作数指令有M条,无操作数指令N条,问单操作数指令最多可能有多少条?

17.什么是中断?中断技术给计算机系统带来了什么作用?

中断是一种程序随机切换的方式,有时也统称为异常。当外部发生某些随机的事件需要及时处理时,无论CPU正在执行哪一条指令,都可以通过中断响应的方式暂停正在执行的主程序的执行,转而执行另外一段中断服务程序。在高优先级的中断服务程序执行完毕后,可以返回被打断的主程序“断点”继续执行。

中断技术给计算机系统带来了以下几点好处:

1. 提高系统的响应速度:中断技术可以使计算机系统在执行某个任务时,能够及时响应来自外部设备的请求或者其他紧急事件,从而提高系统的响应速度。

2. 实现多任务处理:中断技术可以使计算机系统能够同时处理多个任务,通过合理地设置中断优先级,可以保证重要任务的及时处理,提高系统的效率。

3. 提高系统的可靠性:中断技术可以使计算机系统在出现故障或异常情况时能够及时处理,避免系统崩溃或数据丢失。

4. 简化编程:中断技术可以使程序员更加方便地编写程序,不需要关注具体的硬件细节,只需要编写中断服务程序即可。

5. 实现实时性要求:对于嵌入式系统等对实时性要求较高的应用,中断技术可以保证系统能够及时响应外部事件,满足实时性要求。

中断技术给计算机系统带来了更高的响应速度、更好的多任务处理能力、更高的可靠性、更简化的编程方式以及满足实时性要求的能力。

18.指令和数据都存放在主存,如何识别从主存储器中取出的是指令还是数据?

指令和数据都存放在主存,它们都以二进制代码形式出现,区分的方法为:

(1)取指令或数据时所处的机器周期不同:取指周期取出的是指令;分析、取数或执行周期取出的是数据。

(2)取指令或数据时地址的来源不同:指令地址来源于程序计算器;数据地址来源于地址形成部件。

19. 根据连接方式不同,计算机系统采用的总线连接结构,有两种基本的类型,请比较单总线、多总线结构的性能特点?

1. 单总线结构:计算机的各个部件均由系统总线相连,在单总线结构中,CPU 与主存

之间、CPU 与 I/O 设备之间、I/O 设备与主存之间、各种设备之间都通过系统总线交换信息。

单总线结构的优点是控制简单方便,扩充方便。但由于所有设备部件均挂在单一总线上,

使这种结构只能分时工作,即同一时刻只能在两个设备之间传送数据,这就使系统总体数

据传输的效率和速度受到限制,这是单总线结构 的主要缺点。 (4 分)

2. 多总线结构:双总线结构又分为面向 CPU 的双总线结构和面向存储器的双总线结构。

面向 CPU 的双总线结构如下图所示。其中一组总线是 CPU 与主存储器之间进行信息交换的

公共通路,称为存储总线。另一组是 CPU 与 I/O 设备之间进行信息交换的公共通路,称为

输入/输出总线(I/O 总线)。

20.什么是总线周期、时钟周期、指令周期?它们之间一般有什么关系?

总线周期:存储器和I/O端口是挂接在总线上的,CPU对存储器和I/O接口的访问通过总线实现。把CPU通过总线对微处理器外部(存储器或I/O接口)进行一次访问所需时间称为一个总线周期。

总线周期一般包含4个总线时钟周期:

(1)T1状态 ——输出存储器地址或I/O地址。

(2)T2状态 ——输出控制信号。

(3)T3和Tw状态 ——总线操作持续,并检测READY以决定是否延长时序。

(4)T4状态 ——完成数据传送。

时钟周期:计算机中最小的时间单位,等于CPU主频的倒数。一个时钟周期内,cpu仅完成一个最基本的动作。

指令周期:从取指开始到执行完成该指令所需要的全部时间。指令周期包含若干机器周期。

关系:时钟周期 < 总线周期 < 指令周期

总线周期由若干个时钟周期组成,在8086CPU中,一个总线周期为4个时钟周期;

根据指令复杂程度的不同,指令周期由若干个总线周期组成。

21、说明总线结构对计算机系统性能的影响?

(1)最大存储容量:

单总线系统中,最大内存容量必须小于由计算机字长所决定的可能的地址总 线。双总线系统中,存储容量不会受到外围设备数量的影响。

(2)指令系统:

双总线系统,必须有专门的I/0指令系统单总线系统,访问内存和I/0使用相同指令。

(3)吞吐量:

总线数量越多,吞吐能力越大

22、计算机硬件有哪些部件?各部件的作用是什么?

计算机由运算器、控制器、存储器、输入设备和输出设备等五个逻辑部件组成。

1、运算器

运算器由算术逻辑单元(ALU)、累加器、状态寄存器、通用寄存器组等组成。算术逻辑运算单元(ALU)的基本功能为加、减、乘、除四则运算,与、或、非、异或等逻辑操作,以及移位、求补等操作。计算机运行时,运算器的操作和操作种类由控制器决定。

运算器处理的数据来自存储器;处理后的结果数据通常送回存储器,或暂时寄存在运算器中。与Control Unit共同组成了CPU的核心部分。

2、控制器

控制器,是整个计算机系统的控制中心,它指挥计算机各部分协调地工作,保证计算机按照预先规定的目标和步骤有条不紊地进行操作及处理。

硬件系统的核心是中央处理器(Central Processing Unit,简称 CPU)。它主要由控制器、运算器等组成,并采用大规模集成电路工艺制成的芯片,又称微处理器芯片。

3、存储器

存储器(Memory)是计算机系统中的记忆设备,用来存放程序和数据。

按用途存储器可分为主存储器(内存)和辅助存储器(外存),也有分为外部存储器和内部存储器的分类方法。外存通常是磁性介质或光盘等,能长期保存信息。内存指主板上的存储部件,用来存放当前正在执行的数据和程序,但仅用于暂时存放程序和数据,关闭电源或断电,数据会丢失。

4、输入设备

输入设备(Input Device)是人或外部与计算机进行交互的一种装置,用于把原始数据和处理这些数的程序输入到计算机中。

计算机能够接收各种各样的数据,既可以是数值型的数据,也可以是各种非数值型的数据,如图形、图像、声音等都可以通过不同类型的输入设备输入到计算机中,进行存储、处理和输出。

5、输出设备

输出设备(Output Device)是计算机的终端设备,用于接收计算机数据的输出显示、打印、声音、控制外围设备操作等。也是把各种计算结果数据或信息以数字、字符、图像、声音等形式表示出来。23.说明存储周期和存取时间的区别?

存储周期:连续启动两次读或写操作所需间隔的最小时间

存取时间,指的是CPU读或写内存内数据的过程时间。

存取周期和存取时间的主要区别是:存取时间仅为完成一次存取操作的时间,而存取周期不仅包含操作时间,还包含操作后线路的恢复时间。即:

存取周期 = 存取时间 + 恢复时间

24、某计算机的Cache-主存层次采用组相联映射方式,页面大小为128B,Cache容量为64页,按4页分组,主存容量为4096页,问:

(1)主存地址共需多少位?

(2)主存地址字段中主存字块标记,组地址标记和页内地址各需要多少位?

(1)4096=2¹²,主存地址需要12位。

- 组相联映射 标记 组号 页内地址

1 4 7

25、有一主存—Cache 结构的存储器,其主存容量1MB,Cache容量64KB,每块8KB,采用直接地址映射方式。

1.求主存地址格式

2.主存地址25301H问它映像在Cache的哪一个行/块?

26、磁盘组有6片磁盘,每片有二个记录面,存储区域内径22cm,外径33cm,道密度为40道/cm,内层位密度400位/cm,转速3600转/分,问:

(1)共有多少柱面?

(2)盘组总存储容量多少?

(3)数据传输率多少?

(1)有效存储区域=存储区域外半径−存储区域内半径,注,题目所给的内/外径为直径

存储区域外半径=33/2=16.5cm

存储区域内半径=22/2=11cm

故,有效存储区域=16.5-11 = 5.5cm

因为道密度为40道/cm,即半径上每cm就有40条磁道,

故一个盘面上的磁道数量为:

有效存储区域×道密度=5.5cm×40道/cm=220道,柱面数量即为磁道数量=220

(2)盘组容量=面数×一个盘面的磁道数×每个磁道的容量

可用存储信息的盘面数为:2×6

一个盘面的磁道数:220

每个磁道容量=磁道长度×对应位密度

因为题目所给的是内层位密度(当所给为外层位密度时也同理),故我们需要计算出内层的周长,易得为=2πR=2×3.14×11= 69.08cm

因此每条磁道容量=69.08cm×400bit/cm=3454B

可得一个盘面的存储容量=

一个盘面的磁道数×每个磁道的容量=3454B×220(由第一题得)= 759880B

一个盘组共有12个盘面,故总的容量=759880B×12=7598800B+2×759880B=9118560B

(3)磁盘数据传输速率Dr=rN

(N为每条磁道容量,N=3453B;r为磁盘转速,r=3600转/60秒=60转/秒)

所以Dr=60×3454B=207240B/s

27、用32K*8位的E2PROM芯片组成128K*16位的只读存储器,试问:

(1) 数据寄存器多少位?地址寄存器多少位?

(2) 共需多少个EPROM芯片?

(3) 画出此存储器组成框图

(1) 系统16位数据线,所以数据寄存器16位.

系统单元数位128K,所以系统地址=![]() 所以地址寄存器17位。

所以地址寄存器17位。

(2)所需芯片数![]() =8片。

=8片。

(3)存储器组成框图如下:

28.某计算机字长为32位,主存容量为64KB,采用单字长单地址指令,共有40条指令。试采用直接、立即、变址、相对四种寻址方式设计指令格式。

29、已知某机采用微程序控制方式,其控制存储器容量为512×48(位),微程序在整个控制存储器中实现转移,可控制的条件共4个,微指令采用水平型格式,后继微指令地址采用断定方式,如图所示:

| 操作控制字段 | 判别测试字段 | 下地址字段 |

(1)微指令中的三个字段分别应多少位?

(2)画出对应这种微指令格式的微程序控制器逻辑框图。

30、某机主存容量为4M×16位,且存储字长等于指令字长,若该机的指令系统具备97种操作。操作码位数固定,且具有直接、间接、立即、相对、基址五种寻址方式。

(1)画出一地址指令格式并指出各字段的作用;

(2)该指令直接寻址的最大范围(十进制表示);

(3)一次间址的寻址范围(十进制表示);

(4)相对寻址的位移量(十进制表示)

31、CPU结构如下图所示,其中有一个累加寄存器AC、一个状态条件寄存器和其他4个寄存器,各部件之间的连线表示数据通路,箭头表示信息传送方向。

(1)标明4个寄存器的名称。

(2)简述指令从主存取出送到控制器的数据通路。

[1] a 为数据缓冲寄存器 DR ;b 为指令寄存器 IR;

c 为主存地址寄存器 AR;d 为程序计数器 PC. (每个 1 分,共 4 分)

[2] 主存 M → 缓冲寄存器 DR →指令寄存器 IR →操作控制器。 (4 分)

32.如下图所示为双总线结构机器的数据通路,IR为指令寄存器,PC为程序计数器(具有自增功能),M 为主存(受 R/ W信号的控制),它既存放指令又存放数据,AR为地址寄存器,DR为数据寄存器,ALU为加、减控制信号决定完成何种操作, 控制信号 G控制的是一个门电路,它相当于两条总线之间的桥。另外, 线上标注有小圈表示有控制信号, 图中,yi表示 y 寄存器的输入控制信号, R1o为寄存器 R1的输出控制信号,未标字符的线为直通线,不受控制。

“SUB R2,R0”指令完成(R0)+(R2)→R0的功能操作,画出其指令周期流程图,假设该指令的地址已放入 PC 中,并列出相应的微操作控制信号序列。

33.设操作控制信号Ci的发出条件如下,写出Ci的逻辑表达式,并设计Ci的产生逻辑。

(1)在取指周期(M1机器周期)的T3节拍脉冲到来时发生。

(2)在指令Ia或Ib的指令周期的M2机器周期的T2节拍脉冲到来时发生。

(3)在指令Ic的指令周期的M3机器周期的T2节拍脉冲到来,且Bn有效时发生

5802

5802

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?