前言

操作系统利用一个或多个处理器的硬件资源,为系统用户提供一组服务,它还代表用户来管理辅助存储器的输入/输出(Input/Output,I/O)设备,因此,在开始分析操作系统之前,掌握一些底层的计算机系统硬件知识很重要。

1.基本构成

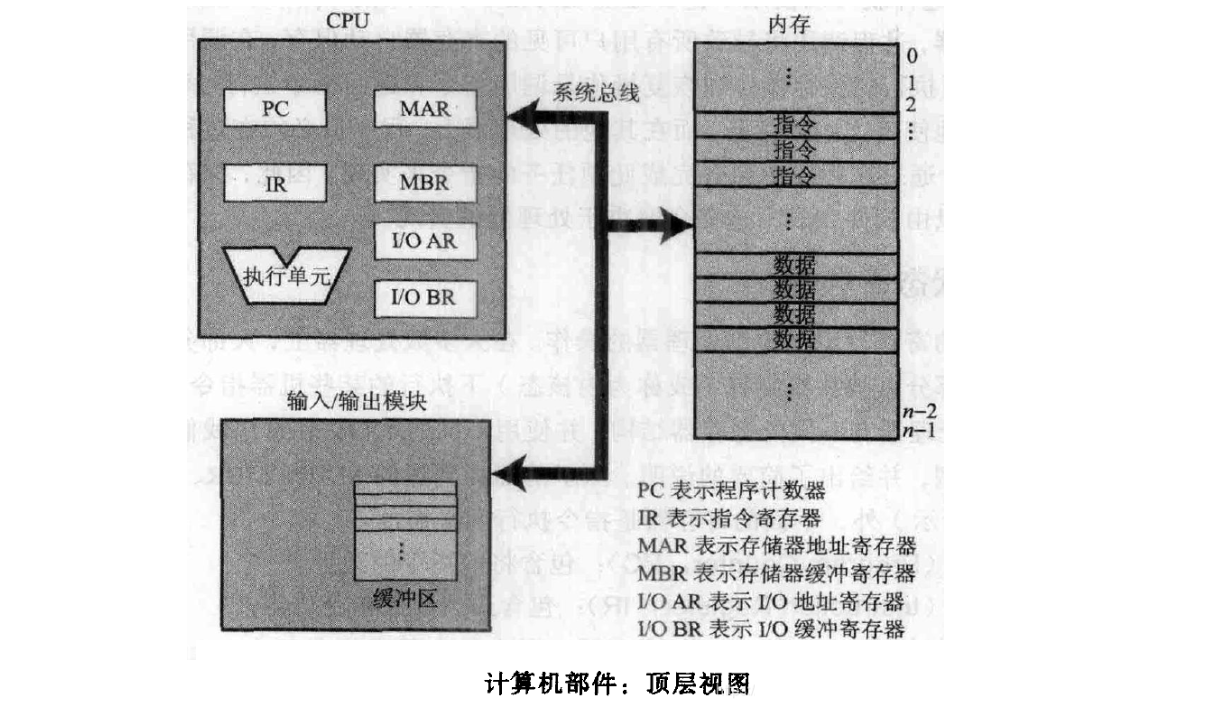

⭐计算机由处理器、存储器和输入/输出部件组成,每类部件都有一个或多个模块。这些部件以某种方式互连,以实现计算机执行程序的主要功能。因此,计算机有4个主要的结构化部件:

- 处理器(Processor) : 控制计算机的操作,执行数据处理功能。只有一个处理器时,它通常指中央处理器(CPU)

- 内存(Main memory):存储数据和程序。此类存储器通常是易失性的,即当计算机关机时,存储器的内容就会丢失,也就是断电易失。相对于此的是磁盘存储器,当计算机关机时,它的内容不会丢失。内存通常也称实存储器(real memory)或主存储器(primary memory)。

- 输入/输出模块(l/0 modules):在计算机和外部环境之间移动数据。外部环境由各种外部设备组成,包括辅助存储器设备(如硬盘)、通信设备和终端。

- 系统总线(System bus):在处理器、内存和输入/输出模块间提供通信的设施。

📖处理器的一种功能是与存储器交换数据。为此,它通常使用两个内部(对处理器而言)寄存器:

- 内存地址寄存器(Memory Address Register,MAR):用于确定下次读/写的存储器地址;

- 内存缓冲寄存器(Memory Buffer Register, MBR):用于存放要写入存储器的数据或从存储器中读取的数据。

【同理】

- 输入/输出地址寄存器(IO Address Register,简称IOAR或IO地址寄存器) :用于确定一个特定的输入/输出设备

- 输入/输出缓冲寄存器(IO Buffer Register,简称IOBR或I/0缓冲寄存器):用于在输入/输出模块和处理器间交换数据。

🍁内存模块由一组单元组成,这些单元由顺序编号的地址定义。每个单元包含一个二进制数,它可解释为一个指令或数据。输入/输出模块在外部设备与处理器和存储器之间传送数据。输入/输出模块包含内存缓冲区,用于临时保存数据,直到它们被发送出去。

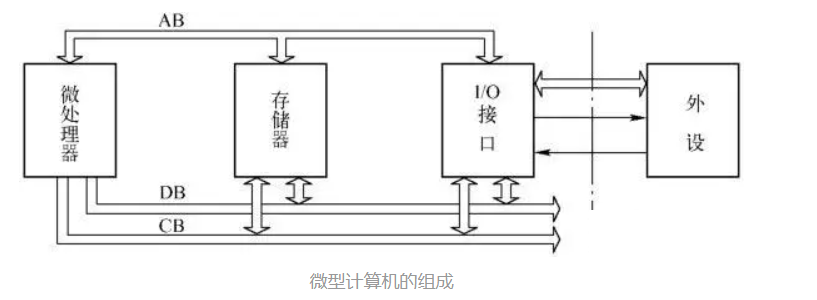

2.微处理器

微处理器(Micro Processing Unit,MPU):一种大规模集成电路器件,一般是以中央处理器CPU为核心,具有控制和运算功能,部分包含其它功能(如RAM、ROM等)的芯片。微处理器的特点是是微型、低功耗、主频低。

3.指令的执行

处理器执行的程序是由一组保存在存储器中的指令组成的。

最简单的指令处理包括两步:处理器首先从存储器中一次读(取)一条指令,然后执行每条指令。程序执行是由不断重复的取指令和执行指令的过程组成的,指态执行可能涉及很多操作,具体取决于指令本身。

单个指令所需要的外理称为一个指周期。我们可以使用两个简单的步骤来描述指令周期。这两个步骤分别称为取指阶段和执行阶段。仅当机器关机、发生某些未知错误或遇到与停机相关的程序指令时,程序执行才会停止。

-

每个指令周期开始时,处理器从存储器中取一条指令。在典型的处理器中,程序计数器(ProgramCounter,PC)保存下一次要取的指令地址。除非出现其他情况,否则处理器在每次取指令后总是递增PC,以便能按顺序取下一条指令(即位于下一个存储器地址的指令)。

-

取到的指令放在处理器的一个寄存器中,这个寄存器被称为指今寄存器(Instruction Register,IR)。指令中包含确定处理器将要执行的操作的位,处理器解释指令并执行对应的操作。大体上,这些动作可分为4类:

- 处理器—存储器:数据可以从处理器传送到存储器,或从存储器传送到处理器。

- 处理器—I/O:通过处理器和I/O模块间的数据传送,数据可以输出到外部设备,或从外部备向处理器输入数据。

- 数据处理:处理器可以执行很多与数据相关的算术操作或逻辑操作。

- 控制:某些指令可以改变执行顺序。例如,处理器从地址为149的存储单元中取出一条指令,该指令指定下一条指令应该从地址为182的存储单元中取,这样处理器就会把程序计数器置为182。因此在下一个取指阶段,将从地址为182的存储单元而非150的存储单元中取指令。

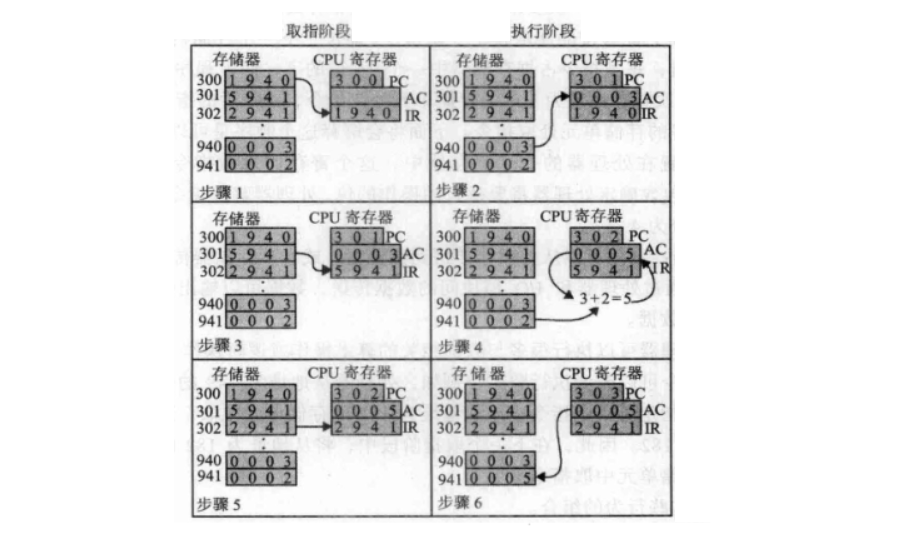

下图展示了程序的部分执行过程,显示了存储器和处理器的寄存器的相关部分。给出的程序片段把地址为940的存储单元中的内容与地址为941的存储单元中的内容相加,并将结果保存在后一个单元中。这需要三条指令,可用三个取指阶段和三个执行阶段描述:

-

PC中包含第一条指令的地址为300,该指令内容(值为十六进制数1940)被送入指令寄存器R中,PC增1。注意,此处理过程使用了存储器地址寄存器(MAR)和存储器缓冲寄存器(MBR)。为简单起见,这些中间寄存器没有显示。

-

R中最初的4位(第一-个十六进制数)表示需要加载AC,剩下的12位(后三个十六进制数)表示地址为940。

-

从地址为301的存储单元中取下一条指令( 5941 ),PC增1。

-

AC中以前的内容和地址为941的存储单元中的内容相加,结果保存在AC中。

-

从地址为302的存储单元中取下一条指令(2941 ),PC增1。

-

AC中的内容被存储在地址为941的存储单元中。

在这个例子中,为把地址为940的存储单元中的内容与地址为941的存储单元中的内容相加,一共需要三个指令周期,每个指令周期都包含一个取指阶段和一个执行阶段。如果使用更复杂的指令集合,则只需要更少的指令周期。大多数现代的处理器都具有包含多个地址的指令,因此指令周期可能涉及多次存储器访问。此外,除了存储器访问外,指令还可用于I/O操作。

4.IO模块

IO模块是指输入输出模块,它是计算机系统中用于处理输入和输出的一部分。在编程中,IO模块提供了一系列函数和类,用于读取和写入数据到外部设备或文件。

IO模块提供了多种方式来进行输入和输出操作,包括文件读写、网络通信、标准输入输出等。常用的IO函数和方法包括:

open()函数:用于打开文件,并返回一个文件对象,可以指定文件的打开模式(读取、写入、追加等)和编码方式。

read()方法:用于从文件中读取指定数量的字符或字节。

write()方法:用于向文件中写入指定的字符或字节。

close()方法:用于关闭文件。

seek()方法:用于移动文件指针到指定位置。

flush()方法:用于刷新缓冲区,将缓冲区中的数据立即写入到文件。

除了文件IO,Python的IO模块还提供了其他功能,如标准输入输出(sys.stdin、sys.stdout、sys.stderr)、内存IO(io.StringIO、io.BytesIO)等。

-

IO模块(例如磁盘控制器)可以直接与处理器交换数据。正如处理器可以通过指定存储单元的地址来启动对存储器的读和写一样,处理器也可以从IO模块中读数据或向IO模块中写数据。对于后一种情况,处理器需要指定被某一IO模块控制的具体设备。因此,指令序列的格式与图1.4中的格式类似,只是用IO指令代替了存储器访问指令。

-

在某些情况下,允许IO模块直接与内存发生数据交换,以减轻在完成IO任务过程中的处理器负担。此时,处理器允许I/O模块具有从存储器中读或往存储器中写的特权,这样IO模块与存储器之间的数据传送无需通过处理器完成。在这类传送过程中,IO模块对存储器发出读命令或写命令,从而免去了处理器负责数据交换的任务。这个操作称为直接内存存取(DirectMemory Access,DMA )

5.中断

事实上所有计算机都提供了允许其他模块(IO、存储器)中断处理器正常处理过程的机制。

中断最初是用于提高处理器效率的一种手段。

例如,大多数IO设备比处理器慢得多,假设处理器给一台打印机传送数据,在每一次写操作后,处理器必须暂停并保持空闲,直到打印机完成工作。暂停的时间长度可能相当于成百上千个不涉及存储器的指令周期。显然,这对于处理器的使用来说是非常浪费的。

| 中断的分类 | |

|---|---|

| 类别 | 说明 |

| 程序中断 | 在某些条件下由指令执行的结果产生,例如算术溢出、除数为0、试图执行一条非法的机器指令以及访问到用户不允许的存储器位置 |

| 时钟中断 | 由处理器内部的计时器产生,允许操作系统以一定规律执行函数 |

| I/O中断 | 由IO控制器产生,用于发信号通知一个操作的正常完成或各种错误条件 |

| 硬件故障中断 | 由诸如掉电或存储器奇偶错误之类的故障产生 |

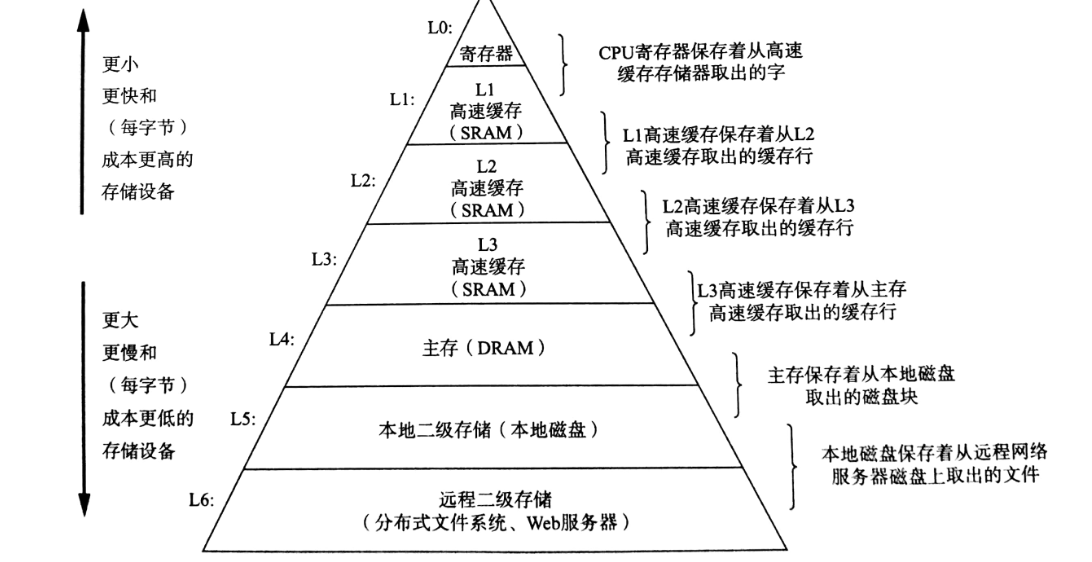

6.存储器的层次结构

计算机存储器的设计目标可以归纳成三个问题:多大的容量?多快的速度?多贵的价格?

- “多大的容量”的问题从某种意义上来说是无止境的,存储器有多大的容量,就可能开发出相应的应用程序使用它。

- “多快的速度”的问题相对易于回答,为达到最佳的性能,存储器的速度必须能够跟得上处理器的速度。换言之,当处理器正在执行指令时,我们不希望它会因为等待指令或操作数而暂停。

- 最后一个问题也必须考虑,对一个实际的计算机系统,存储器的价格与计算机其他部件的价格相比应该是合理的。

应该认识到,存储器的这三个重要特性间存在着一定的折衷,即容量、存取时间和价格。在任何时候,实现存储器系统会用到各种各样的技术,但各种技术之间往往存在着以下关系:

- 存取时间越快,每一个“位”的价格越高。

- 容量越大,每一个“位”的价格越低。

- 容量越大,存取速度越慢。

7.高速缓存

7.1 什么是高速缓存

在全部指令周期中,处理器在取指令时至少访问一次存储器,而且通常还要多次访问存储器用于取操作数或保存结果。处理器执行指令的速度显然受存储周期(从存储器中读一个字或写一个字到存储器中所花的时间)的限制。长期以来,由于处理器和内存的速度不匹配,这个限制已经成为很严重的问题。

7.2 高速缓存的原理

近年来,处理器速度的提高一直快于存储器访问速度的提高,这需要在速度、价格和大小之间进行折衷。理想情况下,内存的构造技术可以采用与处理器中的寄存器相同的构造技术,这样主存的存储周期才跟得上处理器周期。但这样成本太高,解决的方法是利用局部性原理( principle of locality ),即在处理器和内存之间提供一个容量小而速度快的存储器,称做高速缓存。

高速缓存试图使访问速度接近现有最快的存储器,同时保持价格便宜的大存储容量(以较为便宜的半导体存储器技术实现)。

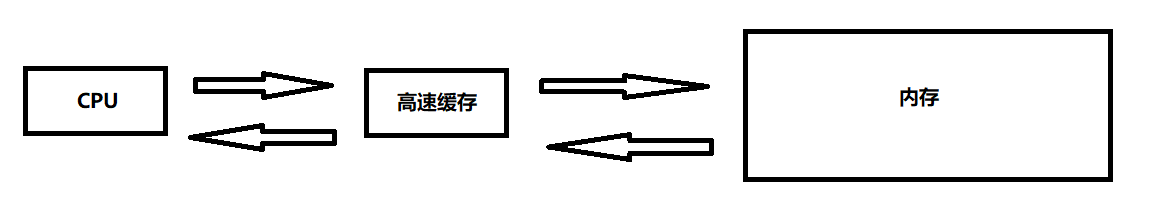

下图中有一个相对容量大而速度比较慢的内存和一个容量较小且速度较快的高速缓存,高速级存包含一部分内存数据的副本。

-

当处理器试图读取存储器中的一个字节或字时,要进行一次检查以确定这个字节或字是否在高速缓存中。

-

如果在,该字节或字从高速缓存传递给处理器

-

如果不在,则由固定数目的字节组成的一块内存数据先被读入高速缓存,然后该字节或字从高速缓存传递给处理器

由于访问局部性现象的存在,当一块数据被取入高速缓存以满足一次存储器访问时,很可能紧接着的多次访问的数据是该块中的其他字节。

516

516

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?