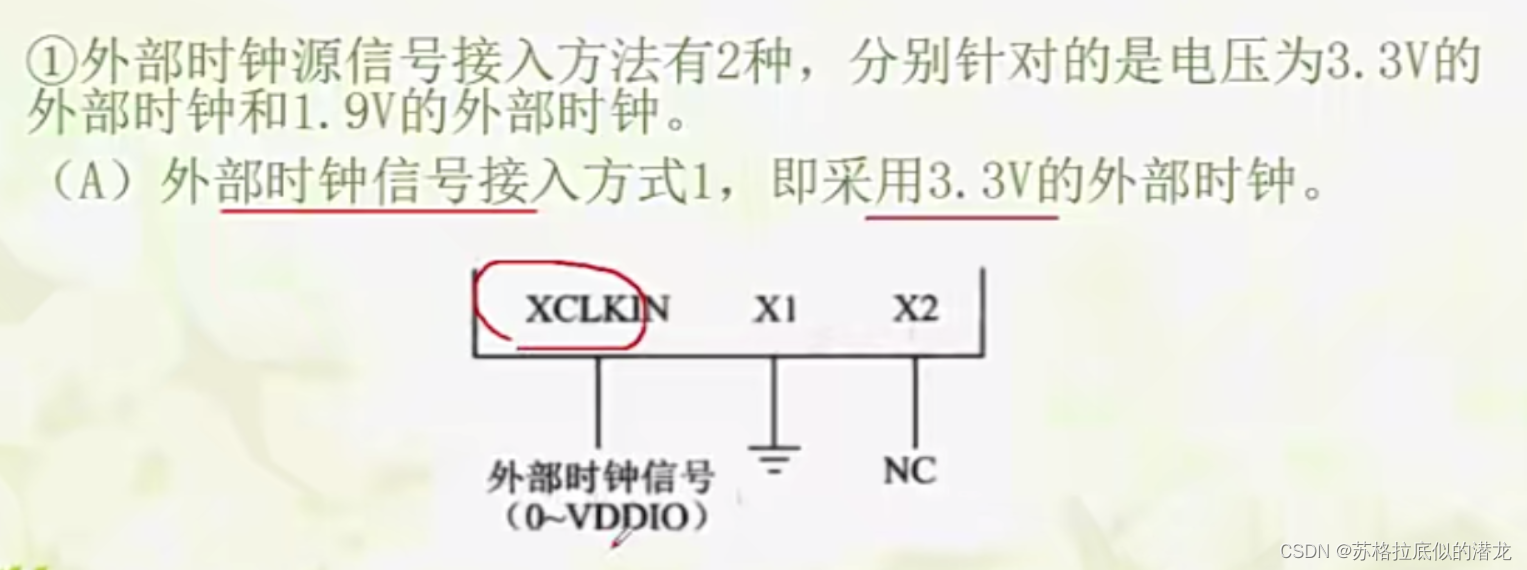

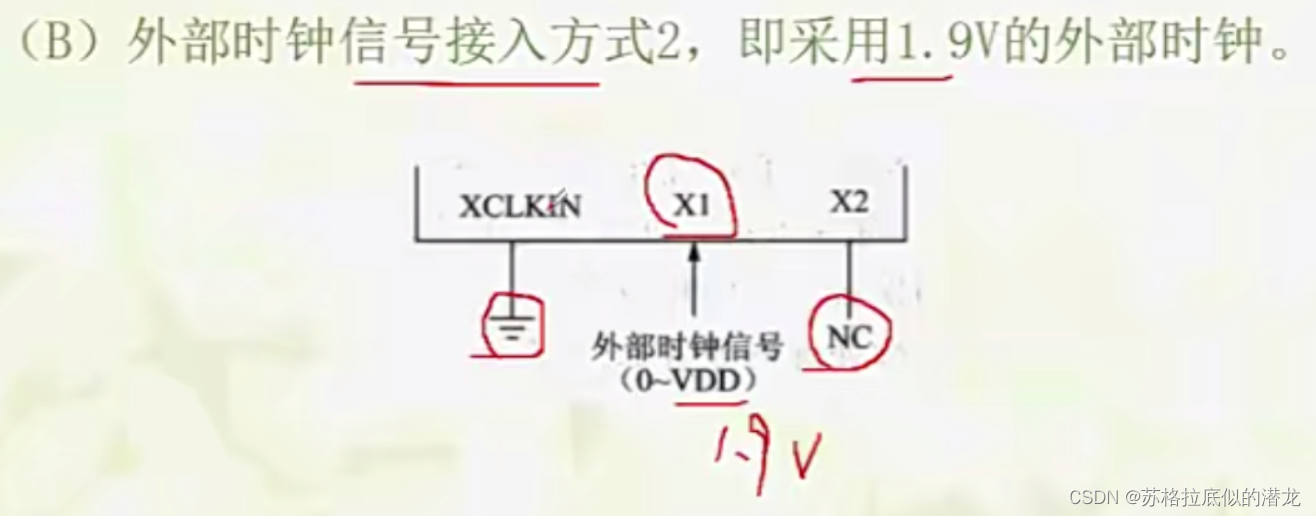

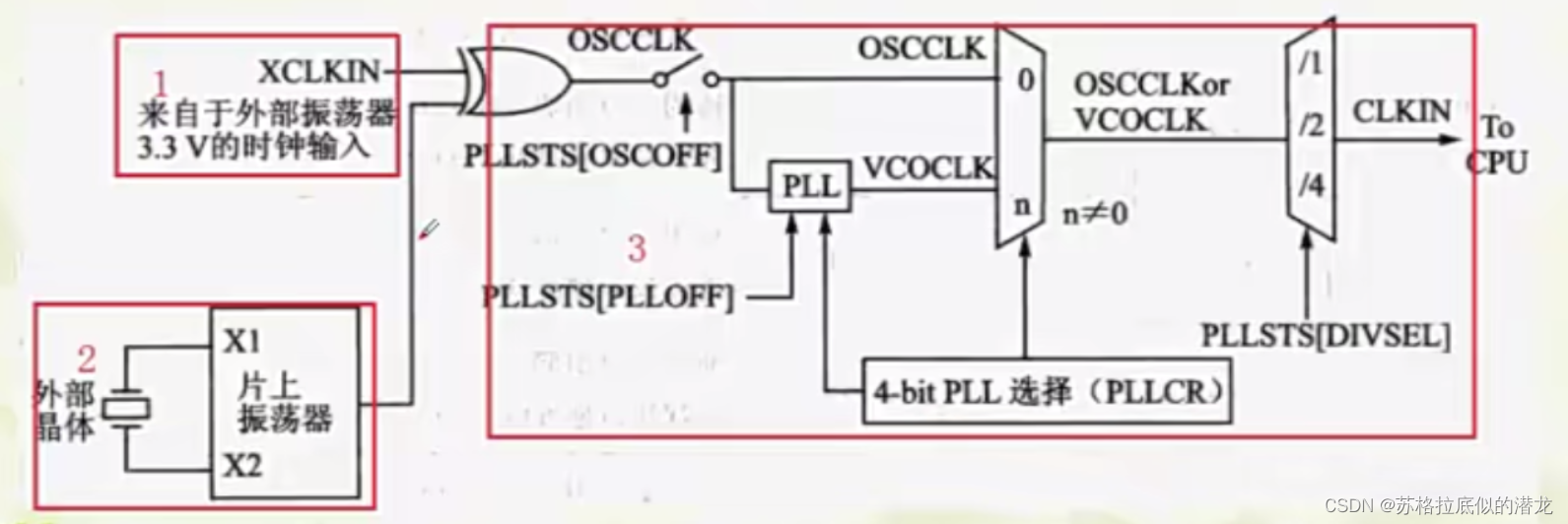

1)F28335时钟来源

2)自定义系统时钟

如果想要自定义系统时钟频率,只需要修改DSP28_DIVSEL和DSP28_PLLCR的数值

其中初始化时钟频率为30MHZ,DSP29_PLLCR为倍频,对时钟频率做乘法,DSP28_DIVSEL为分频,对时钟频率做除法。

TI公司提供的库文件DSP2833x_Example.h中,只需调节对应宏定义的打开和关闭即可

/*-----------------------------------------------------------------------------

Specify the PLL control register (PLLCR) and divide select (DIVSEL) value.

-----------------------------------------------------------------------------*/

//#define DSP28_DIVSEL 0 // Enable /4 for SYSCLKOUT

//#define DSP28_DIVSEL 1 // Disable /4 for SYSCKOUT

#define DSP28_DIVSEL 2 // Enable /2 for SYSCLKOUT

//#define DSP28_DIVSEL 3 // Enable /1 for SYSCLKOUT

#define DSP28_PLLCR 10

//#define DSP28_PLLCR 9

//#define DSP28_PLLCR 8

//#define DSP28_PLLCR 7

//#define DSP28_PLLCR 6

//#define DSP28_PLLCR 5

//#define DSP28_PLLCR 4

//#define DSP28_PLLCR 3

//#define DSP28_PLLCR 2

//#define DSP28_PLLCR 1

//#define DSP28_PLLCR 0 // PLL is bypassed in this mode

//----------------------------------------------------------------------------

2654

2654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?