指令集拓展

最小指令集合: RV32I, RV64I

根据功能需要选择对应的拓展,确保指令集的简洁。

基本概念

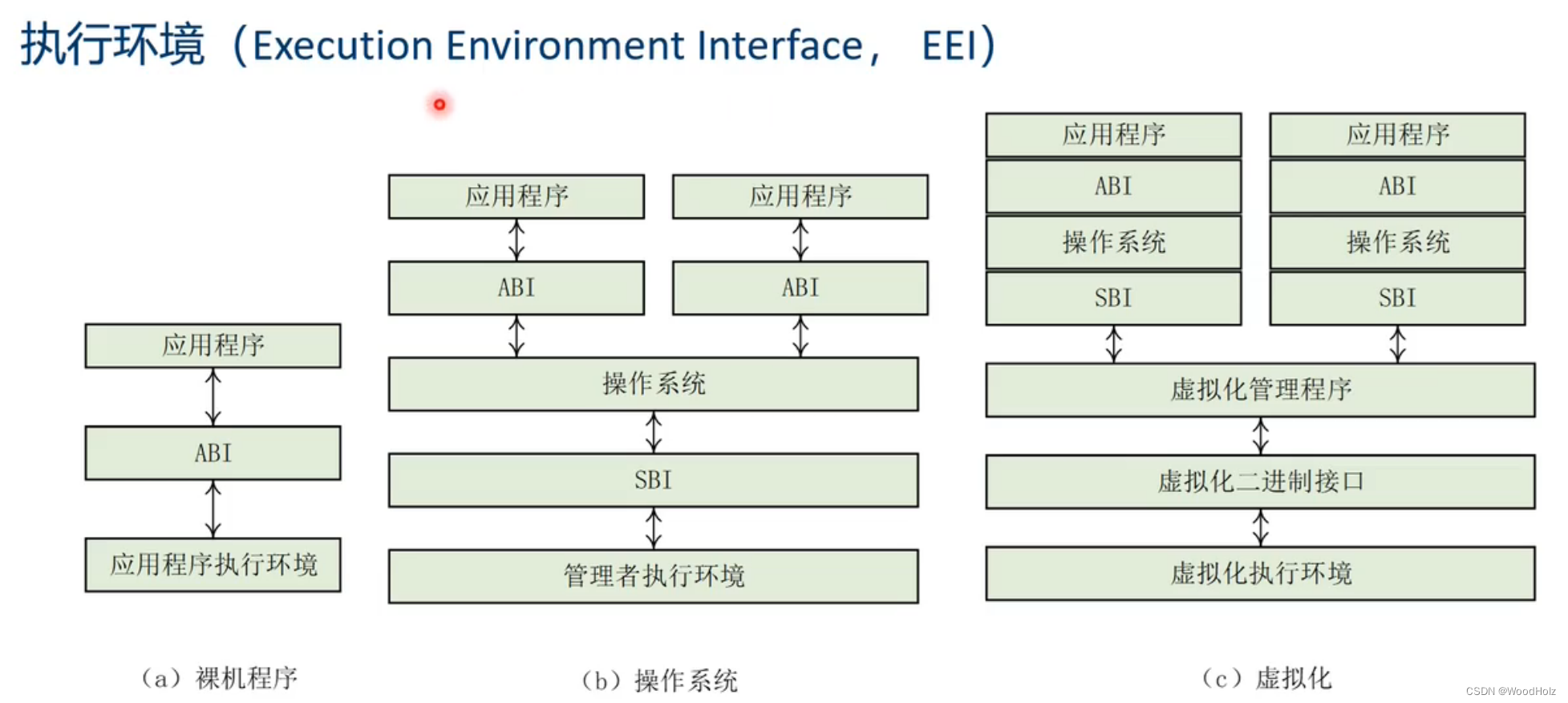

执行环境接口(EEI)

包括程序的初始状态、CPU的类型与数量、支持的S模式、内存和I/O的可访问性与属性、每个CPU上执行指令的行为以及异常的处理等

一个EEI可由纯硬件、纯软件或软硬件结合实现

哈特

表示一个CPU的执行线程。

近似于x86的SMT(超线程),Arm中的PE(处理机)

现目前市面上的处理器只需要了解一个物理核就一个执行线程(哈特),技术上并未实现超线程

处理器模式

- M 机器模式 SBI固件

- S 特权模式 OS内核

- U 用户模式

SBI服务

硬件共性功能的抽象。

就是对硬件的抽象和提供接口服务。类似于系统调用。

通用寄存器

| 通用寄存器 | 别名 | 特殊用途 |

|---|---|---|

| x0 | zero | 源寄存器/目标寄存器 |

| x1 | ra | 链接寄存器,保持函数返回地址 |

| x2 | sp | 栈帧寄存器,指向栈的地址 |

| x3 | gp | 全局寄存器,松弛链接优化 |

| x4 | tp | 线程寄存器,存放指向task_struct的指针 |

| x5~x7 | t0~t6 | 临时寄存器 |

| x8~x9 | s0~s11 | 函数调用如使用到需要保存到栈里;s0可作栈指针 |

| x10~x17 | a0~a7 | 函数调用时传递参数和返回值 |

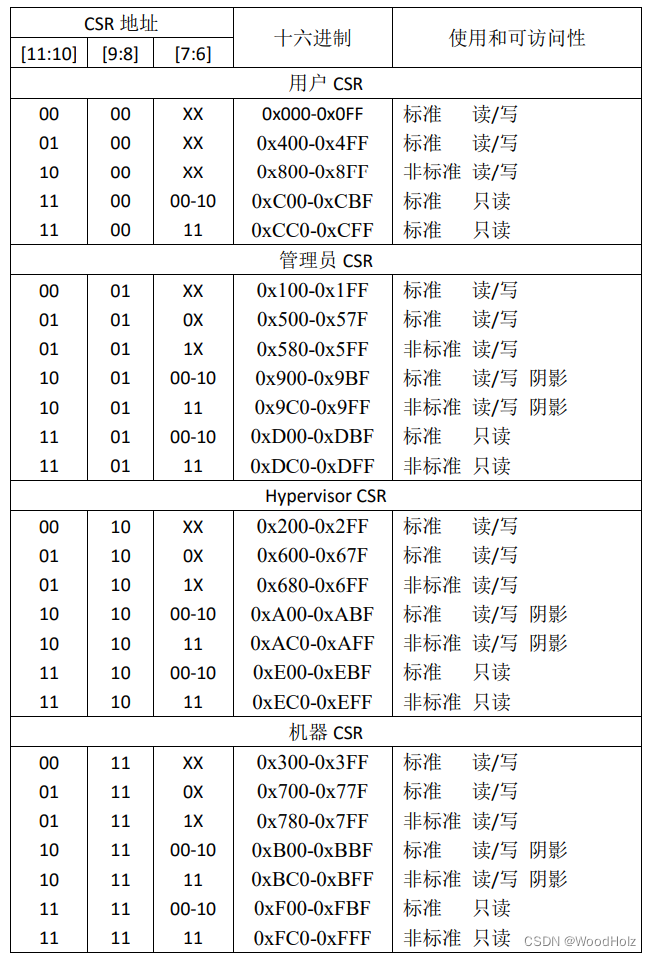

系统寄存器

- M模式的系统寄存器

- S模式的系统寄存器

- U模式的系统寄存器

通过CSR指令访问系统寄存器

触发非法指令异常的操作:

- 访问不存在/未实现

- 写入只读

- 越级访问

2200

2200

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?