一、什么是锁相环

锁相环(ohase-locked Loop,PLL):是一个能够比较输入输出相位差的反馈系统,利用外部输入的参考信号控制环路内部震荡信号的频率和相位,使同步至参考信号。使内部产生的信号和外部输入相位一样的信号

- 与我们平时所说的电路不一样,平时的电路反馈电流电压,而锁相环的输入输出都是相位,反馈的是相位差;

- 平时的电路以电压或者电流的变化为衡量稳定性的依据

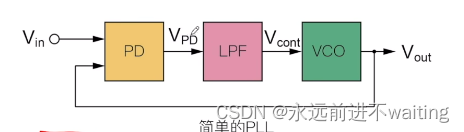

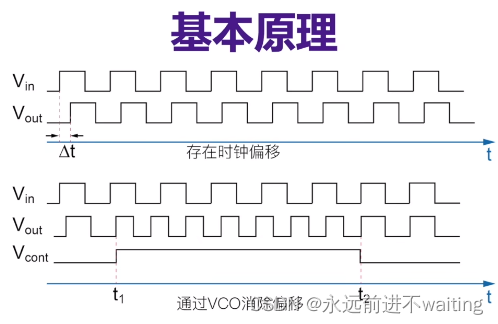

基本原理:

PD:鉴相器;LPF:低通滤波器;VCO:压控振荡器

Vin是输入信号的频率可以用晶振产生,如下图是非常标准的输入信号,而经过系统输出会产

生相位偏差,Vin和Vout进入鉴相器,如果有相位偏差,就会产生一个Vpd鉴定信号(有低频有高频),后面跟着VCO压控振荡器必须要稳定的故在之前加一个低通滤波器LPF,经过LPF滤波得到控制信号Vcont,会控制VCO震荡快一些追赶输入信号,当追赶上控制电压恢复原值。于是锁相环就是通过反复的鉴相和调整,最终VCO的输出信号频率和输入信号频率相位一致,这时PLL电路进入锁定状态。

二、主要应用

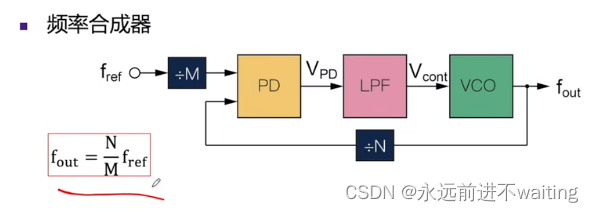

(一)频率合成器

如图所示的电路结构是在锁相环基本电路上的扩展,添加了两个分频器(除法运算代表分频、乘法运算代表倍频)于是得到,而通过调节N、M的值实现不同倍数的倍频或者分频,且两个信号的稳定性是一致的(eg.N=100,M=3)

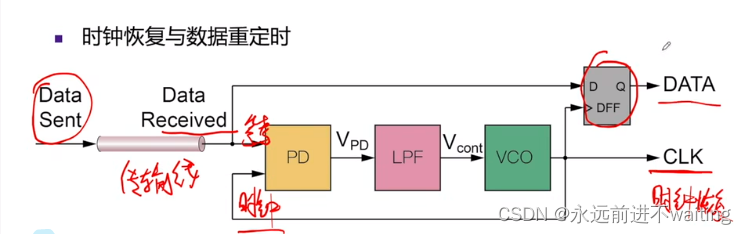

(二)时钟恢复与数据重定时

数据发送经过很长的一段数据线,其中数据可能与原始会有偏差(误码率),然后经过PLL电路产生一个与数据端数据频率和相位一样的时钟信号,然后在经过采样电路(触发器),从而达到降低误码率的效果。

(三)产生同一频率的时钟信号

我们需要不同的模块的内部时钟都能参考一个总的时钟来进行同步,从而避免两个模块内部时钟的差异而产生的数据传输的漂移等问题。

三、基本模块介绍

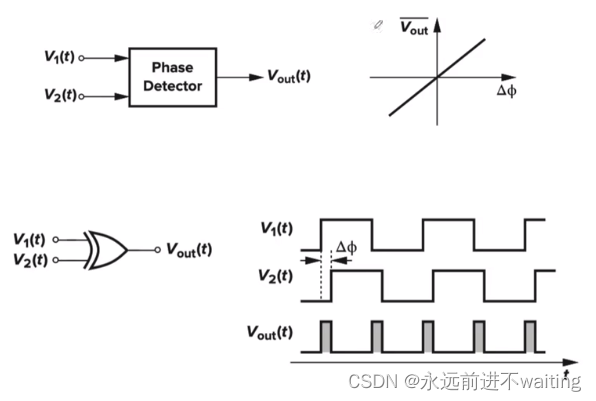

鉴相器PD(Phase Detector)

作用:检测两个信号的相位差,并将相位差转化为电压输出(转化曲线如右上所示为线性),能实现这一功能最基本的结构是异或门,电压相同逻辑低,电压不同逻辑高,这样逻辑高电压输出就是相位不同。(异或门直接输出的是脉冲信号,有高频成分和低频分量)

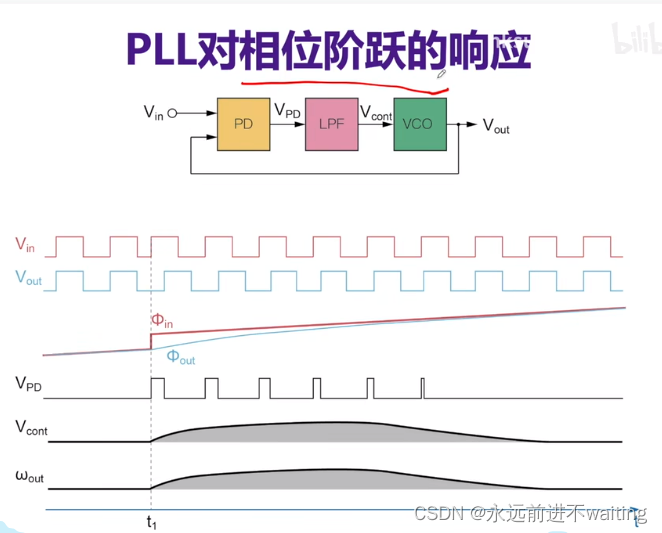

四、PLL对相位阶跃的响应

如果外界有一个噪声干扰对Vin产生影响,而实际对PLL有影响的是相位的阶跃,相位差一开始很大,故Vpd就开始逐渐增大,然后Vout开始追赶故w开始变大,当相位逐渐接近,相位差趋于0,此时二者减小趋于0,阶跃响应稳不稳定决定了其抗干扰能力。

6447

6447

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?