文档说明:

信息主要来源《IHI0050G_amba_chi_architecture_spec》

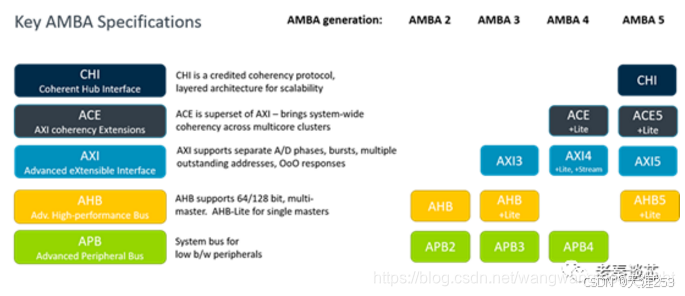

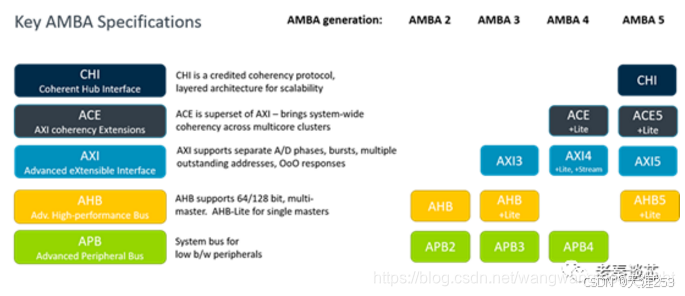

AMBA5出现了CHI(Coherent Hub Interface)协议,从名称看,hub比较显眼。CHI协议可以说是ACE协议的进化,一个重要的变化是将所有的信息传输采用包(packet)的形式来完成。反映在接口上,CHI与之前的ACE,AXI这些协议就完全不一样了。

1介绍

1.1架构概述

CHI架构是一个可伸缩的、连贯的集线器接口和由多个组件使用的片上互连。CHI体系结构允许组件连接的灵活拓扑结构,由性能、功率和区域系统需求驱动。

1.1.1组件

基于CHI的系统的组件可以包括:

独立处理器

处理器集群

图形处理器

内存控制器

I/O桥接

PCIe子系统互连

1.1.2关键功能

该体系结构的主要特性是:

•可扩展的体系结构,支持从小型系统扩展到大型系统的模块化设计。

•独立的分层方法,包括协议、网络和链路层,具有不同的功能。

•基于数据包的通信。

•由基于互连的主节点处理的所有事务,它可以协调所需的窥探、缓存和内存访问。

•CHI一致性协议支持:

-64字节缓存线的相干颗粒。

–Snoop过滤器和基于目录的系统,用于窥探比缩放。

–MESI和MOESI缓存模型,并从任何缓存状态转发数据。

–附加的部分的和空的高速缓存行状态。

•CHI事务集包括:

-允许性能、区域和高效系统缓存实现的丰富事务类型。

–支持互连中的原子操作和同步。

–支持高效执行独占访问的功能。

–交易,以有效地移动和放置数据,及时地将数据移动到更接近预期的使用点。

–通过分布式虚拟内存(DVM)操作进行–虚拟内存管理。

•请求重试以管理协议资源。

•支持端到端服务质量(QoS)。

•支持手臂内存标记扩展(MTE)。

•支持手臂领域管理扩展(RME)。

•可配置的数据宽度,以满足系统的要求。

•ARMTrustZone™是基于逐笔交易的支持。

•使用生产者-消费者排序模型优化了一致性写的事务流。

•错误报告和传播,跨组件和互连,以确保系统的可靠性和完整性。

•使用数据中毒和每字节错误指示处理子高速缓存线数据错误。组件接口上的

•电源感知信令:

-启用闪烁级时钟门控。

–为时钟门和电源门控制的组件激活和失活序列。

–协议对电源和时钟控制的活动指示。

1.1.3体系结构层

功能被分为以下几个层:

协议

网络

链接

| 层 | 通信粒度 | 主要功能 |

| 协议 |

Transaction

| 协议层是CHI架构中最顶层的一层。协议层的功能是: -在协议节点上生成和处理请求和响应。 –在包含缓存的协议节点上定义允许的缓存状态转换。 –为每个请求类型定义事务流。 –管理协议级流控制。 |

| 网络 |

Packet

| 网络层的功能是: -打包协议消息。 –确定通过互连将包路由到所需目的地并添加到包所需的源和目标节点id。 |

| 链接 |

Flit

| 链路层的功能是: -提供网络设备之间的流量控制。 –管理链路通道,以提供跨网络的无死锁切换。 |

1.2拓扑结构

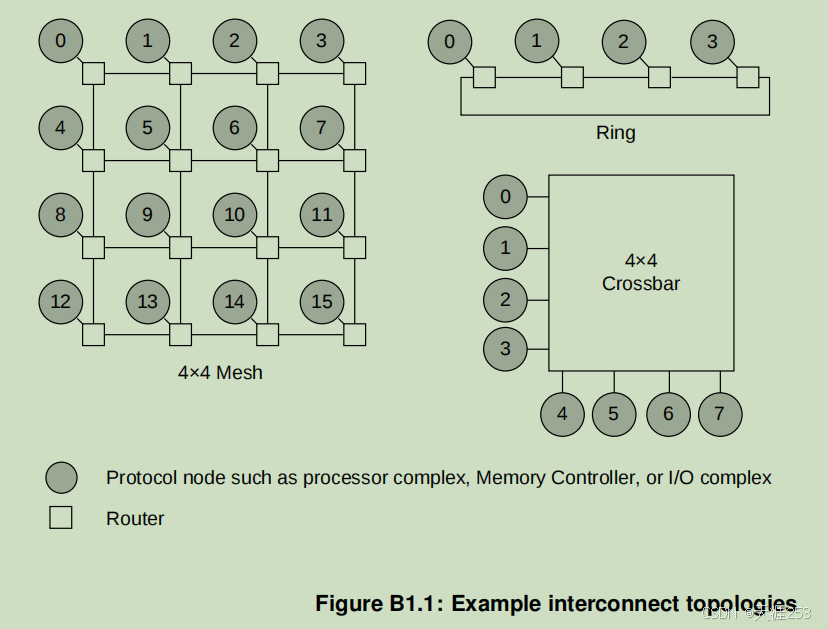

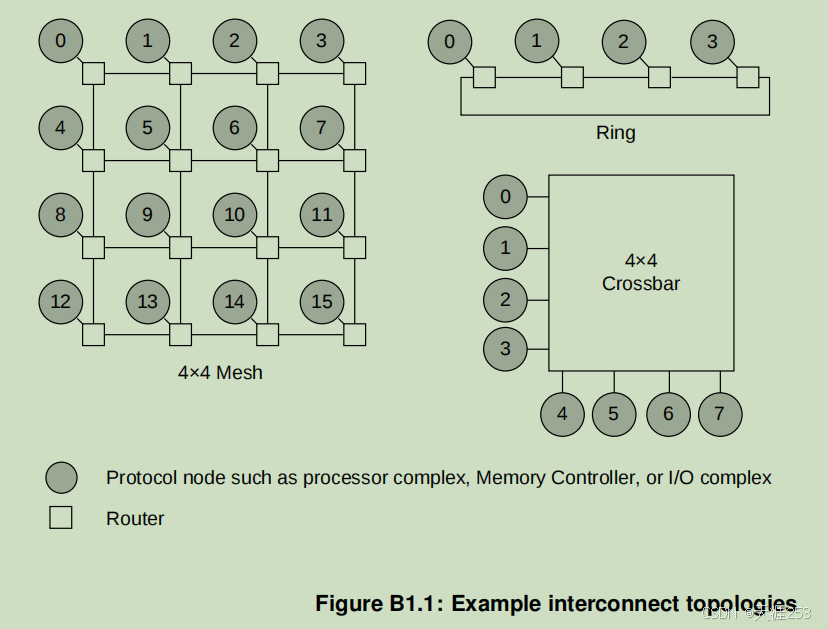

CHI体系结构主要是与拓扑无关的。然而,本规范中包含了某些与拓扑相关的优化,以使实现更高效。图B1.1显示了三个所选择的拓扑示例,以显示可用的互连带宽和可扩展性选项的范围。

Crossbar 横条拓扑构建起来很简单,并且自然地提供了一个具有低延迟的有序网络。横杆拓扑结 构适用于导线计数仍然相对较小的地方。横条拓扑适用于具有少量节点的互连。

Crossbar 横条拓扑构建起来很简单,并且自然地提供了一个具有低延迟的有序网络。横杆拓扑结 构适用于导线计数仍然相对较小的地方。横条拓扑适用于具有少量节点的互连。

Ring 环拓扑提供了一个在互连布线效率和延迟之间的权衡。延迟随环上节点的数量呈线性增加。环状拓扑结构适用于中等尺寸的互连件。

Mesh 网格拓扑以牺牲更多的电线为代价提供了更大的带宽。网格拓扑是非常模块化的,可以通过添加更多的开关行和列轻松地扩展到更大的系统。网格拓扑适用于更大规模的互连。

1.3术语

以下术语在本规范中具有特定的含义:

Transaction 事务执行一个操作。通常,事务要么从内存中读取,要么写入内存。

Message 消息是一个协议层术语,它定义了两个组件之间的交换颗粒。例如:请求,数据响应,Snoop请求。

一个单一的数据响应消息可以由多个数据包组成。

Packet 数据包是端点之间互连上的传输颗粒。一条消息可以由一个或多个数据包组成。例如,单个数据响应消息可以由1到4个数据包组成。每个数据包都包含路由信息,如目标ID和源ID,它们允许通过互连进行独立的路由。

Flit

FLow control unIT

(Flit)是最小的流量控制单元。一个数据包可以由一个或多个

Flits组成。给定数据包的所有点通过互连遵循相同的路径。注意:对于CHI,所有的数据包都由一个flit组成。

Phit

PHysical layer transfer unIT

(Phit)是两个相邻网络设备之间的一种传输。一个灯可以由一个或多个部分组成。注意:对于CHI,所有的

Flit都由一个phit组成。

PoS

Point of Serialization

(PoS) 是互连中的一个点,在这里确定了来自不同代理的请求之间的排序。

PoC

Point of Coherence

(PoC)是一个保证所有可以访问内存的代理都能看到内存位置的相同副本的点。在一个典型的基于chi的系统中,PoC是互连中的HN-F。

PoE

Point of Encryption

(PoE)是内存系统中任何已经达到该点的写操作都被加密的点。

PoP Point of Persistence

(PoP)是内存系统中相干点或之外的一个潜在点,在这里,当系统电源被删除时,保持对内存的写入,当电源恢复到内存中受影响的位置时,可靠地恢复。

PoDP Point of Deep Persistence (PoDP) 是内存系统中的一个点,即使电源和备用电池同时出现故障,数据也会被保存下来。

PoPA Point of Physical Aliasing (PoPA)是对一个物理地址空间(PAS)中的位置的更新对所有其他物理地址空间可见的点。

Downstream cache 从请求节点的角度定义了下游高速缓存。请求的下游缓存是请求使用CHI请求事务访问的缓存。请求节点可以发送带有数据的请求,以将数据分配到下游高速缓存中。

Requester 通过发出请求消息来启动事务处理的一种组件。术语“请求者”可用于独立启动事务的组件。术语“请求者”还可以用于独立发出下游请求消息的互连组件,或者作为系统中正在发生的其他事务的副作用。

Completer 响应从其他组件接收到的事务的任何组件。完成器可以是互连组件,如主节点或杂项节点,也可以是互连之外的组件,如从属组件。

Subordinate 接收事务并适当地完成事务的代理。通常,从属代理是系统中最下游的代理。从属者也可以被称为Completer 或者 Endpoint。

Endpoint 下属组件的另一个名称。端点是事务的最终目的地。

Protocol Credit 从交易完成者那里获得的能够接受交易的信用或担保。

Link layer Credit 在链接的另一边,一个flit将被接受的信用或保证。L-Credit是对链接层单跳的信用。

ICN Interconnect (ICN)是用于协议节点之间通信的CHI传输机制。互连可以包括在环、网格、横梁或其他拓扑中连接的交换机定义的实现结构。该互连还可以包括协议节点,如主节点和杂项节点。

IPA Intermediate Physical Address

(IPA). 在两阶段的地址转换中:

•阶段1提供了一个中间物理地址(IPA)。

•阶段2提供了物理地址(PA)。

RN Request Node (RN) 生成到互连的协议事务,包括读取和写操作。

HN Home Node (HN)是互连中的一个节点,它从请求节点接收协议事务,完成所需的一致性操作,并返回一个响应。

SN Subordinate Node (SN) 是从主节点接收请求、完成所需操作并返回响应的节点。

MN Miscellaneous or Misc Node (MN)是位于互连网络中的一个节点,该节点从请求节点接收DVM消息,完成所需的操作,并返回一个响应。

IO Coherent node 一个请求节点,除了不可窥探请求外,还生成可监听请求的子集。IO相干节点生成的可嗅请求不会导致接收到的数据缓存处于相干状态。因此,IO相干节点不接收任何Snoop请求。

Snoopee 正在接收窥探的请求节点。

Write-Invalidate protocol 一种协议,在该协议中,写入系统中共享缓存行的请求节点必须在继续写入之前使所有副本无效。CHI协议是一个写无效协议。

In a timely manner 该协议不能定义必须在其中发生某些事件的绝对时间。一个足够空闲的系统可以在没有明确的行动下进展和完成。

Inapplicable 一个字段值,表示在处理消息时未使用该字段。

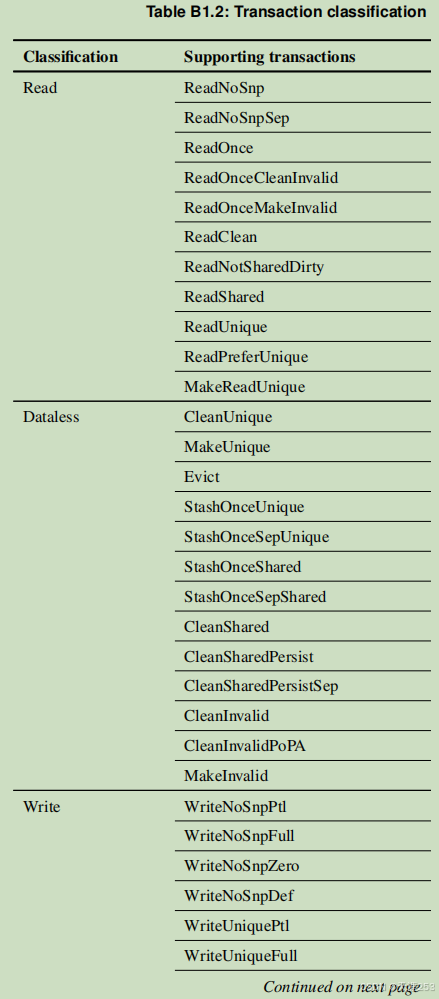

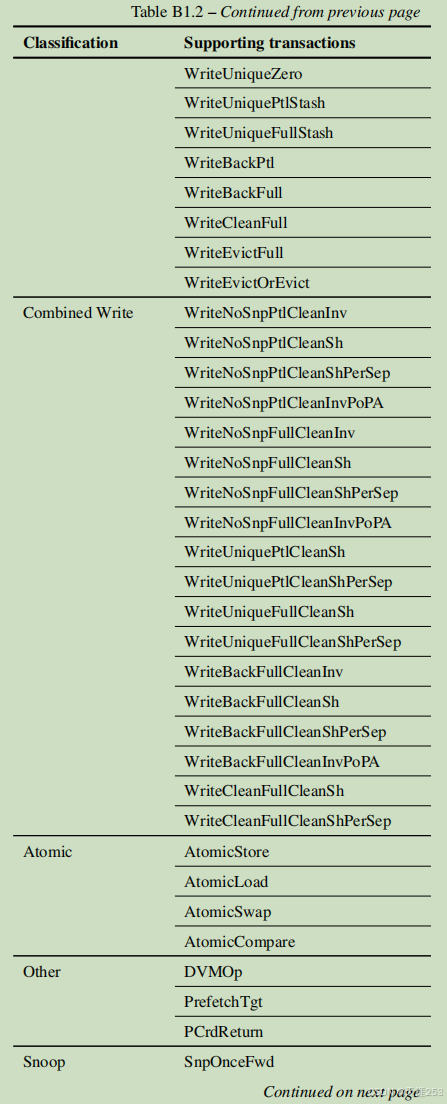

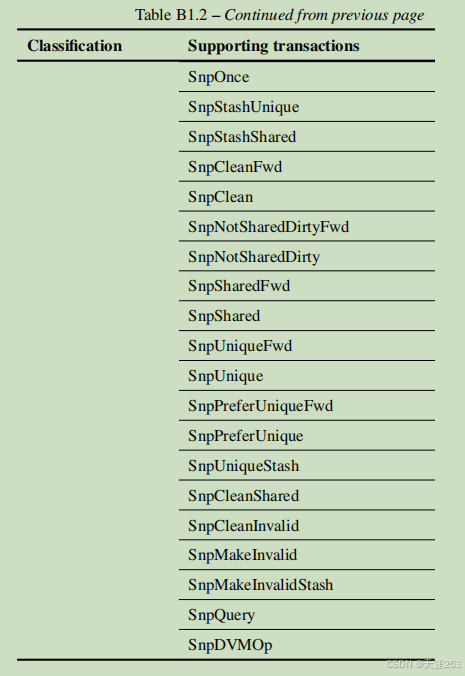

1.4交易分类

表B1.2中列出了本规范所支持的协议事务及其主要分类。

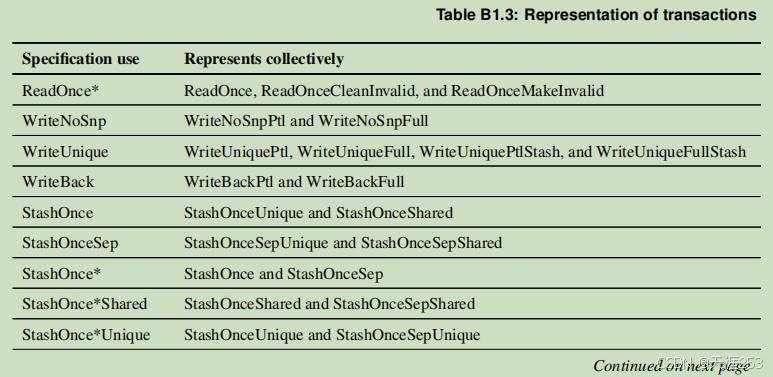

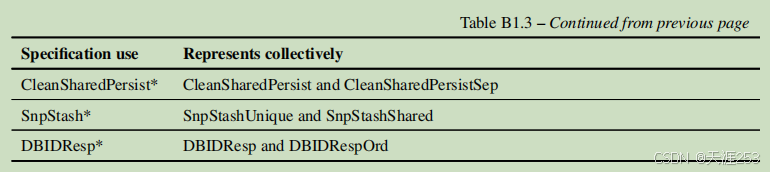

表B1.3显示了事务处理的表示形式。

1.5一致性概述

硬件一致性使系统组件能够共享内存,而不需要软件缓存维护来保持一致性。

如果两个组件以相同的顺序观察到,则内存区域是一致的。

1.5.1相干模型

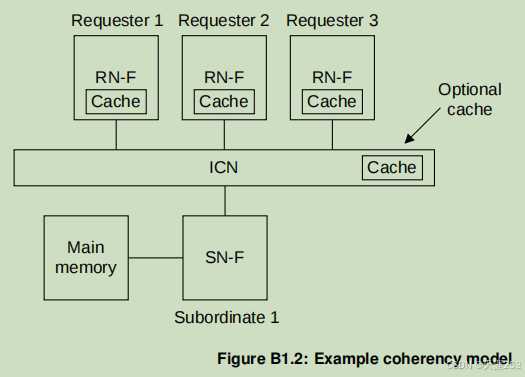

图B1.2显示了一个相干系统的示例,其中包括三个请求者组件,每个组件都有一个本地缓存和相干协议节点。该协议允许同一内存位置的缓存副本驻留在一个或多个请求程序组件的本地缓存中。

一致性协议强制要求,当存储出现在地址位置时,数据值不超过一个副本。一致性协议确保所有请求者在任何给定的地址位置观察正确的数据值。在每个存储到一个位置之后,其他请求者可以为他们自己的本地缓存获取数据的新副本,以允许多个缓存副本存在。

高速缓存线被定义为一个64字节对齐的内存区域。所有的一致性都保持在高速缓存线的粒度上。在内存位置的副本不再保存在任何缓存中。一致性协议不要求主内存始终是最新的。

注意:虽然不是要求,但允许在缓存的副本仍然存在时更新主存。

一致性协议使请求者组件能够确定缓存行是否是特定内存位置的唯一副本,或者是否存在相同位置的其他副本。一致性协议确保:

•如果缓存行是唯一的副本,则请求程序组件可以更改缓存行的值,而不通知系统中的任何其他请求程序组件。

•如果一个缓存行也可以出现在另一个缓存中,则请求程序组件必须使用适当的事务通知其他缓存。

1.5.2缓存状态模型

1.6组件命名

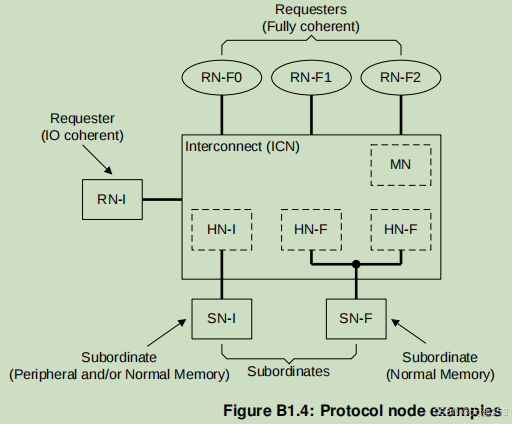

CHI协议中的组件按节点类型进行分类:

RN 请求节点。生成到互连的协议事务,包括读取和写操作。一个请求节点被进一步归类为:

RN-F 完全相干的请求节点:

-包括一个硬件相干的高速缓存。

–允许生成由协议定义的所有事务。

–支持所有的Snoop事务。

RN-D 具有支持DVM的IO相干请求节点:

—不包括硬件相干高速缓存。

–接收DVM交易。

–生成由协议定义的事务的子集。

RN-I IO相干请求节点:

-不包括硬件相干高速缓存。

–不接收DVM事务。

–生成由协议定义的事务的子集。

–不需要窥探功能。

HN Home节点。位于从请求节点接收协议事务的互连范围内的节点。主节点被进一步归类为:

HN-F 完全相干的主节点:

-期望接收除DVMOp之外的所有请求类型。

–包括一个一致性点(PoC),它通过监听所需的rn-f、合并事务的Snoop响应以及向请求的请求节点发送单个响应来管理一致性。

–应该是管理内存请求之间的顺序的序列化点(PoS)。

–可以包含一个目录或窥探过滤器来减少冗余的窥探。

注意:特定于实现的,可以包括一个集成的互连缓存。

HN-I 非一致性主节点:

-处理由协议定义的请求类型的有限子集。

–不包括PoC,也不能处理可提示的请求。在收到可提示的请求时,HN-I必须以符合协议要求的消息进行响应。

–应该是管理针对IO子系统的IO请求之间的订单的PoS。

MN 杂项节点。

从一个请求节点接收一个DVM事务处理,完成所需的操作,并返回一个响应。

SN 子节点。接收来自主节点的请求,完成所需的操作,并返回一个响应。一个下属节点被进一步分类为:

SN-F 从属节点。

–用于正常内存。

–可以处理不可窥取的读、写和原子请求,包括它们的排他变体,以及缓存维护操作(CMO)请求。

SN-I从属节点。

–用于外设或正常内存。

–可以处理不可窥取的读、写和原子请求,包括它们的排他变体,以及CMO请求。

图B1.4显示了通过互连连接的各种协议节点类型。

1.7读取数据源

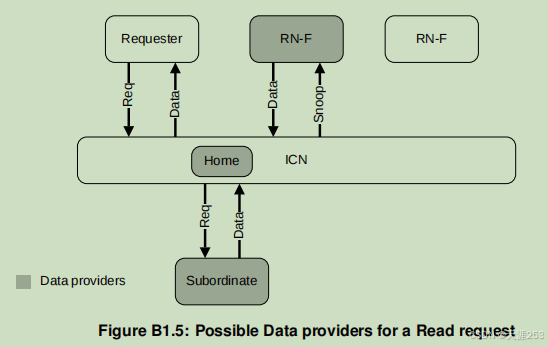

在基于chi的系统中,读取请求可以从不同的来源获取数据。图B1.5显示,这些源是:

• 互连中的高速缓存

• 下级节点

• 对应节点RN-F

Home的一个选项是请求RN-F或下属节点只返回数据到Home。Home依次将接收到的数据的副本转发给请求者。如果启用数据提供程序可以将数据响应直接转发给请求者,则可以删除在读取事务流中获取数据的跳点。

可以使用几种技术来减少完成事务的跳点数。跳数的减少导致节省了读和写延迟和互连带宽利用率。这些技术被分类为:

直接内存传输(DMT)定义了允许下级节点直接向请求者发送数据的特性。

直接缓存传输(DCT)定义了允许对等RN-F直接向请求者发送数据的功能。DCT读取事务流中的数据提供程序必须通知主页数据已发送给请求者。在某些情况下,数据提供程序还必须向家庭家庭发送一份数据副本。

直接写数据传输(DWT)定义了允许请求的请求节点直接向下级节点发送写数据的特性。

未完待续......

Crossbar 横条拓扑构建起来很简单,并且自然地提供了一个具有低延迟的有序网络。横杆拓扑结 构适用于导线计数仍然相对较小的地方。横条拓扑适用于具有少量节点的互连。

Crossbar 横条拓扑构建起来很简单,并且自然地提供了一个具有低延迟的有序网络。横杆拓扑结 构适用于导线计数仍然相对较小的地方。横条拓扑适用于具有少量节点的互连。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?