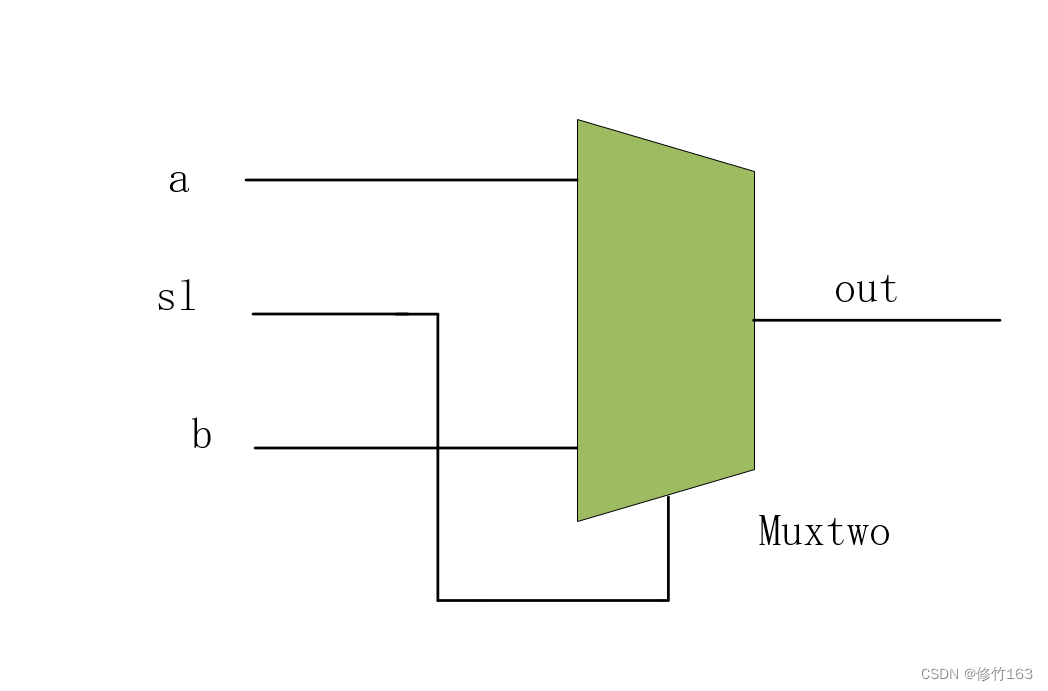

例子1:

二选一多路选择器的Verilog程序

module muxtwo(out,a,b,sl)

input a,b,sl;

output out;

reg out;

always@(sl or a or b)

if (! sl) out = a;

else out = b;

endmodule

结合多路选择器的电路结构我们来分析一下代码。输出out是a还是b取决于sl是高电平还是低电平当控制信号的sl为非(低电平0)时out输出为a否则为b,always@(sl or a or b)表示只要信号sl,a,b只要其中之一发生变化就执行后面的if语句。

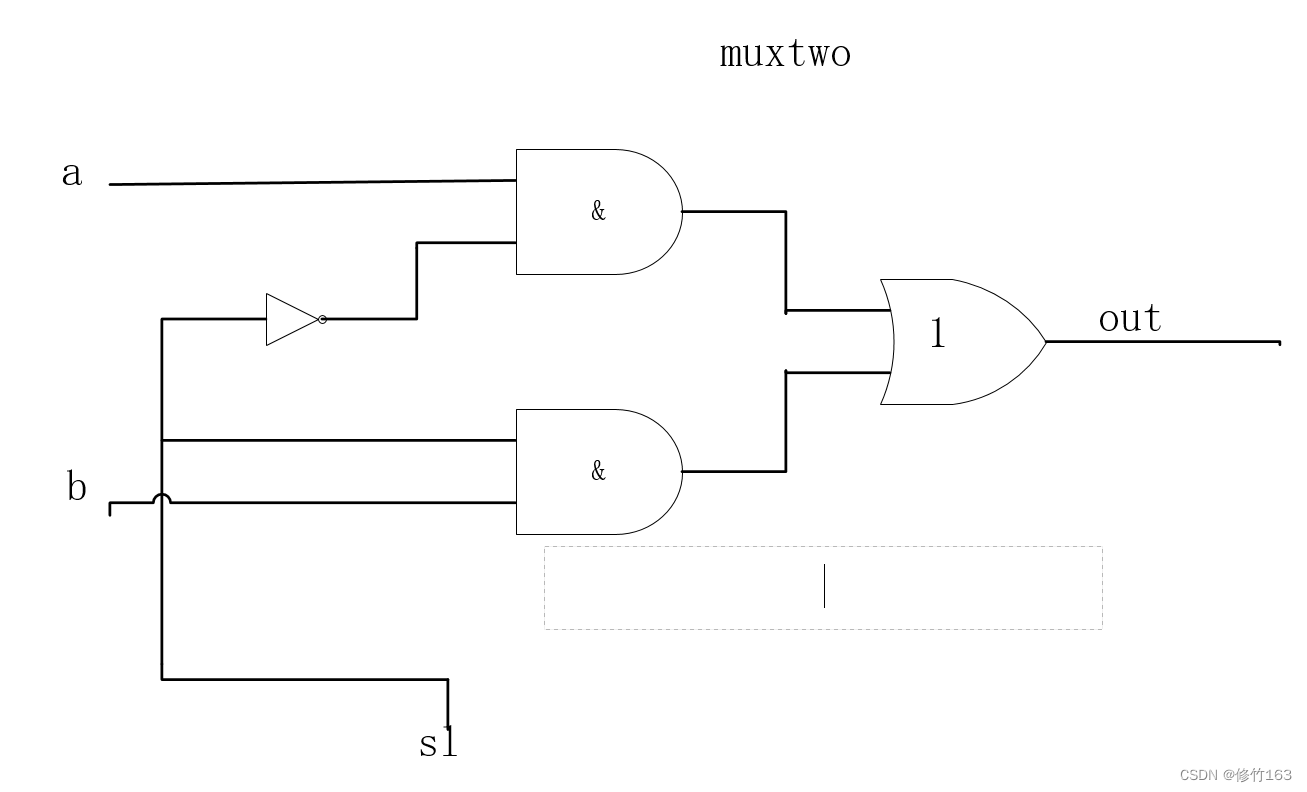

例2:用带有与非门的二选一多路选择器的Verilog HDL程序描述。

现在我们用verilog语言来描述这个电路:

module muxtwo(out,sl,a,b)

input a,b,sl; //输入信号名

output out; //输出信号名

wire nsl,sela,selb; //定义内部连线

assign nsl =~ sl ; //求反

assign sela = a&nsl ; //按位与运算

assign selb = b&nsl;

assign out = sela | selb;

endmodule 非常容易理解代码就是按照逻辑运算描述了电路结构。

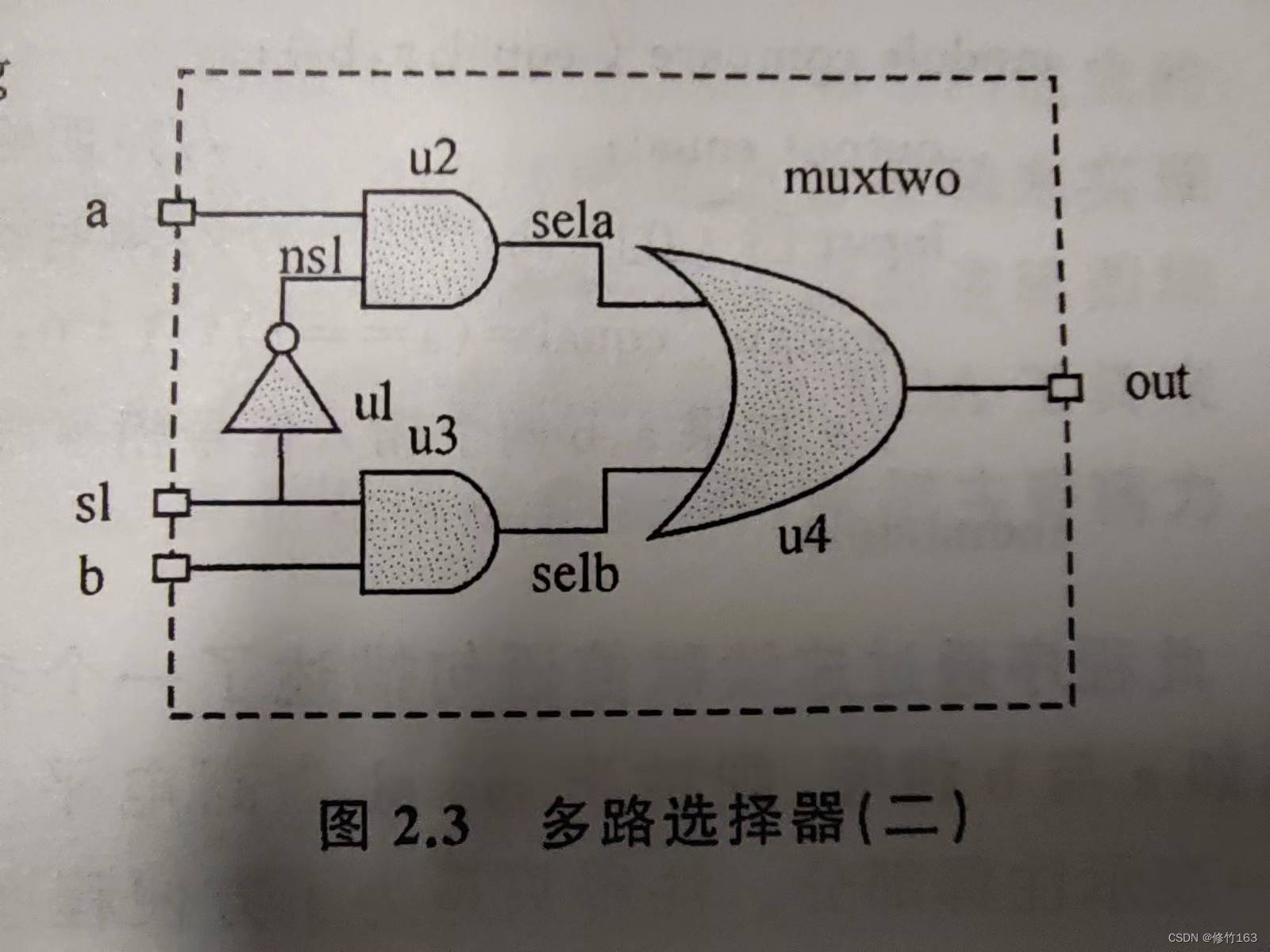

例3

我们用代码来描述这个电路。

module muxtwo(out,sl,a,b);

input sl,a,b;

output out;

not u1(nsl,sl);

and #1 u2(sela,a,nsl);

and #1 u3(selb,sl,b);

or #1 u4(out,sela,selb);

endmodule对程序解释说明

#1,#2表示门输入到门输出的延迟时间为1或2各单位。

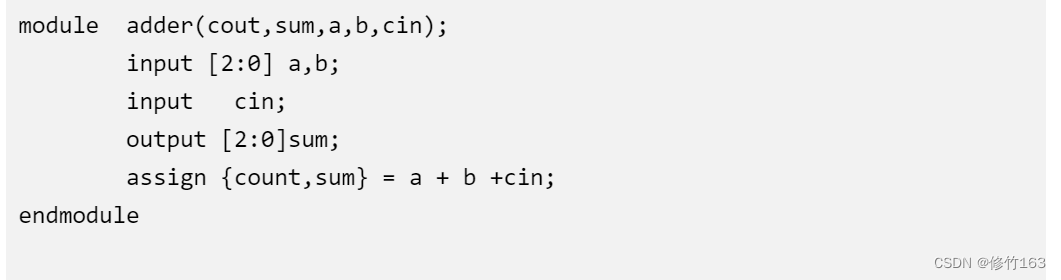

例4,通过连续赋值语句描述一个3位加法器的Veriog程序。

通过连续赋值语句描述了一个名为adder的三位加法器。它可以根据两个二比特数a,b 和进位(cin)计算出和(sum)以及上进位(cout).

能完成一个功能的模块封装在module和endmodule之间。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?