龙芯已经准备了一系列配套的实验供我们学习

截止2024年11月,共有23个实验包,能帮助我们从熟悉vivado和龙芯试验平台到添加Cache为止。实际上,完成实验的过程也是设计cpu的基本步骤,即完成了这23个实验你也就得到了一款五/六级流水并且具备MMU和cache的完整cpu核心。在这之后还需要完成对cpu的ipc(cpu每秒运行指令数)提升的漫长之路。

接下来我们将从lab1(实验1)开始熟悉vivado和龙芯试验平台开始

lab1是一个控制龙芯实验箱上led灯实现跑马灯的工程

非常适合作为入门学习实践:

当

当

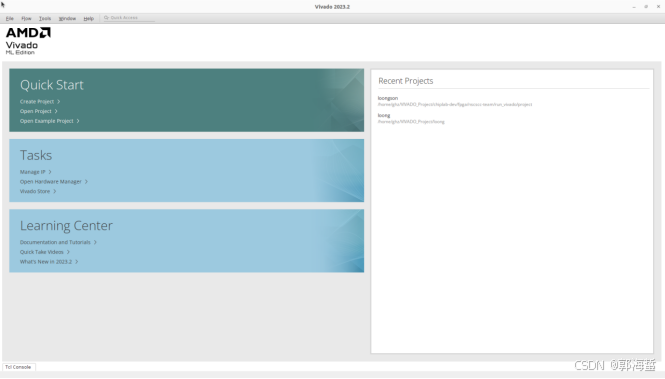

当你完成vivado2023.2的安装打开它后会看到这样的界面

Quick Start部分能帮助你快速创建或者打开工程

Task部分能帮助你管理IP核以及完成硬件设备的管理等任务

在右侧你可以看到最近的工程并能快速打开

接下来我们新建一个工程:

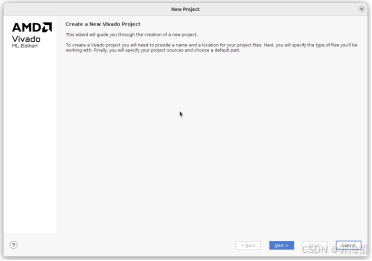

首先点击Quick Start选项卡下的Create Project

接着点击next

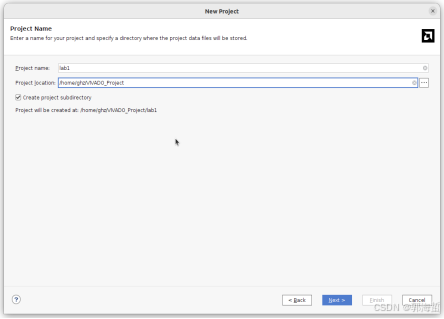

输入你的项目名称并选择保存路径后点击next

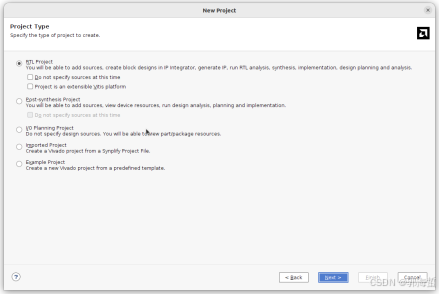

在此选择工程类型:

1. RTL Project

- 这是最常用的完整设计工程类型

- 你可以添加源文件,在IP集成器中创建框图设计

- 可以进行RTL分析、综合、实现和时序分析等完整的设计流程

- 适合从头开始的FPGA设计项目

- Post-synthesis Project(后综合工程)

- 用于导入已经综合过的网表

- 可以查看器件资源使用情况

- 可以进行布局布线和实现

- 适合只需要做后端实现的项目

- I/O Planning Project(I/O规划工程)

- 专注于管脚分配的规划

- 只能查看器件封装和I/O资源

- 不能添加设计源文件

- 适合前期只做管脚规划的工作

- Imported Project(导入工程)

- 用于导入从Synplify等其他工具生成的工程

- 将其他工具的工程转换为Vivado工程

- Example Project(示例工程)

- 基于预定义模板创建新工程

- 包含了一些基础设计实例

这里我们选择RTL project然后点击NEXT

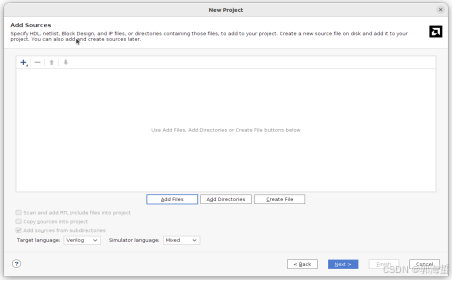

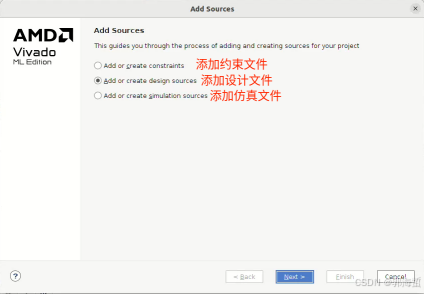

在此界面中你可以添加已有的文件或创建新的文件,为了演示在工程中添加文件,此处我们直接点击NEXT

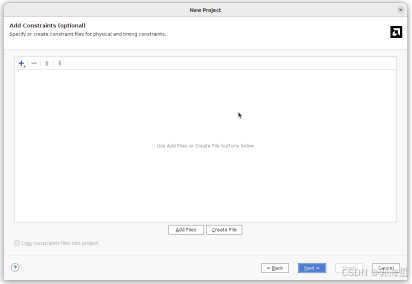

接下来要求我们添加约束文件

我们先来简单认识一下约束文件:

XDC文件是基于Tcl(一种脚本语言) 编写的文本文件,用于约束FPGA设计中的时序、管脚、IO标准等。常见的XDC文件内容包括:

- 时序约束:例如时钟周期、输入和输出延迟等,以确保设计的时序正确

- 物理约束:例如管脚分配,用于指定FPGA引脚与设计信号之间的映射

- IO标准约束:设置引脚的电气特性(如电压标准)

此处我们依然直接点击NEXT

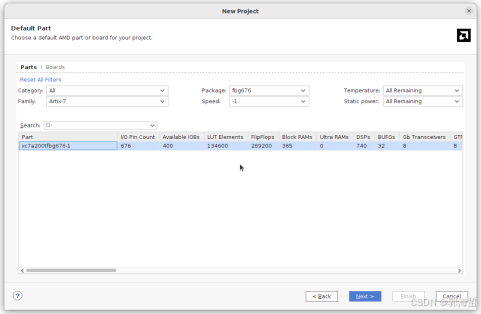

龙芯实验平台使用Airtx-7 XC7A200T-FBG676芯片

按照上图选择好芯片型号后点击NEXT

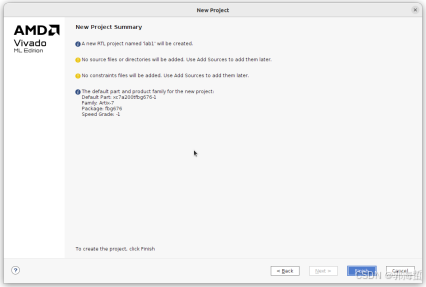

在这个界面中vivado会对先前的选择进行汇总

此处的两个warning是在提醒我们没有选择源文件与约束文件

点击Finish即可完成工程的创建

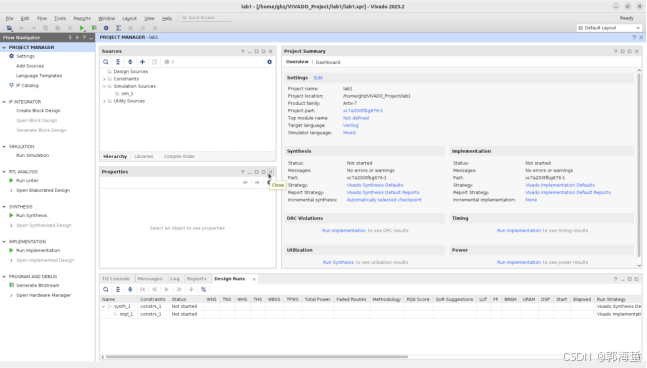

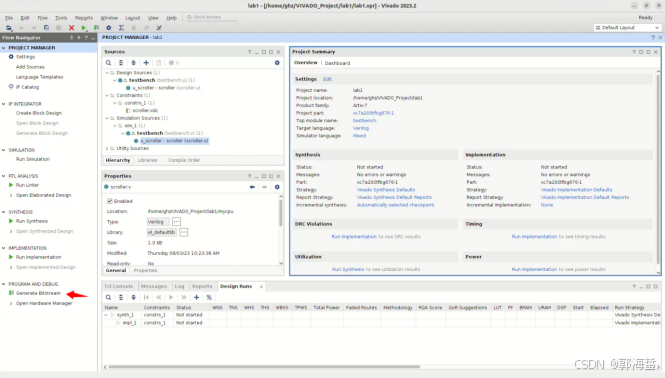

在vivado的主界面中:

左侧导航栏 - Flow Navigator

- PROJECT MANAGER:项目管理,源文件添加与设置

- IP CATALOG:IP核目录,用于添加和管理IP核

- IP INTEGRATOR:IP集成器,用于创建框图设计

- SIMULATION:仿真功能区

- RTL ANALYSIS:RTL分析工具

- SYNTHESIS:综合工具

- IMPLEMENTATION:实现工具

- PROGRAM AND DEBUG:程序下载和调试

- 中央区域 - Sources/Properties窗口

- Sources:显示项目中的所有源文件

- Design Sources:设计源文件

- Constraints:约束文件

- Simulation Sources:仿真文件

- Properties:显示选中对象的属性

- 右侧区域 - Project Summary

- 显示项目概况信息

- 包含项目设置、综合状态、实现状态等

- 显示器件利用率、时序违例、功耗等信息

- 底部区域 - Console/Messages

- Tcl Console:命令行界面

- Messages:显示各类信息、警告和错误

- Log:日志信息

- Reports:各类报告

- Design Runs:设计运行状态

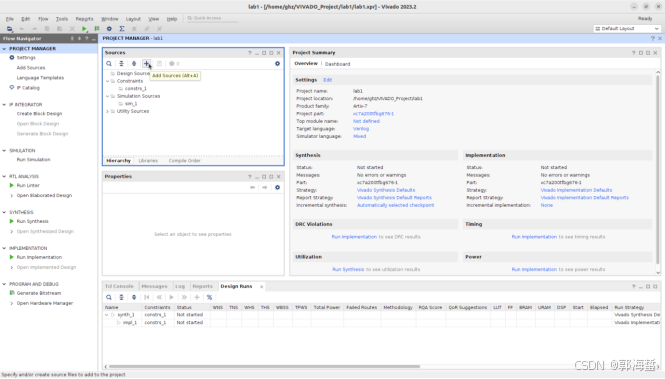

接下来我们将添加lab1中为我们提供的约束文件(.xdc)和源文件(.v)

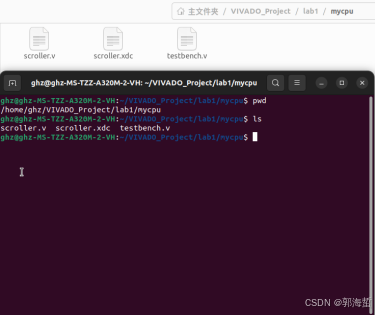

为了工程文件的规整,我们建议你将本工程用到的所有文件都存放在同一个父文件夹下(此处为lab1)然后点击Source区域中的+号添加文件

——————————————————————————————————————————

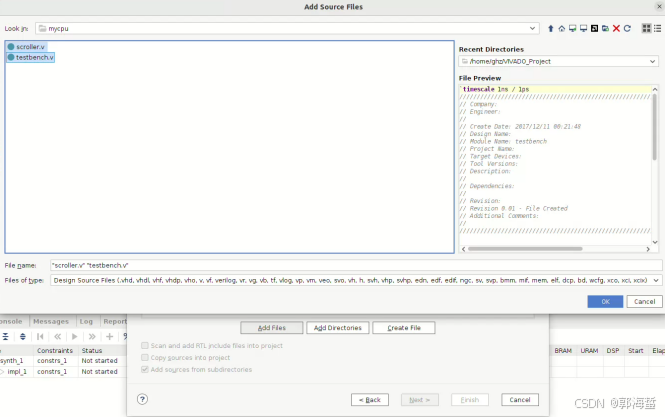

接着选择添加源设计文件

接着在出现的窗口中点击Add Files添加.v文件(此处包括源设计文件scroller.v和仿真文件testbench.v)

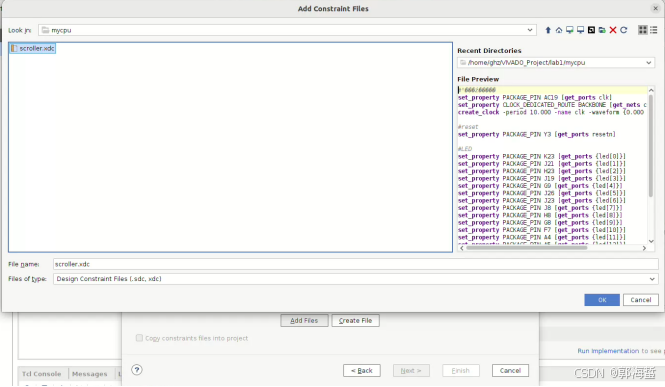

如法泡制,添加约束文件

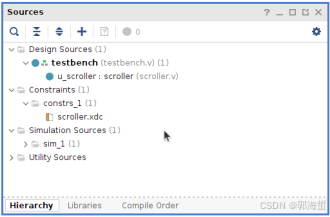

现在我们就可以在Source窗口中看到我们添加的文件了

此时你就可以编辑这些文件了,但vivado自带的编辑器不具备一些常用的功能,建议将编辑器替换为vscode或其他ide,具体方法请自行查找

在往后的教程中将默认在Ubuntu 22.4环境下使用vscode进行演示

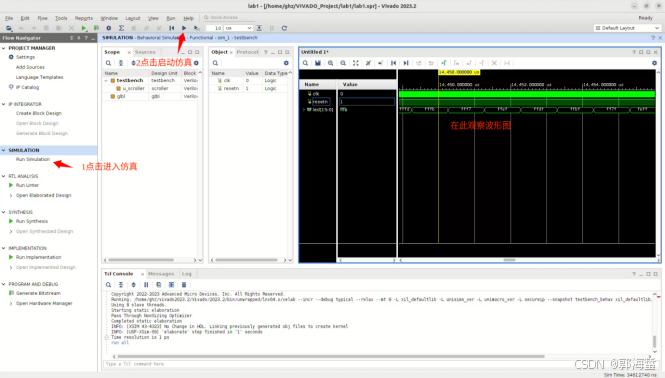

接着进入仿真

可以看到信号在规律变化

仿真无误后点击此处生成比特流文件

生成比特流文件后在硬件管理器中选择对应芯片烧录即可在龙芯试验平台上看到对应的跑马灯效果了

本章为大家梳理了vivado的工程创建,并明确了工程中基本的三种文件:源工程文件(.v) 约束文件(.xdc) 测试文件(.v)

在顺利通过仿真以及上板确认无误后,请梳理lab1中源工程文件 约束文件 以及测试文件的源代码。形式包括但不限于增加注释 绘制思维图等,并配合各种人工智能助手完成对tcl语法/verilog语法的熟悉以及对仿真流程的贯通。

2420

2420

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?