实验代码

module LED_Shumaguang (clk, led);

input clk;

reg[6:0] led;

output[6:0] led;

integer p;

reg clk_1Hz;

reg[8:0] current_state, next_state;

always @(posedge clk) begin

if (p==25000000-1) begin

p = 0;

clk_1Hz = ~clk_1Hz;

end

else begin

p = p+1;

end

end

parameter s0 = 9'b000000000,

s1 = 9'b000000001,

s2 = 9'b000000010,

s3 = 9'b000000100,

s4 = 9'b000001000,

s5 = 9'b000010000,

s6 = 9'b000100000,

s7 = 9'b001000000,

s8 = 9'b010000000,

s9 = 9'b100000000;

always @(posedge clk_1Hz)

current_state <= next_state;

always @(posedge clk)

case (current_state)

s0: next_state <= s1;

s1: next_state <= s2;s2: next_state <= s3;

s3: next_state <= s4;

s4: next_state <= s5;

s5: next_state <= s6;

s6: next_state <= s7;

s7: next_state <= s8;

s8: next_state <= s9;

s9: next_state <= s0;

default: next_state <= s0;

endcase

always @(current_state)

case (current_state)

s0: led <= 7'b100_0000;

s1: led <= 7'b111_1001;

s2: led <= 7'b010_0100;

s3: led <= 7'b011_0000;

s4: led <= 7'b001_1001;

s5: led <= 7'b001_0010;

s6: led <= 7'b000_0010;

s7: led <= 7'b111_1000;

s8: led <= 7'b000_0000;

s9: led <= 7'b001_0000;

default: led <= 7'b100_0000;

endcase

endmodule

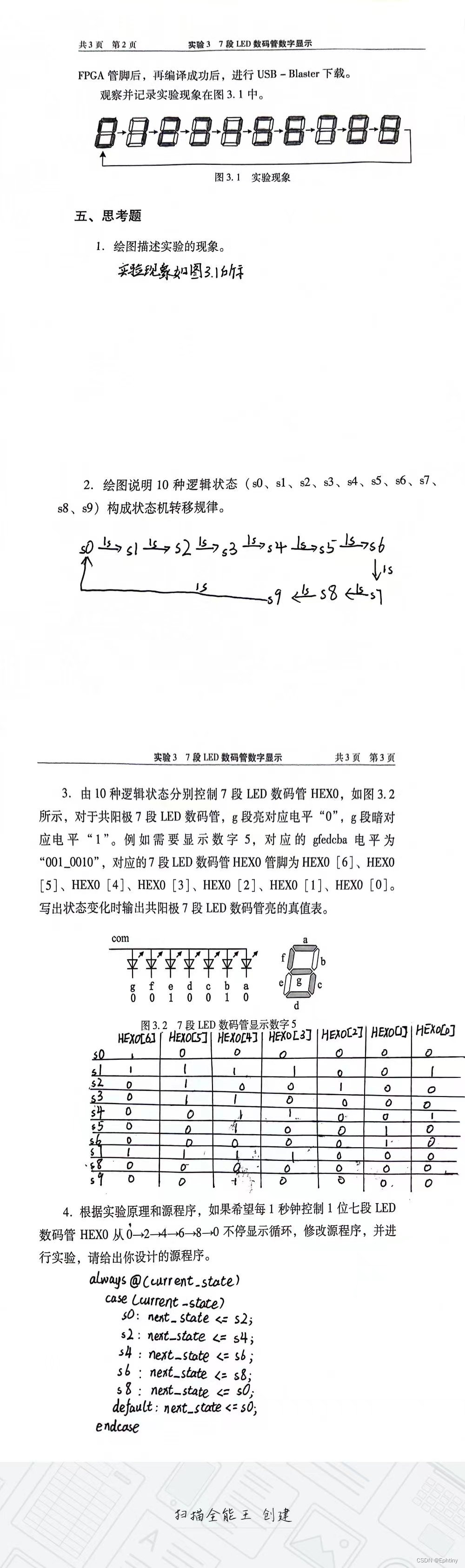

实验报告

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?