简介

SPI是一个同步的数据总线,也就是说它是用单独的数据线和一个单独的时钟信号来保证发送端和接收端的完美同步。

时钟是一个震荡信号,它告诉接收端在确切的时机对数据线上的信号进行采样。

产生时钟的一侧称为主机,另一侧称为从机。总是只有一个主机(一般来说可以是微控制器/MCU),但是可以有多个从机。

SPI是全双工(具有单独的发送和接收线路),因此可以在同一时间发送和接收数据。

注意:数据在传输过程中,高位在先还是低位在先,SPI协议并无明确规定,但是数据要在主从机中正确传输,自然双方要先约定好。

引脚

| 引脚 | 说明 |

| MISO | 主机输入端,从机输出接 |

| MOSI | 主机输出端,从机输入接 |

| SCLK | 时钟信号,主机发送 |

| SS | 片选信号,主机发送以控制与哪个从机通信,通常是低电平有效信号 |

时钟极性CKP/Clock Polarity

除了配置串行时钟速率(频率)外,SPI主设备还需要配置时钟极性。

根据硬件制造上的命名规则不同,时钟极性通常写为CKP或CPOL.时钟极性和相位共同决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据。

CKP = 0 :时钟空闲IDLE为低电平0;

CKP = 1 :时钟空闲IDLE为高电平1。

时钟相位CKE/Clock Phase(Edge)

除配置串行时钟速率和极性外,SPI主设备还应配置时钟相位(或边沿)。根据硬件制造商不同,时钟相位通常写为CKE或CPHA。

CKE = 0 :第一个跳变沿采样;

CKE = 1 :第二个跳变沿采样。

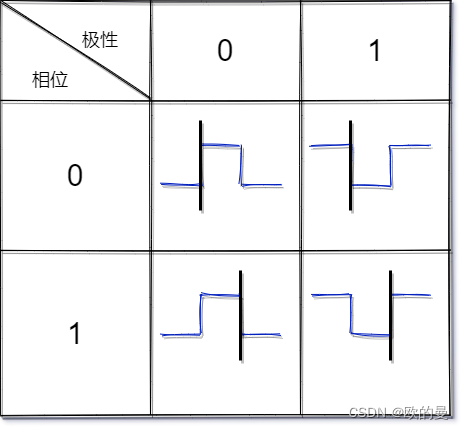

时钟配置图解

蓝色为时钟信号,黑色为采样时刻。

极性为0时钟空闲时为低电平,相位为0 :上升沿采样;相位为1 :下降沿采样。

极性为1时钟空闲时为高电平,相位为0 :下降沿采样;相位为1 :上升沿采样。

本文详细介绍了SPI(SerialPeripheralInterface)同步数据总线的工作原理,包括时钟的同步作用、主机与从机的角色划分、全双工特性以及引脚功能。重点讲解了时钟极性(CKP/CPOL)和时钟相位(CKE/CPHA)的配置,帮助读者理解如何正确设置以实现数据的高效传输。

本文详细介绍了SPI(SerialPeripheralInterface)同步数据总线的工作原理,包括时钟的同步作用、主机与从机的角色划分、全双工特性以及引脚功能。重点讲解了时钟极性(CKP/CPOL)和时钟相位(CKE/CPHA)的配置,帮助读者理解如何正确设置以实现数据的高效传输。

1295

1295

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?