本篇是关于依赖问题的第3集,还是写到哪儿算哪儿。

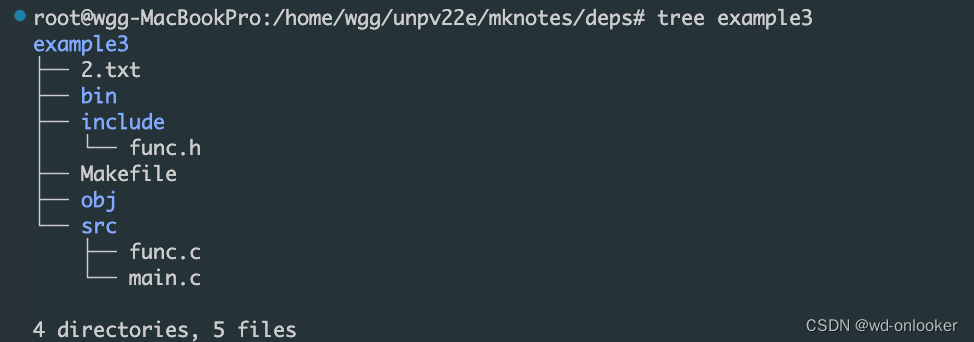

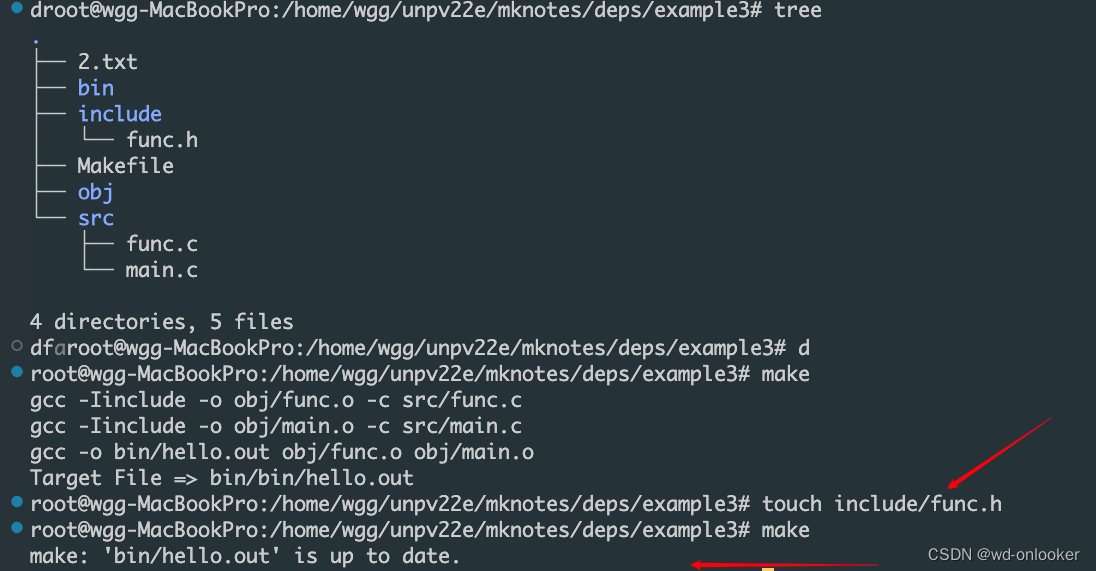

代码组织结构:

Makefile:

vpath %.h include

vpath %.c src

OBJS := func.o main.o

HEADERDIR = -Iinclude

OBJDIR = obj

BINDIR = bin

$(BINDIR)/hello.out : $(addprefix $(OBJDIR)/, $(OBJS))

gcc -o $@ $^

@echo "Target File => $(BINDIR)/$@"

$(OBJDIR)/%.o :%.c

gcc $(HEADERDIR) -o $@ -c $<

.PHONY: clean

clean:

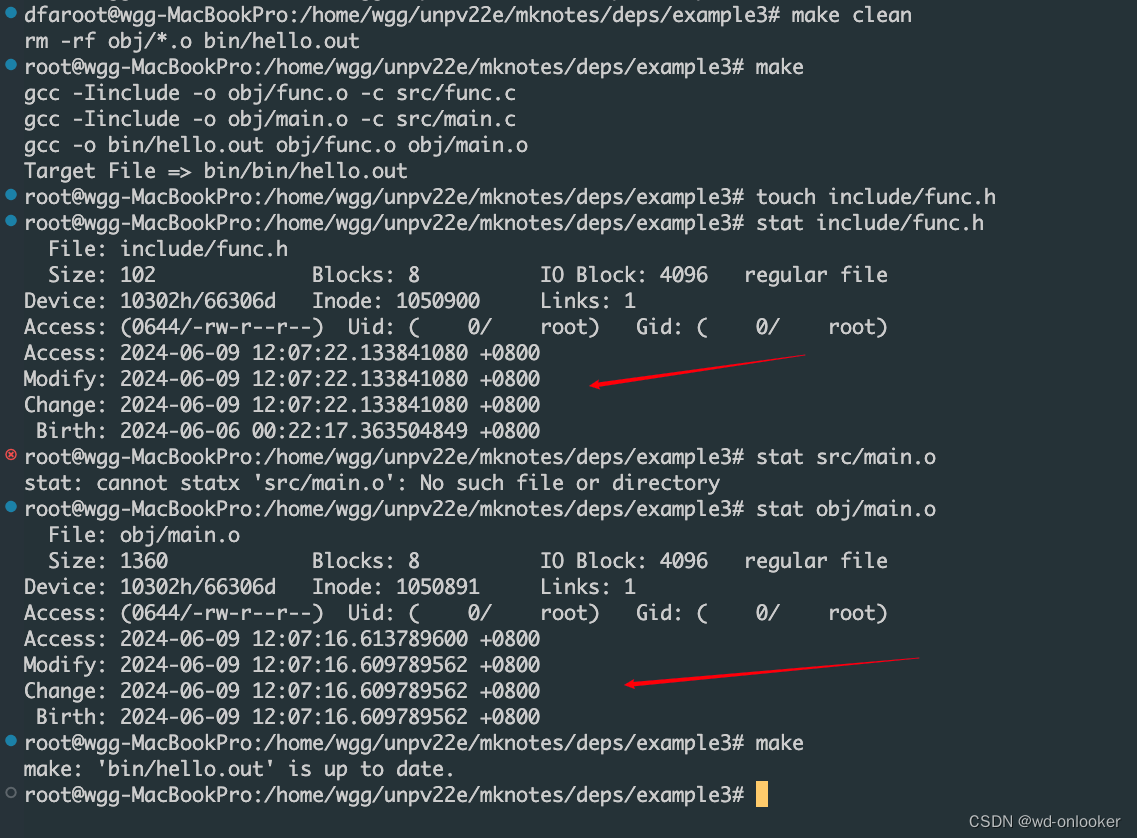

-rm -rf $(OBJDIR)/*.o $(BINDIR)/hello.out 出现问题:规则中依赖的文件更新了(prerequisites),但是目标没有更新,

这个问题分析来看就是很简单。上述Makefile没有添加对.h的依赖,嗯。。所以加上就好了

斯到普,斯到普,这儿在搞点幺蛾子。。

下面这个例子,内容上没有任何意义,只看形式就行了。

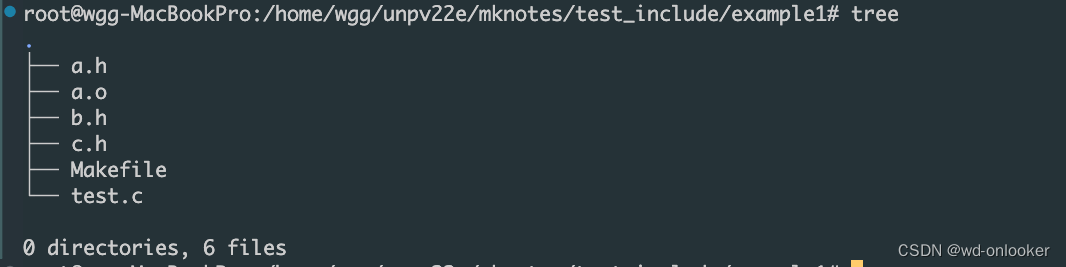

有这么个形式组织的代码

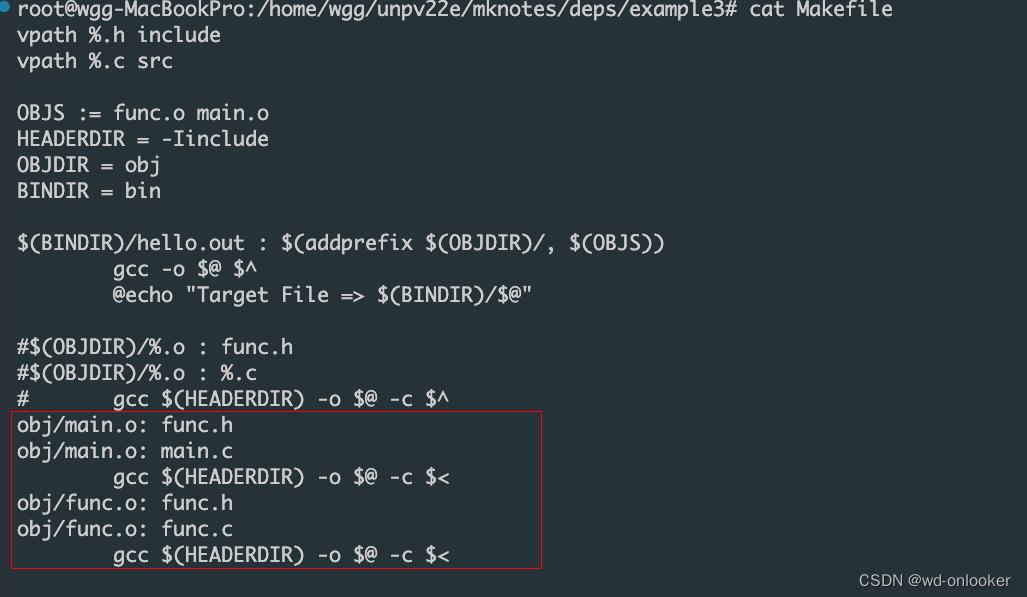

然后Makefile长这样:

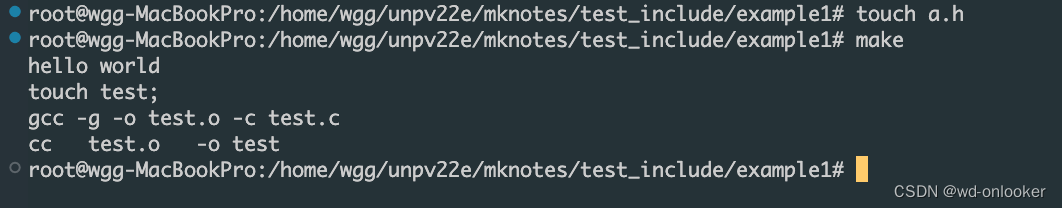

all:test

test.o:a.h

test.o:b.h

test.o:c.h

test.o:test.c

@echo "hello world";

touch test;

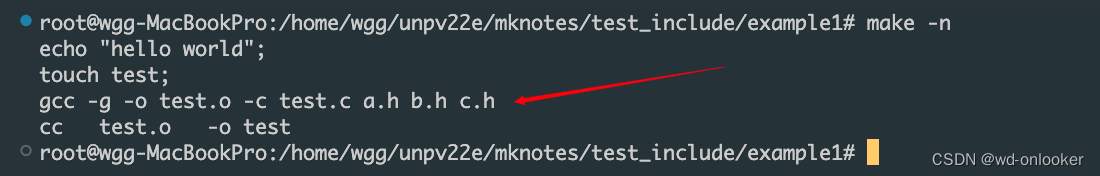

gcc -g -o test.o -c $^ Q:规则是会覆盖还是会累计?这个看$^,Makefile中的自动变量,表示依赖文件的集合。

A:

累加的!所以你这么写也可以:

...

test.o : test.c a.h b.h c.h

...因此更新其中任何的依赖文件(prerequisites),都会更新目标。(执行的时候我把$^改成$<了)

好,好, 现在回到我们刚才斯到普的地方,就这么改:

vpath %.h include

vpath %.c src

OBJS := func.o main.o

HEADERDIR = -Iinclude

OBJDIR = obj

BINDIR = bin

$(BINDIR)/hello.out : $(addprefix $(OBJDIR)/, $(OBJS))

gcc -o $@ $^

@echo "Target File => $(BINDIR)/$@"

# 添加func.h

$(OBJDIR)/%.o : func.h

$(OBJDIR)/%.o : %.c

gcc $(HEADERDIR) -o $@ -c $<

.PHONY: clean

clean:

-rm -rf $(OBJDIR)/*.o $(BINDIR)/hello.out

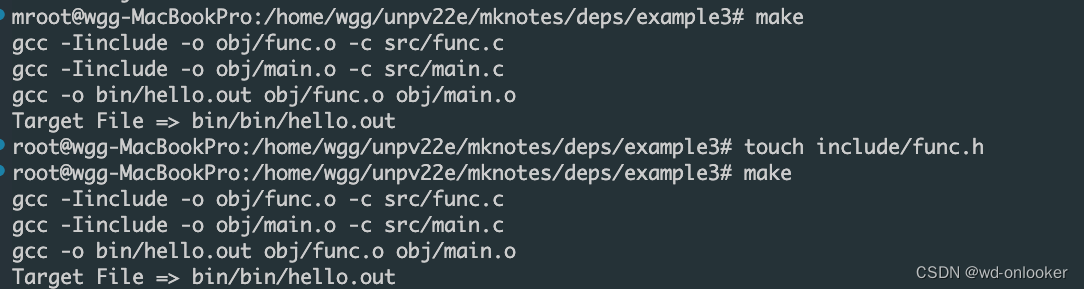

~ 结果:

我上早八,更新了func.h,目标没更新啊,可是刚刚已经亲眼所见,依赖文件是累加的!!!

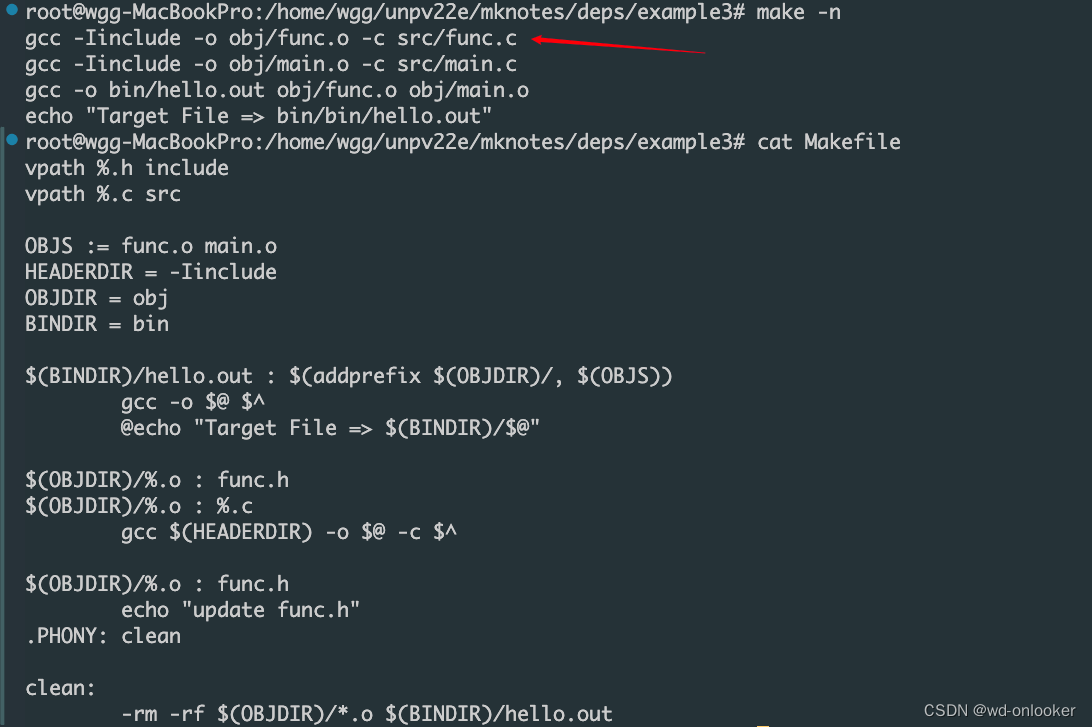

$(OBJDIR)/%.o : func.h

$(OBJDIR)/%.o : %.c

gcc $(HEADERDIR) -o $@ -c $<先把这个$<改成$^,然后运行:make -n看下依赖文件:

这里的规则是被覆盖了!!后边的规则覆盖了前边的。

总结:目标是具体文件还是带有%要仔细了(静态模式),最保险就是依赖文件写一行。

更正的话随便,有很多方式。。。

正常肯定是这样的:

...

$(OBJDIR)/%.o : %.c func.h

gcc $(HEADERDIR) -o $@ -c $<

...

1190

1190

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?