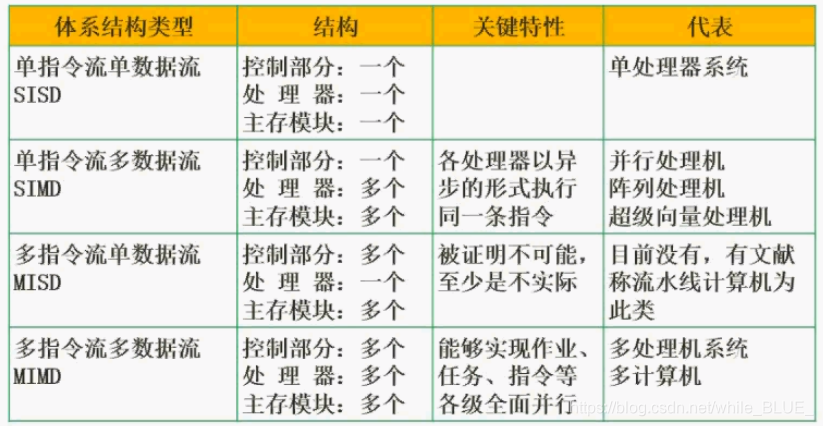

计算机体系结构分类-Flynn

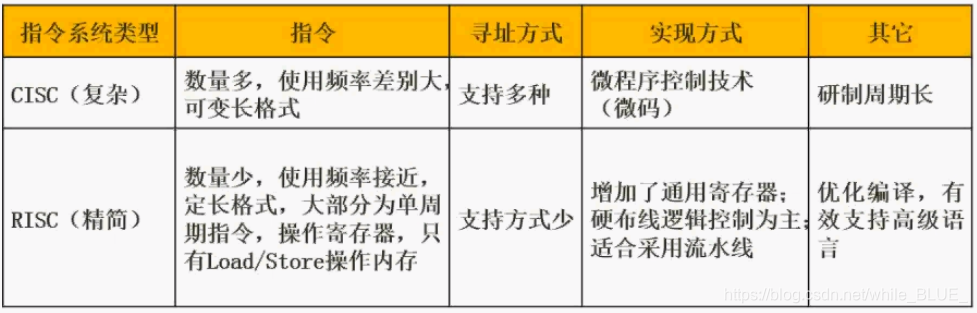

CISC与RISC

- RISC寻址方式比较单一,多寄存器寻址;指令长度固定,指令种类尽量少;

- RISC用硬布线电路实现指令解码,快速完成指令译码。

- RISC通常会比CISC配置更多的寄存器

- RISC编译器的子程序库通常要比CISC编译器的子程序库大得多

- RISC比CISC更加适合VLSI工艺的规整性要求

流水线

- 流水线周期 为指令分段中执行时间最长的一段

- 流水线执行时间计算公式:1条指令执行时间+(指令条数-1)*流水线周期

- 吞吐率:TP=指令条数/流水线执行时间

- 最大吞吐率:TPmax=1/1个流水线周期时间

- 流水线加速比:S=不使用流水线执行时间/使用流水线执行时间

- 流水线效率:E=n个任务占用的时空区/k个流水段的总的时空区

补充:

最大吞吐率取决于流水线中最慢一段所需的时间

如果流水线出现断流,加速比会明显下降

要使加速比和效率最大化应该对流水线各级采用相同的运行时间

流水线采用异步控制不会提高其性能

存储器

常用的虚拟存储器由 主存-辅存 两级存储器组成

随机存取存储器RAM:掉电丢失数据

只读存储器ROM:掉电不丢(例如存储BIOS芯片)

存储设备按访问速度排序为:通用寄存器>Cache>内存>硬盘。

- DRAM:动态随机存取存储器;(计算机系统主存)

- SRAM:静态随机存取存储器;

- Cache:高速缓存;

- EEPROM:电可擦可编程只读存储器。

程序的局限性表现在时间局部性和空间局部性:

(1)时间局部性是指如果程序中的某条指令一旦被执行,则不久的将来该指令可能再次被执行;

(2)空间局部性是指一旦程序访问了某个存储单元,则在不久的将来,其附近的存储单元也最有可能被访问。

相联存储器

是一种按内容访问的存储器。

Cache

-

位于CPU和主存之间,由硬件实现;主存单元地址与Cache单元地址之间的转换工作由硬件完成。

-

容量小,一般在几KB到几MB之间:速度一般比主存快5到10倍,由快速半导体存储器制成;

-

其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。

-

Cache主存储器系统的平均周期(平均存取时间):t=Cache访问命中率*Cache周期时间+(1-Cache访问命中率)*主储存器周期时间

主存与Cache的地址映射方式

(1)直接相联映射方式。

这是一种最简单而又直接的映射方法,指主存中每个块只能映射到Cache的一个特定的块。在该方法中,Cache块地址j和主存块地址i的关系为:

j=i mod Cb

其中Cb是Cache的块数。这样,整个Cache地址与主存地址的低位部分完全相同。

直接映射法的优点是所需硬件简单,只需要容量较小的按地址访问的区号标志表存储器和少量比较电路;缺点是Cache块冲突概率较高,只要有两个或两个以上经常使用的块恰好被映射到Cache中的同一个块位置时,就会使Cache命中率急剧下降。

(2)全相联映射方式。

全相联映射是指主存中任一块都可以映射到Cache中任一块的方式,也就是说,当主存中的一块需调入Cache时,可根据当时Cache的块占用或分配情况,选择一个块给主存块存储,所选的Cache块可以是Cache中的任意一块。

这种映射方式允许主存的每一块信息可以存到Cache的任何一个块空间,也允许从已被占满的Cache中替换掉任何一块信息。全相联映射的优点是块冲突概率低;其缺点是访问速度慢,并且成本太高。

(3)组相联映射方式。

这种方式是前两种方式的折衷方案。这种映射方式在组间是直接映射,而组内是全相联映射,其性能和复杂性介于直接映射和全相联映射之间。

磁盘结构与参数

- 存取时间=寻道时间+等待时间(平均定位时间+转动延迟)

注(寻道时间是指磁头移动到磁道所需的时间;等待时间为等待读写的扇区转到磁头下方所用的时间。)

总线

- 内部总线

- 系统总线:数据总线、地址总线、控制总线

- 外部总线

我们常说的微机总线就是指系统总线,比如PC总线、ISA总线、EISA总线、PCI总线等都属于系统总线。

SCSl是小型计算机系统接口的简称,是一种智能的通用接口标准。可以说是各种计算机与外部设备之间的接口标准。

总线是在计算机中连接两个或多个功能部件的一组共享的信息传输线,它的主要特征就是多个部件共享传输介质。它是构成计算机系统的骨架,是各个功能部件之间进行信息传输的公共通道,借助总线的连接,计算机各个部件之间可以传送地址、数据和各种控制信息。在计算机系统中采用总线结构,便于实现系统的积木化构造,同时可以有效减少信息传输线的数量。

冗余

冗余技术一般包括时间冗余、信息冗余、结构冗余和冗余附加技术,其中结构冗余按照工作方法可以分为静态、动态和混合冗余。

容错系统是指在一定程度上具有容错功能的系统,实现容错的主要办法就是冗余,冗余附加技术的构成主要包括冗余备份程序的存储及调用、实现错误检测和错误恢复的程序、实现容错软件所需的固化程序。

1.结构冗余

结构冗余是常用的冗余技术,按其工作方式,可分为:

(1)静态冗余。静态沉余又称为屏蔽冗余或被动冗余,常用的有三模冗余和多模冗余。静态冗余通过表决和比较来屏蔽系统中出现的错误。例如,三模冗余是对三个功能相同,但由不同的人采用不同的方法开发出的模块的运行结果进行表决,以多数结果作为系统的最终结果。即如果模块中有一个出错,这个错误能够被其他模块的正确结果“屏蔽”。由于无需对错误进行特别的测试,也不必进行模块的切换就能实现容错,故称为静态容错。

(2)动态冗余。动态冗余又称为主动冗余,它是通过故障检测、故障定位及故障恢复等手段达到容错的目的。其主要方式是多重模块待机储备,当系统检测到某工作模块出现错误时,就用一个备用的模块来顶替它并重新运行。各备用模块在其待机时,可与主模块一样工作,也可不工作。前者叫做热备份系统(双重系统),后者叫做冷备份系统(双工系统、双份系统)。在热备份系统中,两套系统同时、同步运行,当联机子系统检测到错误时,退出服务进行检修,而由热备份子系统接替工作,备用模块在待机过程中其失效率为0;处于冷备份的子系统平时停机或者运行与联机系统无关的运算,当联机子系统产生故障时,人工或自动进行切换,使冷备份系统成为联机系统。在运行冷备份时,不能保证从系统断点处精确地连续工作,因为备份机不能取得原来的机器上当前运行的全部数据。

(3)混合冗余。混合冗余技术是将静态冗余和动态冗余结合起来,且取二者之长处。它先使用静态冗余中的故障屏蔽技术,使系统免受某些可以被屏蔽的故障的影响。而对那些无法屏蔽的故障则采用主动冗余中的故障检测、故障定位和故障恢复等技术,并且对系统可以作重新配置。因此,混合冗余的效果要大大优于静态冗余和动态冗余。然而,由于混合冗余既要有静态元余的屏蔽功能,又要有动态冗余的各种检测和定位等功能,它的附加硬件的开销是相当大的,所以混合冗余的成本很高,仅在对可靠性要求极高的场合中采用。

2.信息冗余

信息冗余是在实现正常功能所需要的信息外,再添加一些信息,以保证运行结果正确性的方法。例如,检错码和纠错码就是信息冗余的例子。这种冗余信息的添加方法是按照一组预定的规则进行的。符合添加规则而形成的带有冗余信息的字称为码字,而那些虽带有冗余信息但不符合添加规则的字则称为非码字。当系统出现故障时,可能会将码字变成非码字,于是在译码过程中会将引起非码字的故障检测出来,这就是检错码的基本思想。纠错码则不仅可以将错误检测出来,还能将由故障引起的非码字纠正成正确的码字。

由此可见,信息冗余的主要任务在于研究出一套理想的编码和译码技术来提高信息冗余的效率。编码技术中应用最广泛的是奇偶校验码、海明校验码和循环冗余校验码。

3.时间冗余

时间冗余是以时间(即降低系统运行速度)为代价以减少硬件冗余和信息冗余的开销来达到提高可靠性的目的。在某些实际应用中,硬件冗余和信息冗余的成本、体积、功耗、重量等开销可能过高,而时间并不是太重要的因素时,可以使用时间冗余。时间冗余的基本概念是重复多次进行相同的计算,或称为重复执行(复执),以达到故障检测的目的。

实现时间冗余的方法很多,但是其基本思想不外乎是对相同的计算任务重复执行多次,然后将每次的运行结果存放起来再进行比较。若每次的结果相同,则认为无故障;若存在不同的结果,则说明检测到了故障。不过,这种方法往往只能检测到瞬时性故障而不宜检测永久性的故障。

4.冗余附加

冗余附加技术包括:冗余备份程序的存储及调用,实现错误检测和错误恢复的程序,实现容错软件所需的固化程序。

计算机可靠性

可靠性指的是,软件产品与在规定的一段时间内和规定的条件下维持其性能水平有关的能力,是一个系统对于给定时间间隔内、在给定条件下无失效运作的概率。

它的子特性包括:成熟性、容错性、易恢复性,对于软件可靠性与软件潜在错误的数量、位置有关,并且与软件产品的使用方式有关,对于软件产品的开发方式并不能决定软件产品的可靠性。

- 软件的可靠性是指一个系统在给定时间间隔内和给定条件下无失效运行的概率。

- 软件的可用性是指软件在特定使用环境下为特定用户用于特定用途时所具有的有效性。

- 软件的可维护性是指与软件维护的难易程度相关的一组软件属性。

- 软件的可伸缩性是指是否可以通过运行更多的实例或者采用分布式处理来支持更多的用户。

平均无故障时间定义为MTBF

差错控制

- 码距:一个编码系统的码距是整个编码系统中任意(所有)两个码字的最小距离(例如111,000,最小码距为3)

寻址方式

- 立即寻址的特点是:指令的地址字段指出的不是操作数的地址,而是操作数本身;

- 直接寻址特点是:在指令格式的地址字段中直接指出操作数在内存的地址;

- 寄存器寻址的特点是:指令中给出的操作数地址不是内存的地址单元号,而是通用寄存器的编号(当操作数不放在内存中,而是放在CPU的通用寄存器中时,可采用寄存器寻址方式);

寄存器间接寻址方式与寄存器寻址方式的区别在于:指令格式中操作数地址所指向的寄存器中存放的内容不是操作数,而是操作数的地址,通过该地址可在内存中找到操作数;

相对寻址的特点是:把程序计数器PC的内容加上指令格式中的形式地址来形成操作数的有效地址。

按寻址方式划分的存储器:顺序、直接、随机存储器

相联存储器是一种按存储内容来存储和访问的存储器

例题

-

在计算机体系结构中,CPU内部包括程序计数器PC、存储器数据寄存器MDR、指令寄存器IR和存储器地址寄存器MAR等。

若CPU要执行的指令为:MOVRO,#100(即将数值100传送到寄存器RO中),则CPU首先要完成的操作是()A.100->RO

B.100->MDR

C.PC->MAR

D.PC->IR

解析:

CPU中的程序计数器PC用于保存要执行的指令的地址,访问内存时,需先将内存地址送入存储器地址寄存器MAR中,向内存写入数据时,待写入的数据要先放入数据寄存器MUR。程序中的指令一般放在内存中,要执行时,首先要访问内存取得指令并保存在指令寄存器IR中。

计算机中指令的执行过程一般分为取指令、分析指令并获取操作数、运算和传送结果等阶段,每条指令被执行时都要经过这几个阶段。若CPU要执行的指令为:MOVRO,#100(即将数值100传送到寄存器RO中),则CPU首先要完成的操作是将要执行的指令的地址送入程序计数器PC,访问内存以获取指令。

- VLIW:(Very Long Instruction Word,超长指令字)一种非常长的指令组合,它把许多条指令连在一起,增加了运算的速度。

1882

1882

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?