一.实验预习

设计 一个8位流水灯电路,要求如下:

(1)8个灯每次7亮1暗;

(2)流动方向从左到右;

(3)采用JK或者D触发器构成的异步计数器和74138实现;

(4)流水灯每秒钟变化一次状态(调用50M分频信号模块,将1Hz信号作为流水灯电路的时钟信号输入)。

二、实验内容

二、实验内容

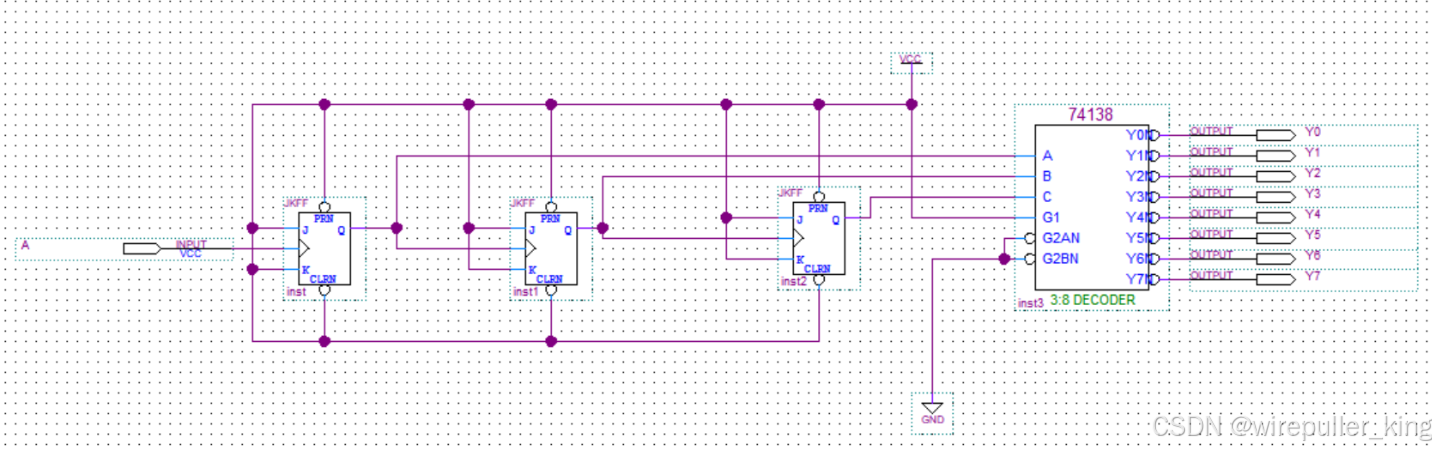

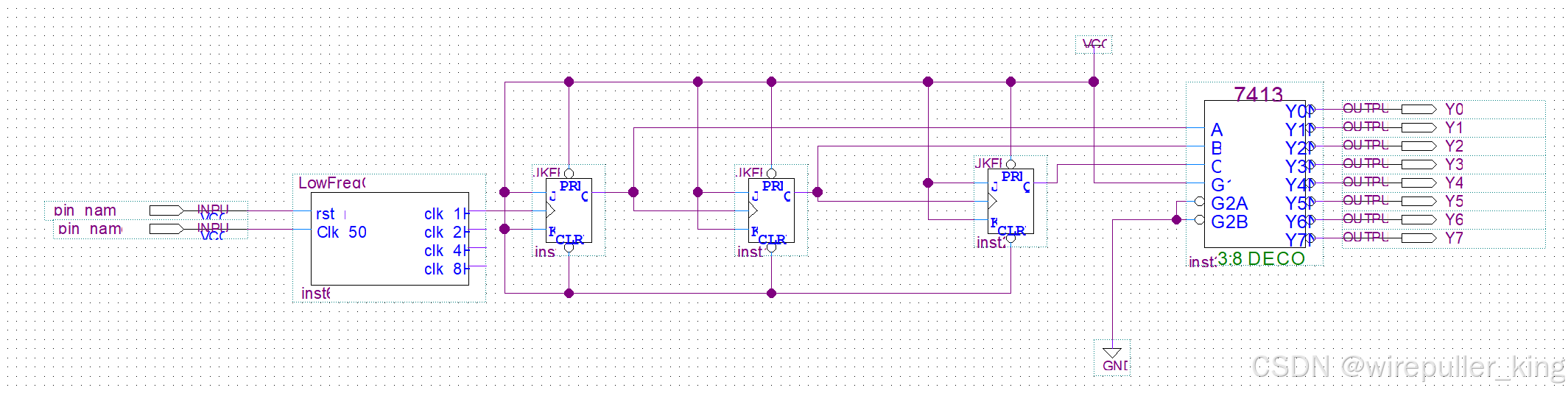

1、设计计数译码型8位流水灯的逻辑电路。要求采用JK或者D触发器构成 SSI异步3位二进制计数器和74138实现,进行仿真。

2、利用实验板50MHZ系统时钟,采用分频的方案产生1HZ、2HZ、4HZ、8HZ的低频时钟信号(使用VHDL语言描述),用于实验电路的CP时钟,并下载至实验板测试。

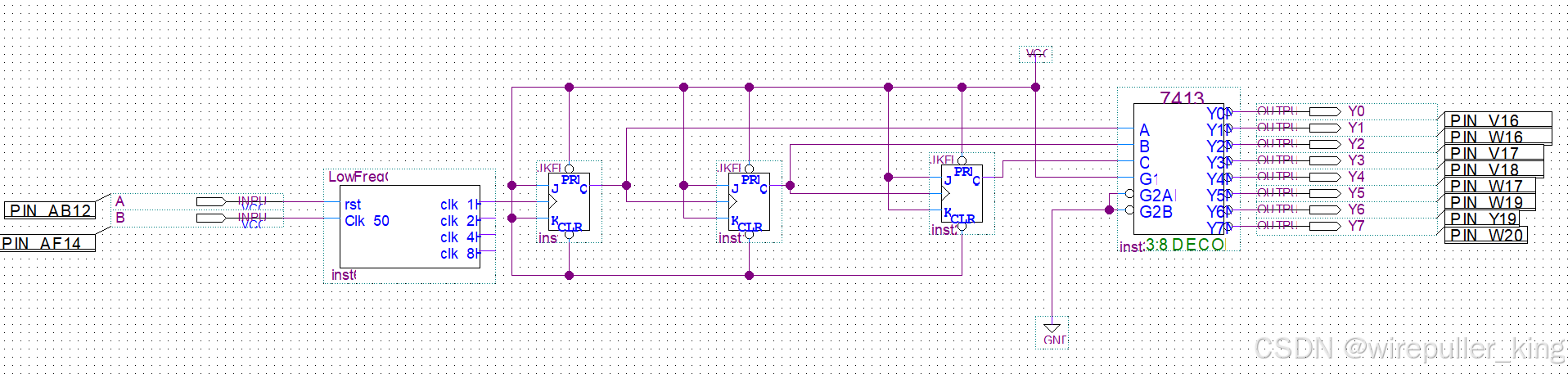

3、应用层次化设计思路将调用50M分频信号模块,作为流水灯电路的CP信号输入,实现自动流水灯设计(不需要仿真),并下载实验板进行功能测试。

(1):使用预习电路画出仿真波形:

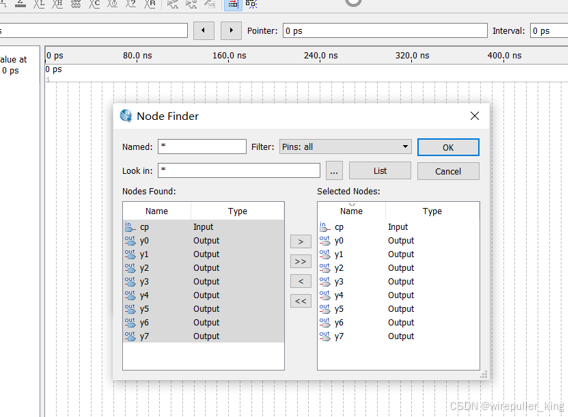

鼠标左键双击左侧空白区域,调出 Insert Node or BUS (添加节点)窗口。

点击Node Finder 按钮,调出Node 添加界面→

点击OK键→点击List 按键→点击双箭头按键→连续两次点击OK键,把原理图设计成功的电路中所有的节点加载到波形仿真文件,进行观察。

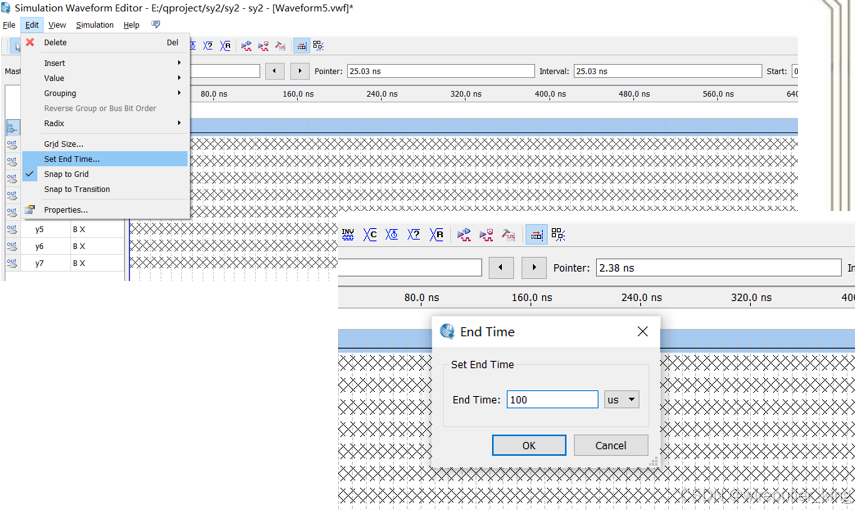

设置仿真时间长度(Set end time)可设置成100 微秒。

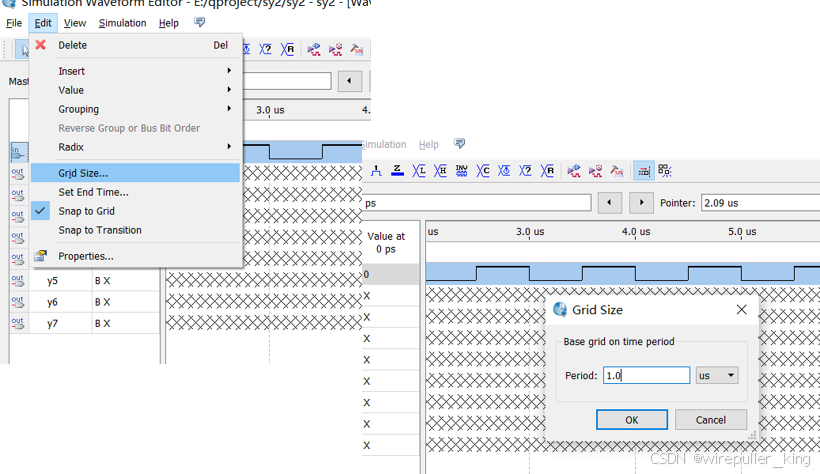

设置仿真时间周期(Set Grid Size)可设置成1微秒。

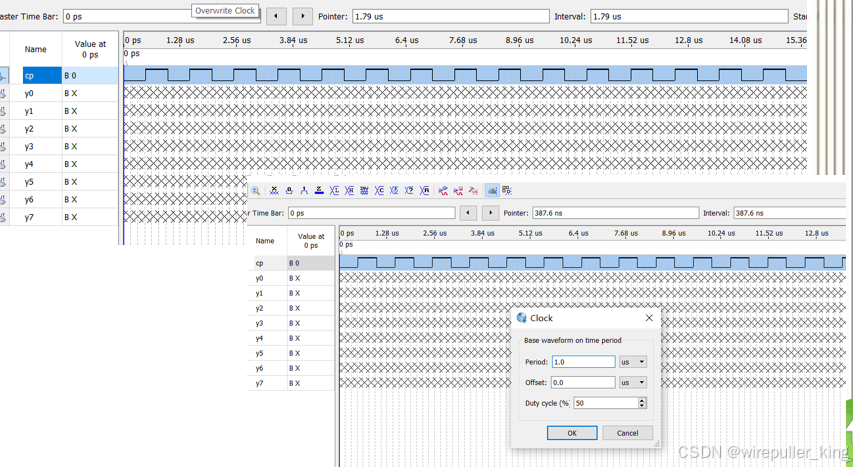

选中CP信号,点击Overwrite Clock 图标,将低频脉冲作为输入时钟信号,其中Period(cp 周期)可设置成1 微秒。

选中CP信号,点击Overwrite Clock 图标,将低频脉冲作为输入时钟信号,其中Period(cp 周期)可设置成1 微秒。

运行仿真波形:

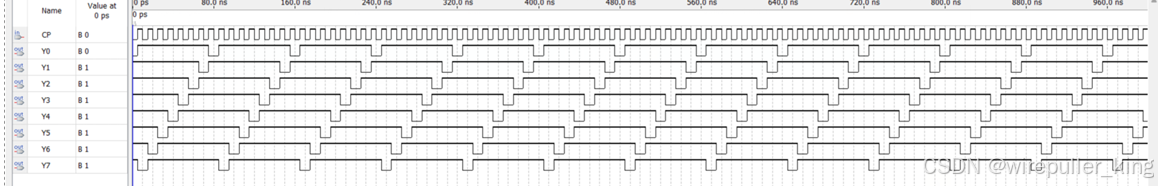

如图即为正确。

如图即为正确。

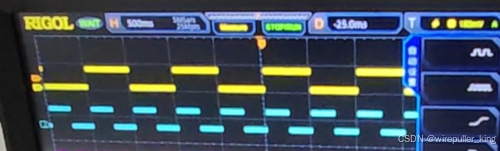

(2):时钟信号产生及测试

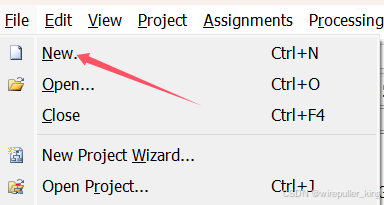

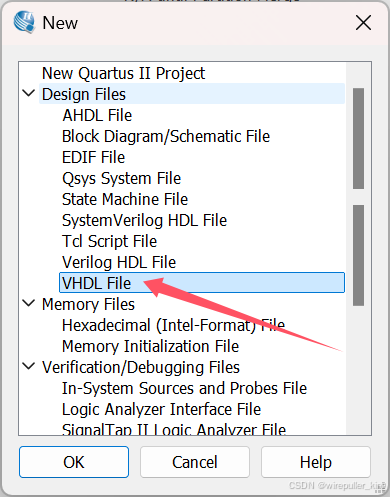

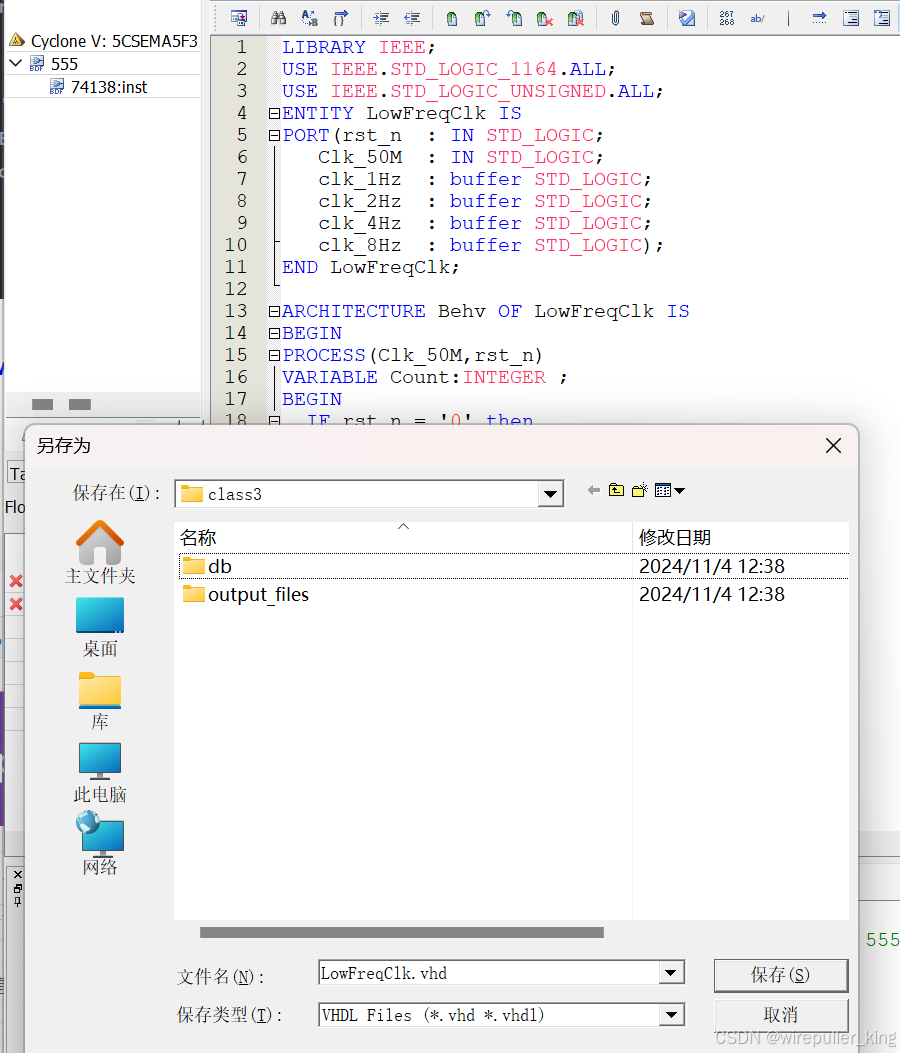

[1]:新建VHDL设计文件

输入VHDL程序代码,如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY LowFreqClk IS

PORT(rst_n : IN STD_LOGIC;

Clk_50M : IN STD_LOGIC;

clk_1Hz : buffer STD_LOGIC;

clk_2Hz : buffer STD_LOGIC;

clk_4Hz : buffer STD_LOGIC;

clk_8Hz : buffer STD_LOGIC);

END LowFreqClk;

ARCHITECTURE Behv OF LowFreqClk IS

BEGIN

PROCESS(Clk_50M,rst_n)

VARIABLE Count:INTEGER ;

BEGIN

IF rst_n = '0' then

Count := 0 ;

clk_8Hz <= '0';

ELSIF Clk_50M'EVENT AND Clk_50M='1' THEN

IF Count >= 3124999 THEN

clk_8Hz <=not clk_8Hz;

Count := 0 ;

ELSE

Count := Count + 1;

END IF;

END IF;

END PROCESS ;

PROCESS(clk_8Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_4Hz <= '0';

ELSIF Clk_8Hz'EVENT AND Clk_8Hz='1' THEN

clk_4Hz <=not clk_4Hz;

END IF;

END PROCESS ;

PROCESS(clk_4Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_2Hz <= '0';

ELSIF Clk_4Hz'EVENT AND Clk_4Hz='1' THEN

clk_2Hz <=not clk_2Hz;

END IF;

END PROCESS ;

PROCESS(clk_2Hz,rst_n)

BEGIN

IF rst_n = '0' then

clk_1Hz <= '0';

ELSIF Clk_2Hz'EVENT AND Clk_2Hz='1' THEN

clk_1Hz <=not clk_1Hz;

END IF;

END PROCESS ;

END Behv;

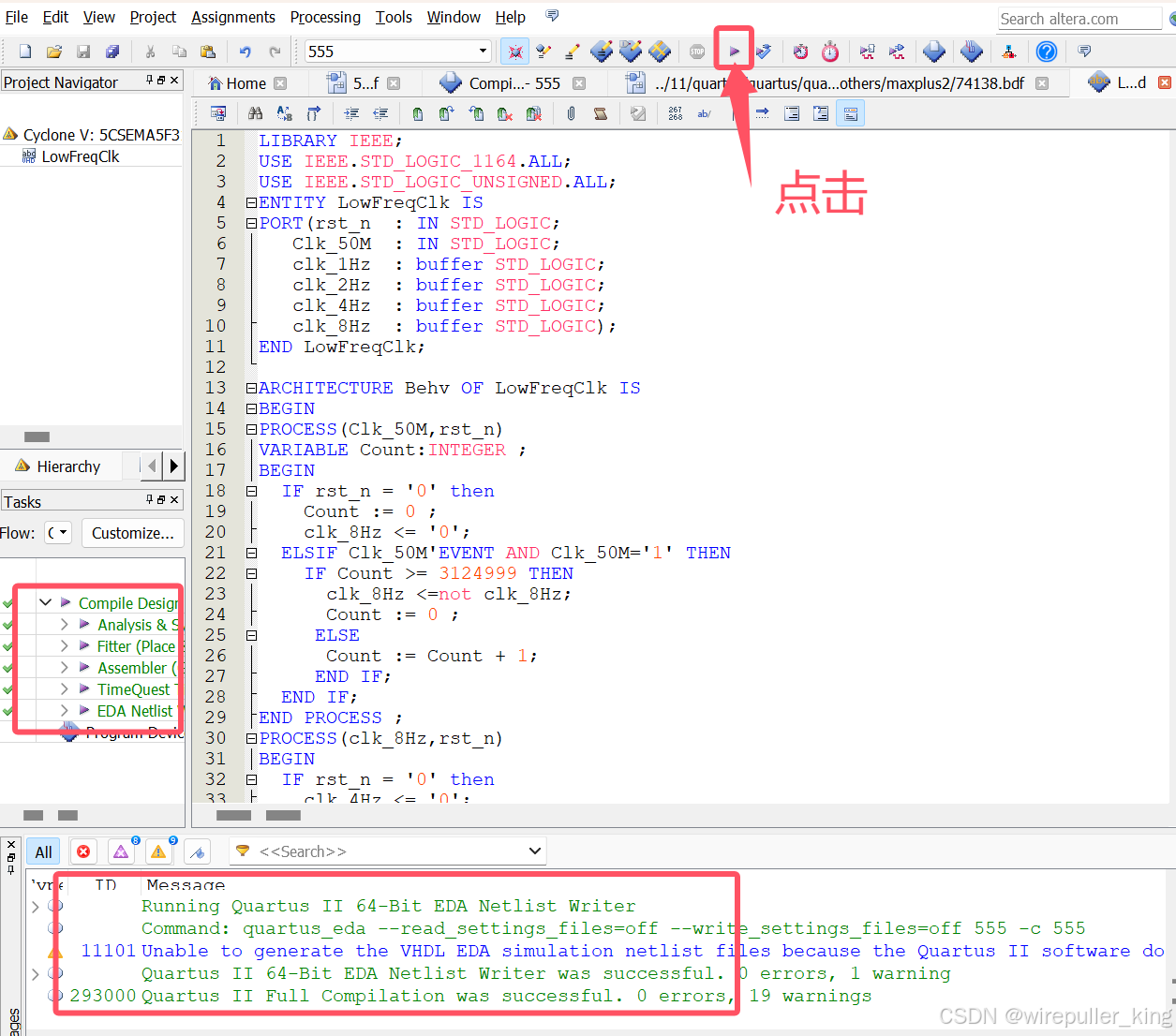

保存文件名为:LowFreqClk.VHD,并编译通过(这步要注意)

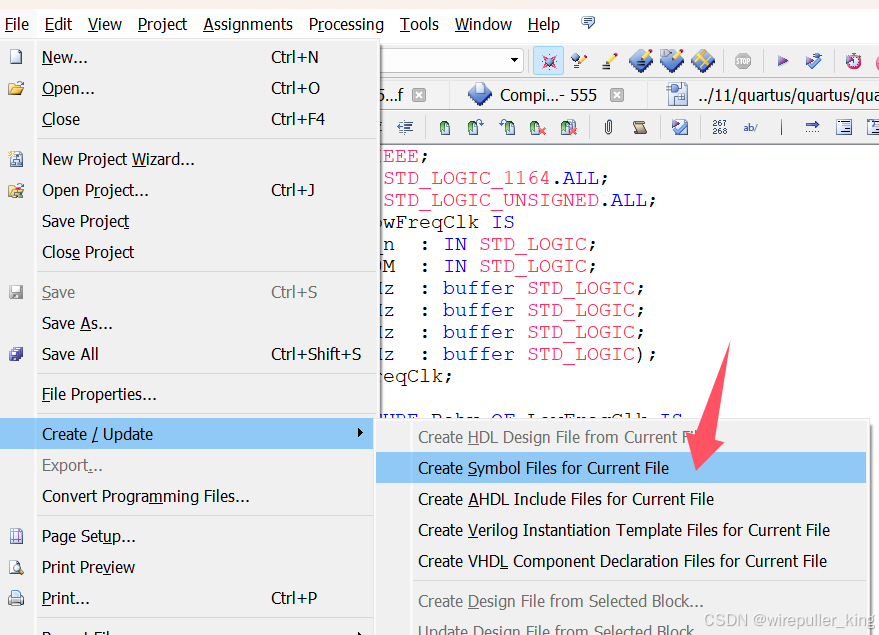

[2]:为设计文件创建符号文件

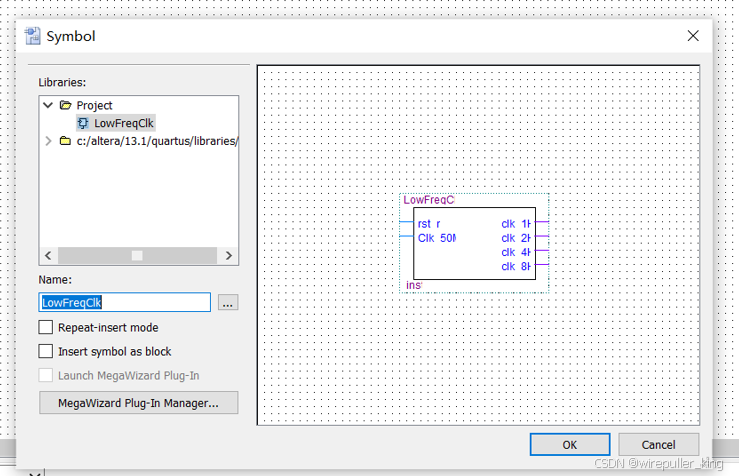

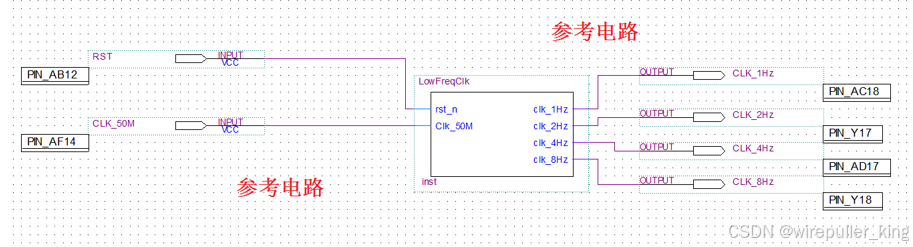

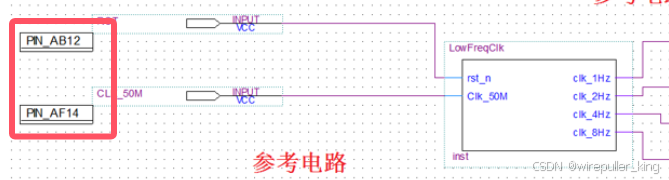

[3]画电路图测试:

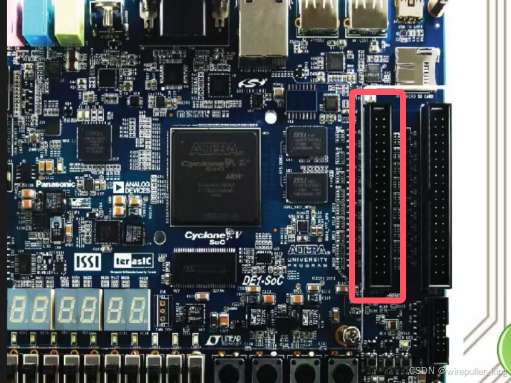

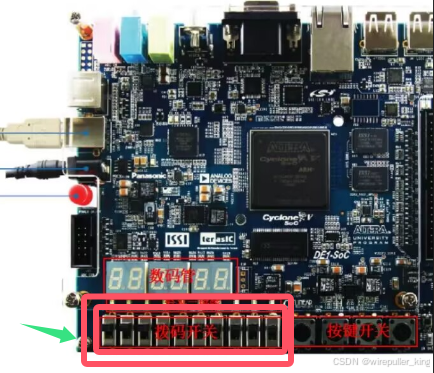

(3)、下载实验板进行功能测试

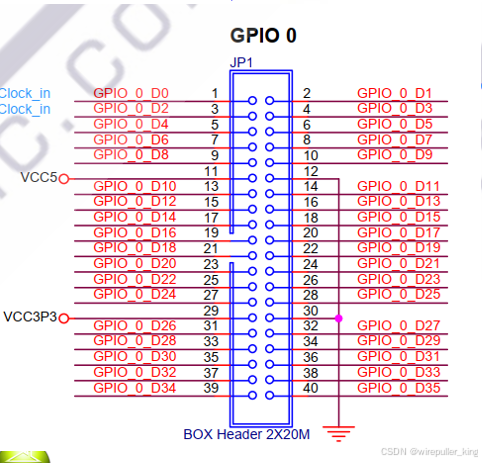

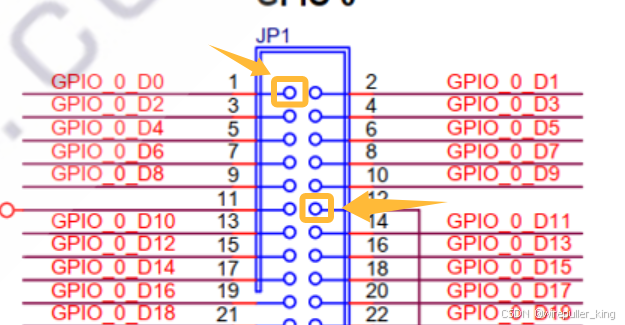

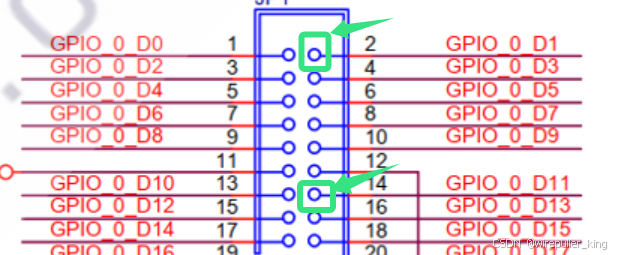

[1]示波器接线:

)

)

[2]加入50M分频模块

[3]下载至电路板并验证功能

VID_20241104_115038

结果为灯流向闪动

ending--------------------------------------------------

有帮助请点赞或评论支持,有错误也请指出,感谢观看。

937

937

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?