转自:http://blog.sina.com.cn/s/blog_8daab13801016dtn.html

终于拿到了友善之臂mini2440的板子,从今天开始就要开始我的linux之旅。之前断断续续看过2440的数据手册及linux应用,给我的总体感觉就是真难,简直是摸不着头脑。哎,大家都说女人不适合做技术,这条路我不知道能不能坚持下去,即使坚持下去我又能走多远呢?不过如果不做技术,我还能做什么呢?哎,废话不多说,还是一步一步地开始吧。

感觉从STM32到s3c2440,这中间有一个跳跃,因为STM32一直是使用片上FLASH和RAM,MDK也是定义好了下载算法,进行简单地配置就可以了。而s3c2440确需要外扩FLASH和SDRAM,对于他们之间如何联系起来我却不是很了解。只是一边看着数据手册一边看原理图及板子的使用手册慢慢地理解,下面进行s3c2440与SDRAM之间的连接进行简单地分析。

S3C2440 有 27 根地址线 ADDR[26:0],2^27= 128Mbyte ,这也相当于一个bank的最大容量,但是bank6和bank7可配置大小,如果小于128M就有些高位地址线没用。在友善之臂上使用的是2片32M的SDRAM,总容量为64M,2^26= 32Mbyte,因此这里用到最高地址总线为ADDR25。

板上用到的是HY57V561620FTP,4Mbit * 4bank *16 ,共32Mbyte。

这里要了解下 SDRAM 的寻址原理。

SDRAM 内部是一个存储阵列。可以把它想象成一个表格。和表格的检索原理一样,先指定行,再指定列,就可以准确找到所需要的存储单元。这个表格称为逻辑BANK。目前的 SDRAM 基本都是 4 个 BANK。寻址的流程就是先指定 BANK 地址,再指定行地址,最后指定列地址。

HY57V561620F这个SDRAM有

13根行地址线 RA0-RA12

9 根列地址线 CA0-CA82 根BANK 选择线 BA0-BA1

SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作过程是将读写的地址分两次输入到芯片中,每一次都由同一组地址线输入。两次送到芯片上去的地址分别称为行地址和列地址。它们被锁存到芯片内部的行地址锁存器和列地址锁存器。/RAS 是行地址锁存信号,该信号将行地址锁存在芯片内部的行地址锁存器中;/CAS 是列地址锁存信号,该信号将列地址锁存在芯片内部的列地址锁存器中,这样就更容易理解这里只有15个地址总线了。

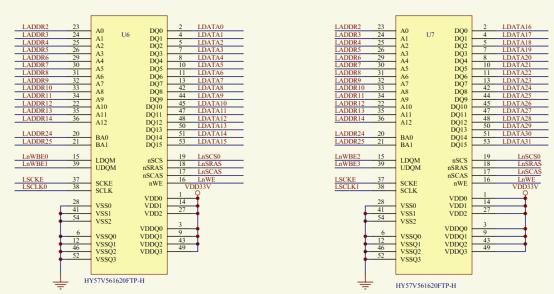

以下是SDRAM的部分的原理图:

从原理图上可以看到SDRAM的A0接到的是2440地址线2,可做以下理解:

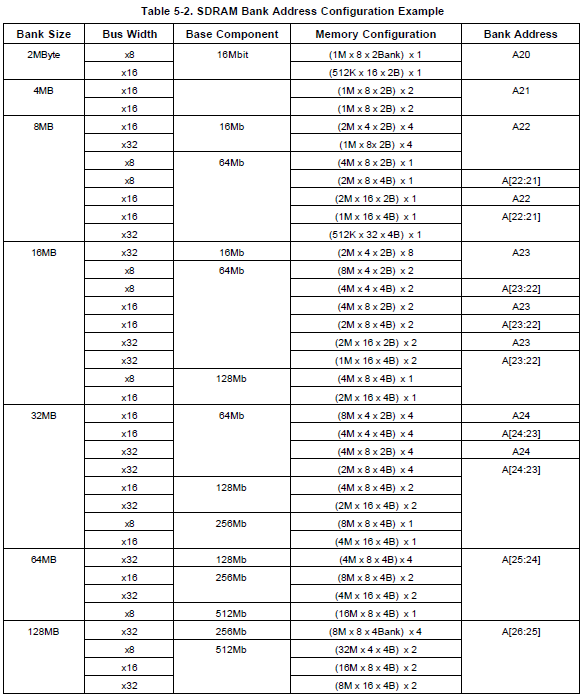

这里使用的是2片16bit的SDRAM并联组成的32bit,数据宽度为32,查看2440的数据手册第五章

原理图中的BA0~BA1 代表了SDRAM 的最高2地址位,因此接ADDR24与ADDR25。也可以这样推理:13根行地址线+9根列地址线 = 22根。另外 HY57V561620F 一个存储单元是2 个字节,相当于有了23根地址线。BA0,BA1 是最高地址位,所以应该接在ADDR24,ADDR25上。也就是说SDRAM 的BA0,BA1接S3C2440 的哪几根地址线是根据整个SDRAM 的容量来决定的。

在此,我还有一个疑惑:板子使用手册上说,SDRAM的物理起始地址为 0x30000000,这个是怎么得出的呢?手册上解释说是它们都使用了nGCS6 作为片选。

2240有8 根片选信号 ngcs0-ngcs7,对应 bank0-bank7,当ngcsx为低电平的时候,就选中对应的bankx,如果使用ngcx6作为片选信号,则选中的是bank6,查手册bank6的其实地址是0x30000000.这样是没错。但是我却自以为这里的片选信号是接的ngcx0,所以就出现了理解上的失误。在仔细看了原理图,我将LnSCS0混淆成了LnGCS0,照一般性的理解可能LNSCS0应该就是从LnGSCS0引脚出来,其实是从LnGSCS6上!哎,不能自以为是啊。

408

408

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?