SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器,同步是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写

一.内部结构

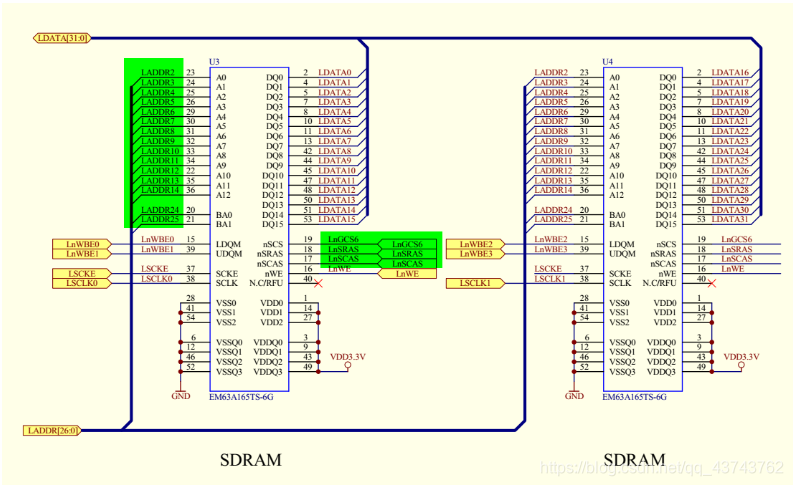

原理图如下:

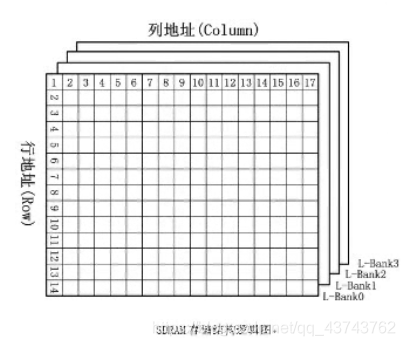

存储逻辑结构:

可以看出SDRAM的内部是一个阵列,就像表格一样,其寻址方式是按照块、行、列来的,即先选定SDRAM芯片,然后发出块信号确定那一块,再发出行信号确定哪一行,再发出列信号确定哪一列。

CPU对SDRAM的访问可以分为以下几步:

- CPU对存储控制器发出统一编址

- 内存控制器发出片选信号,选定SDRAM芯片

- 选定哪一个Bank(通过ADDR24、ADDR25信号线选定,总共4个Bank)

- 对选定的Bank进行行列寻址

- 找到对应的地址,通过32根数据线进行数据传输(原理图中是32位)

看起来很简单,但是我们要考虑到,不同规格SDRAM对应着不同的寻址方式,因为不同的SDRAM可能行列数不一样,对时序要求不一样,所以在访问SDRAM之前,我们要配置存储控制器中的一些寄存器来匹配SDRAM!!!

二.相关寄存器

存储控制器一共有13个寄存器,6种寄存器,对BANK0~BANK5进行访问时,只需要配置BWSCON和BANKCONx寄存器,但是对SDRAM访问,不仅仅需要对这俩个寄存器进行配置,还需要额外配置4个寄存器。

下面以访问SDRAM为例子介绍一下这些寄存器(按照芯片手册中的顺序来介绍):

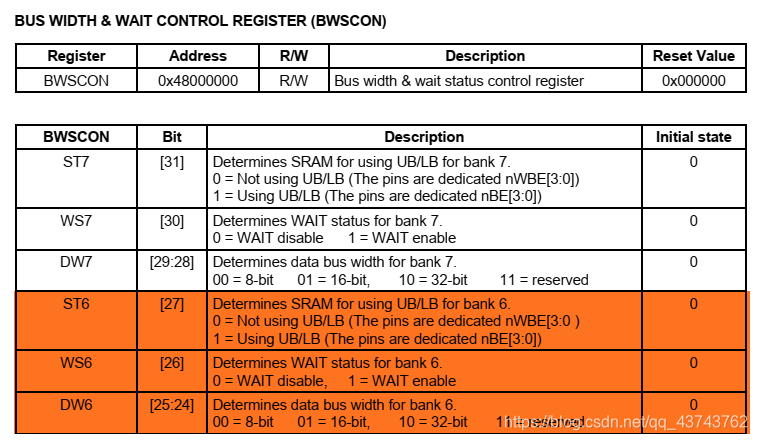

BWSCON

位宽&等待控制寄存器

- ST6:决定是否使用SDRAM的数据掩码,对SDRAM时为0,对SRAM时为1。

- WS6:决定是否使用WAIT信号,一般不使用。(WAIT信号就是在SDRAM没准备好的时候,由SDRAM发给CPU,请求延迟一段时间)

- DW6:决定BANK位宽,自然是32位。

所以,BWSCON寄存器要或运算的值为:0x02000000

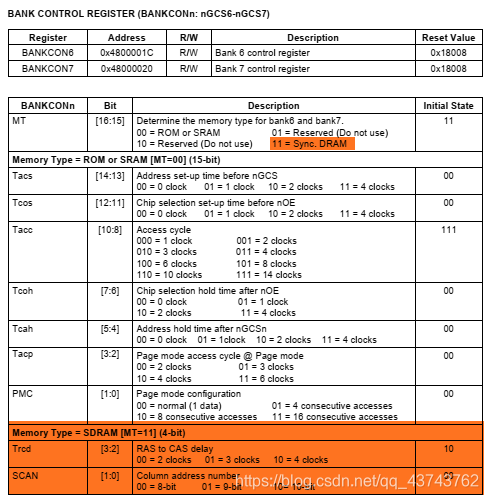

BANKCON6

BANK控制寄存器,用来控制外接设备的访问时序的,BANK0~BANK5默认0X0700

对于SDRAM的访问,我们需要配置的就是图中阴影部分的:

-

MT:决定BANK外接的是SDRAM还是SRAM,SDRAM选择11.

-

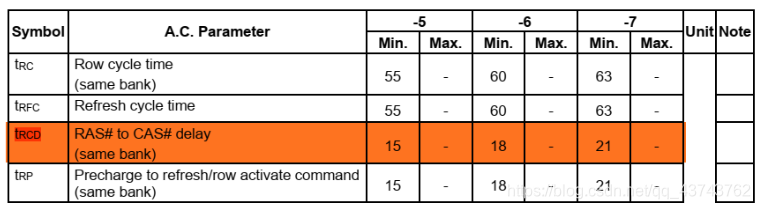

Trcd:行列信号之间的延迟时间,根据芯片手册得知最小为21ns,而我们的HCLK时钟为100MHz,一个clock10ns,所以保险起见选择30ns,即:01。

-

SCAN:设置列地址位,这里使用的SDRAM列地址一共9位,所以为:01.

所以,BANKCON6寄存器要或运算的值为:0x000180

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1209

1209

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?