目录

Flash扇区擦除

实现原理

扇区的概念

- Flash型号的数字代表容量,单位兆bit,如M25P16,此Flash的容量为16Mbit;

- Flash的内存大小,扇区大小,页大小在数据手册中可以查看;

- 每个扇区的地址范围在数据手册中给出, 地址中前两位是扇区地址,中间两位是页地址,后两位是字节地址;

- 扇区擦除即把选中的扇区全置为1,擦除的最小单位是扇区(不能进行页擦除)

扇区擦除步骤

- 在写入扇区擦除指令之前需要写入写使能指令WREN,写入时拉低片选信号,写入完成拉高片选信号,写入写使能指令后便会变为写锁存状态,在此状态下才能进行扇区擦除指令写入;

- 写入扇区擦除指令SE和三个字节的扇区地址(选中扇区的任意地址都可),通过MOSI端口写入指令,写入完成则将片选信号拉高,若不拉高,则此指令不会执行;

- 扇区擦除指令写入后要等待一个全擦除周期完成擦除操作,周期时间可查看数据手册中的

;

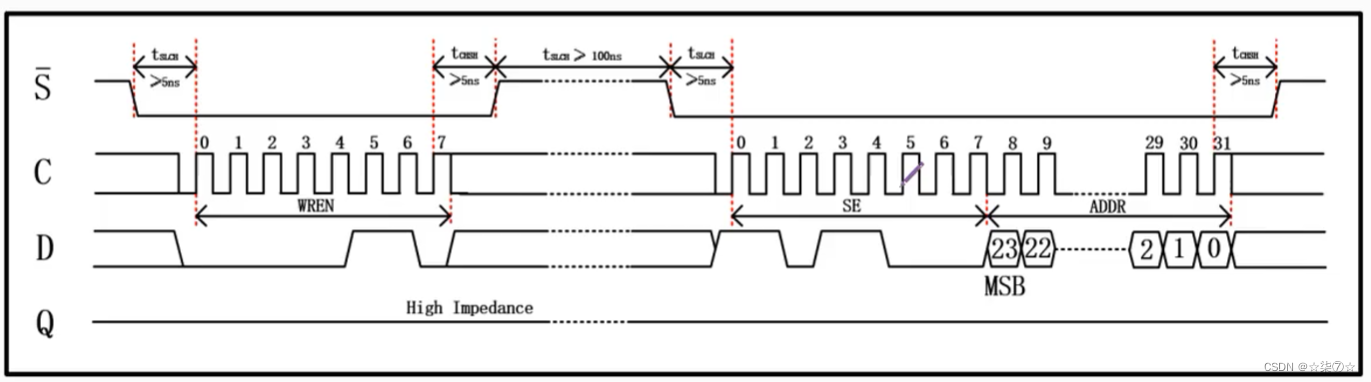

- 以上步骤需要遵循串行输入时序,可在数据手册中查看,见下图;

- 需要查看数据手册中Flash读写操作对时钟频率的要求;

注:与全擦除相比只是在写入的擦除指令不同和多了三个字节的扇区地址写入,见下图。

时序图中的表示也同全擦除一样,上一篇文章全擦除中已给出解释,这里不再给出。

verilog设计代码

module flash_se_ctrl

(

input wire sys_clk , //系统时钟,频率50MHz

input wire sys_rst_n , //复位信号,低电平有效

input wire key , //按键输入信号

output reg cs_n , //片选信号

output reg sck , //串行时钟

output reg mosi //主输出从输入数据

);

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//parameter define

parameter IDLE = 4'b0001 , //初始状态

WR_EN = 4'b0010 , //写状态

DELAY = 4'b0100 , //等待状态

SE = 4'b1000 ; //扇区擦除状态

parameter WR_EN_INST = 8'b0000_0110, //写使能指令

SE_INST = 8'b1101_1000; //扇区擦除指令

parameter SECTOR_ADDR = 8'b0000_0000, //扇区地址

PAGE_ADDR = 8'b0000_0100, //页地址

BYTE_ADDR = 8'b0010_0101; //字节地址

//reg define

reg [3:0] cnt_byte; //字节计数器

reg [3:0] state ; //状态机状态

reg [4:0] cnt_clk ; //系统时钟计数器

reg [1:0] cnt_sck ; //串行时钟计数器

reg [2:0] cnt_bit ; //比特计数器

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//cnt_clk:系统时钟计数器,用以记录单个字节

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_clk <= 5'd0;

else if(state != IDLE)

cnt_clk <= cnt_clk + 1'b1;

//cnt_byte:记录输出字节个数和等待时间

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_byte <= 4'd0;

else if((cnt_clk == 5'd31) && (cnt_byte == 4'd9))

cnt_byte <= 4'd0;

else if(cnt_clk == 31)

cnt_byte <= cnt_byte + 1'b1;

//cnt_sck:串行时钟计数器,用以生成串行时钟

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_sck <= 2'd0;

else if((state == WR_EN) && (cnt_byte == 1'b1))

cnt_sck <= cnt_sck + 1'b1;

else if((state == SE) && (cnt_byte >= 4'd5) && (cnt_byte <= 4'd8))

cnt_sck <= cnt_sck + 1'b1;

//cs_n:片选信号

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cs_n <= 1'b1;

else if(key == 1'b1)

cs_n <= 1'b0;

else if((cnt_byte == 4'd2) && (cnt_clk == 5'd31) && (state == WR_EN))

cs_n <= 1'b1;

else if((cnt_byte == 4'd3) && (cnt_clk == 5'd31) && (state == DELAY))

cs_n <= 1'b0;

else if((cnt_byte == 4'd9) && (cnt_clk == 5'd31) && (state == SE))

cs_n <= 1'b1;

//sck:输出串行时钟

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

sck <= 1'b0;

else if(cnt_sck == 2'd0)

sck <= 1'b0;

else if(cnt_sck == 2'd2)

sck <= 1'b1;

//cnt_bit:高低位对调,控制mosi输出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_bit <= 3'd0;

else if(cnt_sck == 2'd2)

cnt_bit <= cnt_bit + 1'b1;

//state:两段式状态机第一段,状态跳转

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

state <= IDLE;

else

case(state)

IDLE: if(key == 1'b1)

state <= WR_EN;

WR_EN: if((cnt_byte == 4'd2) && (cnt_clk == 5'd31))

state <= DELAY;

DELAY: if((cnt_byte == 4'd3) && (cnt_clk == 5'd31))

state <= SE;

SE: if((cnt_byte == 4'd9) && (cnt_clk == 5'd31))

state <= IDLE;

default: state <= IDLE;

endcase

//mosi:两段式状态机第二段,逻辑输出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

mosi <= 1'b0;

else if((state == WR_EN) && (cnt_byte == 4'd2))

mosi <= 1'b0;

else if((state == SE) && (cnt_byte == 4'd9))

mosi <= 1'b0;

else if((state == WR_EN) && (cnt_byte == 4'd1) && (cnt_sck == 5'd0))

mosi <= WR_EN_INST[7 - cnt_bit]; //写使能指令

else if((state == SE) && (cnt_byte == 4'd5) && (cnt_sck == 5'd0))

mosi <= SE_INST[7 - cnt_bit]; //扇区擦除指令

else if((state == SE) && (cnt_byte == 4'd6) && (cnt_sck == 5'd0))

mosi <= SECTOR_ADDR[7 - cnt_bit]; //扇区地址

else if((state == SE) && (cnt_byte == 4'd7) && (cnt_sck == 5'd0))

mosi <= PAGE_ADDR[7 - cnt_bit]; //页地址

else if((state == SE) && (cnt_byte == 4'd8) && (cnt_sck == 5'd0))

mosi <= BYTE_ADDR[7 - cnt_bit]; //字节地址

endmoduleverilog测试代码

module tb_flash_se_ctrl();

//wire define

wire cs_n;

wire sck ;

wire mosi ;

//reg define

reg sys_clk ;

reg sys_rst_n ;

reg key ;

//时钟、复位信号、模拟按键信号

initial

begin

sys_clk = 0;

sys_rst_n <= 0;

key <= 0;

#100

sys_rst_n <= 1;

#1000

key <= 1;

#20

key <= 0;

end

always #10 sys_clk <= ~sys_clk;

//写入Flash仿真模型初始值(全F)

defparam memory.mem_access.initfile = "initmemory.txt";

//------------- flash_se_ctrl_inst -------------

flash_se_ctrl flash_se_ctrl_inst

(

.sys_clk (sys_clk ), //系统时钟,频率50MHz

.sys_rst_n (sys_rst_n ), //复位信号,低电平有效

.key (key ), //按键输入信号

.sck (sck ), //串行时钟

.cs_n (cs_n ), //片选信号

.mosi (mosi ) //主输出从输入数据

);

//------------- memory -------------

m25p16 memory

(

.c (sck ), //输入串行时钟,频率12.5Mhz,1bit

.data_in (mosi ), //输入串行指令或数据,1bit

.s (cs_n ), //输入片选信号,1bit

.w (1'b1 ), //输入写保护信号,低有效,1bit

.hold (1'b1 ), //输入hold信号,低有效,1bit

.data_out ( ) //输出串行数据

);

endmodule

3379

3379

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?