1.编写verilog代码

命名为 encode83_module.v。

module bcd7seg(

input [3:0] b,

output reg [6:0] h

);

always @(*) begin

case (b)

4'b0000: h = 7'b0000001; // 显示 0

4'b0001: h = 7'b1001111; // 显示 1

4'b0010: h = 7'b0010010; // 显示 2

4'b0011: h = 7'b0000110; // 显示 3

4'b0100: h = 7'b1001100; // 显示 4

4'b0101: h = 7'b0100100; // 显示 5

4'b0110: h = 7'b0100000; // 显示 6

4'b0111: h = 7'b0001111; // 显示 7

4'b1000: h = 7'b0000000; // 显示 8

4'b1001: h = 7'b0000100; // 显示 9

default: h = 7'b1111111; // 其他情况,数码管不显示

endcase

end

endmodule

module encode83_module(

input [7:0] x,

input en,

output reg flag,

output reg [2:0] y,

output [6:0] seg

);

integer i;

wire [3:0] bcd = {1'b0, y};

bcd7seg seg0(bcd, seg);

always @(x or en) begin

if (en) begin

y = 0;

flag = 1'b0;

for( i = 0; i <= 7; i = i+1)

if(x[i] == 1) begin

y = i[2:0];

flag = 1'b1;

end

end

else begin

y = 0;

flag = 0;

end

end

endmodule

2.编写测试代码

命名为 tb_encode83_module.cpp。

#include <stdlib.h>

#include <stdio.h>

#include <unistd.h> // 添加usleep函数需要

#include <verilated.h>

#include "Vencode83_module.h" // Verilator生成的头文件

#include "nvboard.h" // NVBoard头文件

// NVBoard引脚绑定函数

static void nvboard_bind_all_pins(Vencode83_module* dut) {

nvboard_bind_pin(&dut->x, 8, SW7, SW6, SW5, SW4, SW3, SW2, SW1, SW0);

nvboard_bind_pin(&dut->en, 1, SW8);

nvboard_bind_pin(&dut->y, 3, LD2, LD1, LD0);

nvboard_bind_pin(&dut->flag, 1, LD4);

nvboard_bind_pin(&dut->seg, 7, SEG0A, SEG0B, SEG0C, SEG0D, SEG0E, SEG0F, SEG0G);

}

int main(int argc, char** argv, char** env) {

// 初始化NVBoard

nvboard_init();

// 初始化Verilator

Verilated::commandArgs(argc, argv);

Vencode83_module *dut = new Vencode83_module;

// 绑定NVBoard引脚

nvboard_bind_all_pins(dut);

// 主仿真循环

while (1) {

// 更新NVBoard输入状态

nvboard_update();

// 评估模型

dut->eval();

// 添加小延迟以减少CPU占用

usleep(10000); // 10ms

}

// 清理(通常不会执行到这里)

nvboard_quit();

delete dut;

return 0;

}

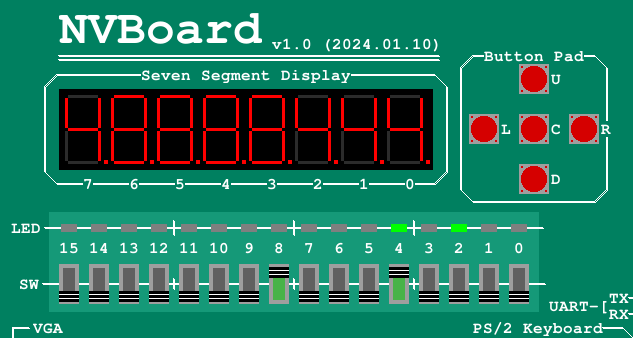

3.引脚绑定

命名为 top.nxdc 。

top = encode83_module

x (SW7, SW6, SW5, SW4, SW3, SW2, SW1, SW0)

en SW8

y (LD2, LD1, LD0)

flag LD4

seg (SEG0A, SEG0B, SEG0C, SEG0D, SEG0E, SEG0F, SEG0G)

//seg1 (SEG1A, SEG1B, SEG1C, SEG1D, SEG1E, SEG1F, SEG1G) 同理可以用前面第1~7个数码管显示4.编写Makefile

TOPNAME = encode83_module

NXDC_FILES = constr/top.nxdc #约束文件路径

INC_PATH ?= #?=的意义是,INC_PATH如果被未被定义,则为?=后的值,如果被定义过,则保持原来的值

VERILATOR = verilator

VERILATOR_CFLAGS += -MMD --build -cc \

-O3 --x-assign fast --x-initial fast --noassert

BUILD_DIR = ./build

OBJ_DIR = $(BUILD_DIR)/obj_dir #OBJ_DIR = ./build/obj_dir

BIN = $(BUILD_DIR)/$(TOPNAME) #BIN = ./build/top

default: $(BIN) #终极目标为default,依赖./build/top

$(shell mkdir -p $(BUILD_DIR))

# constraint file

SRC_AUTO_BIND = $(abspath $(BUILD_DIR)/auto_bind.cpp)

$(SRC_AUTO_BIND): $(NXDC_FILES)

python3 ${NVBOARD_HOME}/scripts/auto_pin_bind.py $^ $@

# project source

VSRCS = $(shell find $(abspath ./vsrc) -name "*.v")

# 在vsrc目录中寻找所有的.v文件,并保存在变量VSRCS中

CSRCS = $(shell find $(abspath ./csrc) -name "*.c" -or -name "*.cc" -or -name "*.cpp")

# 在csrc目录中寻找所有的.c/.cc/.cpp文件,并保存在变量CSRCS中

CSRCS += $(SRC_AUTO_BIND)

# 将auto_bind.cpp文件,追加在变量CSRCS中

# rules for NVBoard

NVBOARD_HOME ?= /home/zjc/.ssh/ysyx-workbench/nvboard

export NVBOARD_HOME

include $(NVBOARD_HOME)/scripts/nvboard.mk

# 包含NVBoard相关Makelile规则

# rules for verilator

INCFLAGS = $(addprefix -I, $(INC_PATH))

CXXFLAGS += $(INCFLAGS) -DTOP_NAME="\"V$(TOPNAME)\""

CXXFLAGS += -I$(NVBOARD_HOME)/include \

-I$(NVBOARD_HOME)/usr/include \

-DUSE_NVBOARD \

-DNVBOARD_UPDATE=nvboard_update

LDFLAGS += -L$(NVBOARD_HOME)/build -l:nvboard.a

LDFLAGS += -lSDL2 -lSDL2_image -lSDL2_ttf

$(BIN): $(VSRCS) $(CSRCS) $(NVBOARD_ARCHIVE)

@rm -rf $(OBJ_DIR) # 生成新的对象之前,删除旧的对象文件

$(VERILATOR) $(VERILATOR_CFLAGS) \

--top-module $(TOPNAME) $^ \

$(addprefix -CFLAGS , $(CXXFLAGS)) $(addprefix -LDFLAGS , $(LDFLAGS)) \

--Mdir $(OBJ_DIR) --exe -o $(abspath $(BIN))

all: default

run: $(BIN)

@$^

clean:

rm -rf $(BUILD_DIR)

.PHONY: default all clean run

5.运行后生成的引脚绑定代码

#include <nvboard.h>

#include "Vencode83_module.h"

void nvboard_bind_all_pins(Vencode83_module* top) {

nvboard_bind_pin( &top->x, 8, SW7, SW6, SW5, SW4, SW3, SW2, SW1, SW0);

nvboard_bind_pin( &top->en, 1, SW8);

nvboard_bind_pin( &top->y, 3, LD2, LD1, LD0);

nvboard_bind_pin( &top->flag, 1, LD4);

nvboard_bind_pin( &top->seg, 7, SEG0A, SEG0B, SEG0C, SEG0D, SEG0E, SEG0F, SEG0G);

}

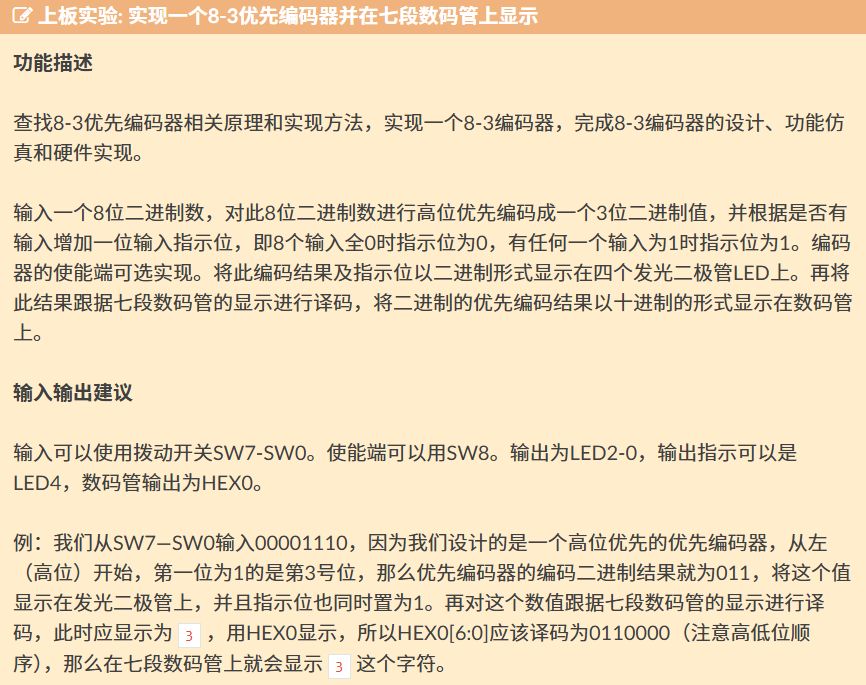

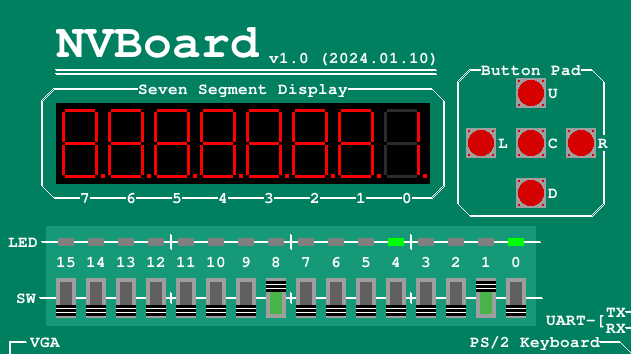

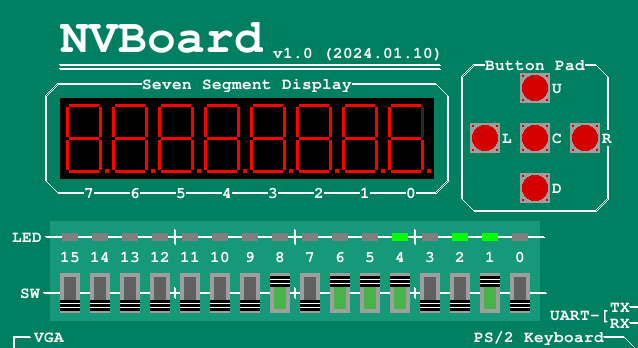

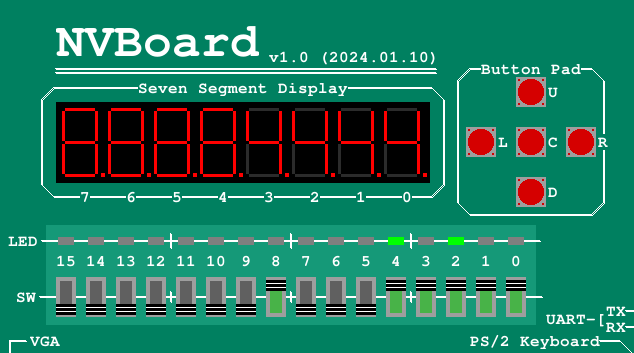

6.结果展示

同理可以在其他数码管显示。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?