在dramsim2的ini文件夹里有许多现成的DRAM参数文件,包含了DRAM芯片的容量、延时和功耗参数,下面用DDR3_micron_32M_8B_x8_sg15.ini文件来举例,批注写在文件内:

NUM_BANKS=8<span style="white-space:pre"> </span>

NUM_ROWS=32768<span style="white-space:pre"> </span>;行*列=32M,这就是文件名32M的由来

NUM_COLS=1024

DEVICE_WIDTH=8<span style="white-space:pre"> </span>;一块DRAM芯片的数据总线宽度8位,而根据DDR3定义,JEDEC_DATA_BUS_BITS=64,组成的一个rank宽度64,所以一个rank需要8块DRAM芯片并联构成

;根据上面的参数,可以计算得到由这种DRAM芯片构成的一个rank容量为:8banks * 32768rows * 1024cols * 8bit * 8chips = 2GB,而运行dramsim2得到的默认输出文件为:;2GB.1Ch.1R.scheme2.open_page.32TQ.32CQ.RtB.pRank.vis

;in nanoseconds

;#define REFRESH_PERIOD 7800

REFRESH_PERIOD=7800<span style="white-space:pre"> </span>;refresh指令发送周期,单位ns。JEDEC DDR3默认的刷新指令发送周期即7.8us,并且需要满足要求64ms刷新全部行,因此一次刷新的行数为: 32768 * 7.8us / 64ms = 4行。如果要增加行数但保持REFRESH_PERIOD不变,则必须增加每次刷新花费的时间tRFC(可以粗略估计为等比例增长)

tCK=1.5 ;*<span style="white-space:pre"> </span>;DRAM工作时钟周期,单位ns

;以下是时间参数,单位为cycle。

CL=10 ;*<span style="white-space:pre"> </span>;CAS指令到从buffer读出数据的时间

AL=0 ;*<span style="white-space:pre"> </span>;从DDR2起,RAS指令后可以马上接CAS指令,但比起传统的RAS后等tRCD再发送CAS的方式,数据能够从阵列中读出的延时并不能间断,AL就是用来表征这段额外延时

;AL=3; needs to be tRCD-1 or 0<span style="white-space:pre"> </span>;如果采取RAS指令马上接CAS指令的方式,AL=tRCD-1,如果等tRCD再接CAS指令,则不用计算AL

;RL=(CL+AL)

;WL=(RL-1)

BL=8 ;*<span style="white-space:pre"> </span>;burst length

tRAS=24;* <span style="white-space:pre"> </span>;RAS指令持续时间

tRCD=10 ;*<span style="white-space:pre"> </span>;传统RAS后需要等待tRCD才能发送CAS

tRRD=4 ;*<span style="white-space:pre"> </span>;RAS和RAS最短间隔(不同bank)

tRC=34 ;*<span style="white-space:pre"> </span>;同一bank RAS和RAS最短间隔

tRP=10 ;*<span style="white-space:pre"> </span>;precharge时间

tCCD=4 ;*<span style="white-space:pre"> </span>;CAS和CAS最短间隔

tRTP=5 ;*<span style="white-space:pre"> </span>;read to precharge

tWTR=5 ;*<span style="white-space:pre"> </span>;write to read

tWR=10 ;*<span style="white-space:pre"> </span>;写到阵列时间

tRTRS=1; -- RANK PARAMETER, TODO

tRFC=107;*<span style="white-space:pre"> </span>;刷新指令执行时间

tFAW=20;*<span style="white-space:pre"> </span>;Four (row) bank Activation Window

tCKE=4 ;*<span style="white-space:pre"> </span>;CKE持续时间

tXP=4 ;*<span style="white-space:pre"> </span>

tCMD=1 ;*

;以下为DRAM单芯片电流参数,单位mA

IDD0=130;<span style="white-space:pre"> </span>;反复RAS precharge的平均电流

IDD1=155;<span style="white-space:pre"> </span>;没用到

IDD2P=10;<span style="white-space:pre"> </span>;CKE无效,全部bank precharge静态电流

IDD2Q=70;<span style="white-space:pre"> </span>;没用到

IDD2N=70;<span style="white-space:pre"> </span>;CKE有效,全部bank precharge静态电流

IDD3Pf=60;<span style="white-space:pre"> </span>;CKE无效,有bank open静态电流

IDD3Ps=60;<span style="white-space:pre"> </span>;跟上面似乎没区别

IDD3N=90;<span style="white-space:pre"> </span>;CKE有效,有bank open静态电流

IDD4W=300;<span style="white-space:pre"> </span>:写时电流

IDD4R=255;<span style="white-space:pre"> </span>;读时电流

IDD5=305;<span style="white-space:pre"> </span>;刷新时电流

IDD6=9;<span style="white-space:pre"> </span>;没用到

IDD6L=12;<span style="white-space:pre"> </span>;没用到

IDD7=460;<span style="white-space:pre"> </span>;没用到

;same bank

;READ_TO_PRE_DELAY=(AL+BL/2+max(tRTP,2)-2)

;WRITE_TO_PRE_DELAY=(WL+BL/2+tWR)

;READ_TO_WRITE_DELAY=(RL+BL/2+tRTRS-WL)

;READ_AUTOPRE_DELAY=(AL+tRTP+tRP)

;WRITE_AUTOPRE_DELAY=(WL+BL/2+tWR+tRP)

;WRITE_TO_READ_DELAY_B=(WL+BL/2+tWTR);interbank

;WRITE_TO_READ_DELAY_R=(WL+BL/2+tRTRS-RL);interrank

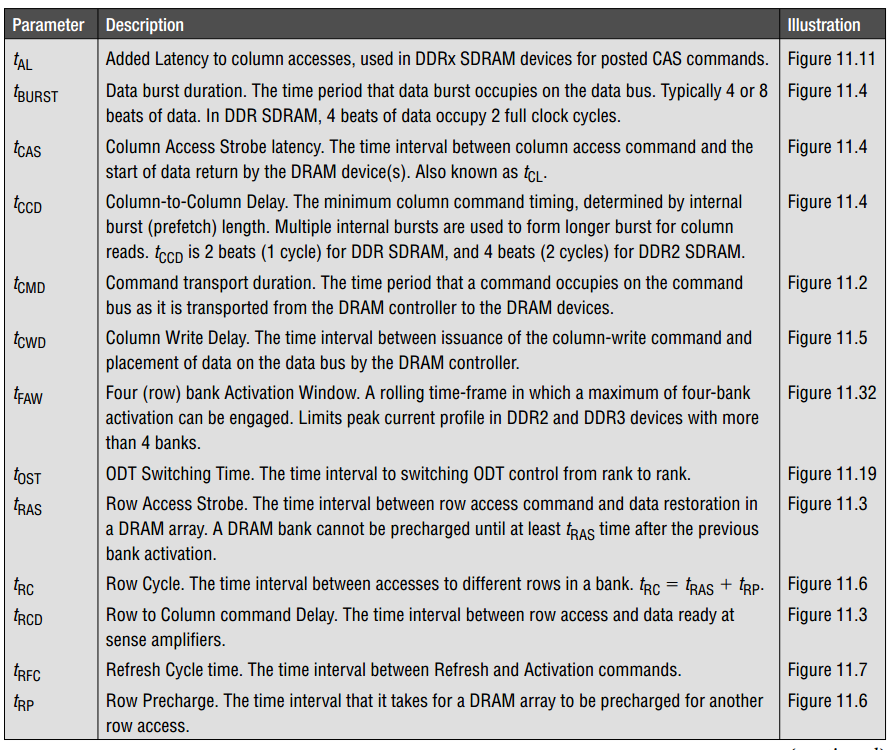

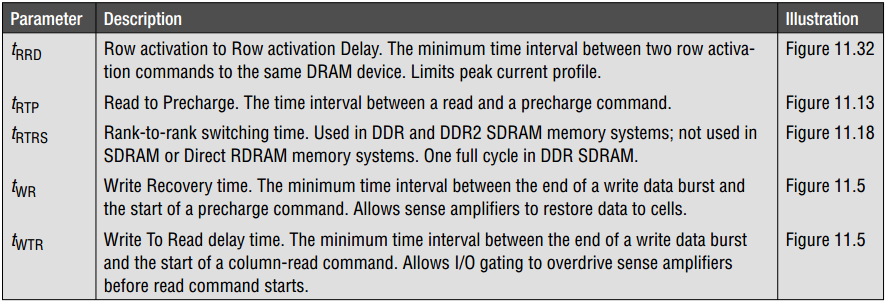

Vdd=1.5 ; TODO: double check this关于详细的DDR3时序参数,可以参考以下表格(出自《Memory: Systems, Cache, DRAM, Disk》):

关于DDR3电流与功耗计算,可以参考micron的《TN-41-01: Calculating Memory System Power for DDR3》

要了解DRAMSIM2具体延时和功耗的计算方法,可以在MemoryController.cpp中查看源代码

4246

4246

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?