Spi子系统

spi协议简介

SPI是串行外设接口(Serial Peripheral Interface)的缩写,是美国摩托罗拉公司(Motorola)最先推出的一种同步串行传输规范,是一种高速、全双工、同步通信总线,所以可以在同一时间发送和接收数据,SPI没有定义速度限制,因此一般的存储设备(flash、sd卡)也使用spi通信。

SPI有主、从两种模式,通常由一个主模块和一个或多个从模块组成(SPI不支持多主机),主模块选择一个从模块进行同步通信,从而完成数据的交换。提供时钟的为主设备(Master),接收时钟的设备为从设备(Slave),SPI接口的读写操作,都是由主设备发起,当存在多个从设备时,通过各自的片选信号进行管理。

SPI通信原理很简单,需要至少4根线,单向传输时3根线,它们是MISO(主设备数据输入)、MOSI(主设备数据输出)、SCLK(时钟)和CS/SS(片选):

MISO( Master Input Slave Output):主设备数据输入,从设备数据输出;

MOSI(Master Output Slave Input):主设备数据输出,从设备数据输入;

SCLK(Serial Clock):时钟信号,由主设备产生;

CS/SS(Chip Select/Slave Select):从设备使能信号,由主设备控制,一主多从时,CS/SS是从芯片是否被主芯片选中的控制信号,只有片选信号为预先规定的使能信号时(高电位或低电位),主芯片对此从芯片的操作才有效。但是在某些点对点的通信中,可能不需要片选信号。

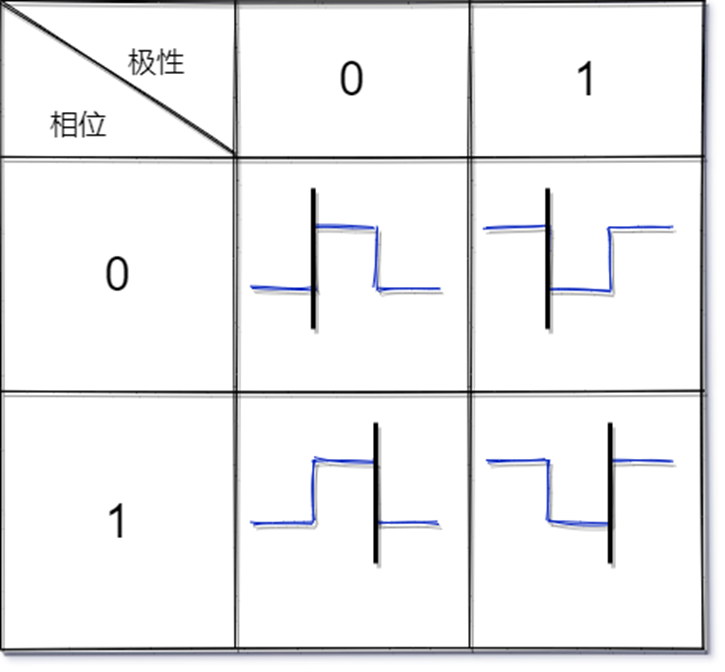

根据SPI的时钟极性和时钟相位特性可以设置4种不同的SPI通信操作模式,其中模式0和模式3最常用。

Mode0:CKP=0,CKE =0:当空闲态时,SCK处于低电平,数据采样是在第1个边沿,也就是SCK由低电平到高电平的跳变,所以数据采样是在上升沿(准备数据),(发送数据)数据发送是在下降沿。

Mode1:CKP=0,CKE=1:当空闲态时,SCK处于低电平,数据发送是在第2个边沿,也就是SCK由低电平到高电平的跳变,所以数据采样是在下降沿,数据发送是在上升沿。

Mode2:CKP=1,CKE=0:当空闲态时,SCK处于高电平,数据采集是在第1个边沿,也就是SCK由高电平到低电平的跳变,所以数据采集是在下降沿,数据发送是在上升沿。

Mode3:CKP=1,CKE=1:当空闲态时,SCK处于高电平,数据发送是在第2个边沿,也就是SCK由高电平到低电平的跳变,所以数据采集是在上升沿,数据发送是在下降沿。

Spi总线没有规定传输速率,只要通信时钟不超过设备datsheet上支持的时钟范围即可,spi也没有规定是lsb还是msb,一般主设备两种都支持,可配置,但是从设备一般只支持其中一种,因此需要根据从设备支持的模式去配置主设备。

关于spi全双工通信的理解

Spi通信并非一问一答的方式,因此数据的交换可以同时发生。如果通信双方是一问一答(查询的方式),则主机先发送查询的信息,然后再发起一次读操作产生时钟,此时从机的数据从数据寄存器移位到数据线上向从机发送数据。

如何根据示波器判断信号质量的好坏

Spi对数据的采样发生在跳变沿(根据上升沿或者下降沿),因此要在时钟的跳变沿,数据线上的电平必须是稳定的电平状态(不能处于一个上升或者下降的状态)。

关于spi从设备不能产生时钟,如何与主设备通信的理解。

时钟线时钟由之设备控制,对于从设备来说,时钟线就是一个输入,而spi的数据交换依赖于时钟,因此只有主设备必须发起一个读写操作,从设备的数据才能发送出去。

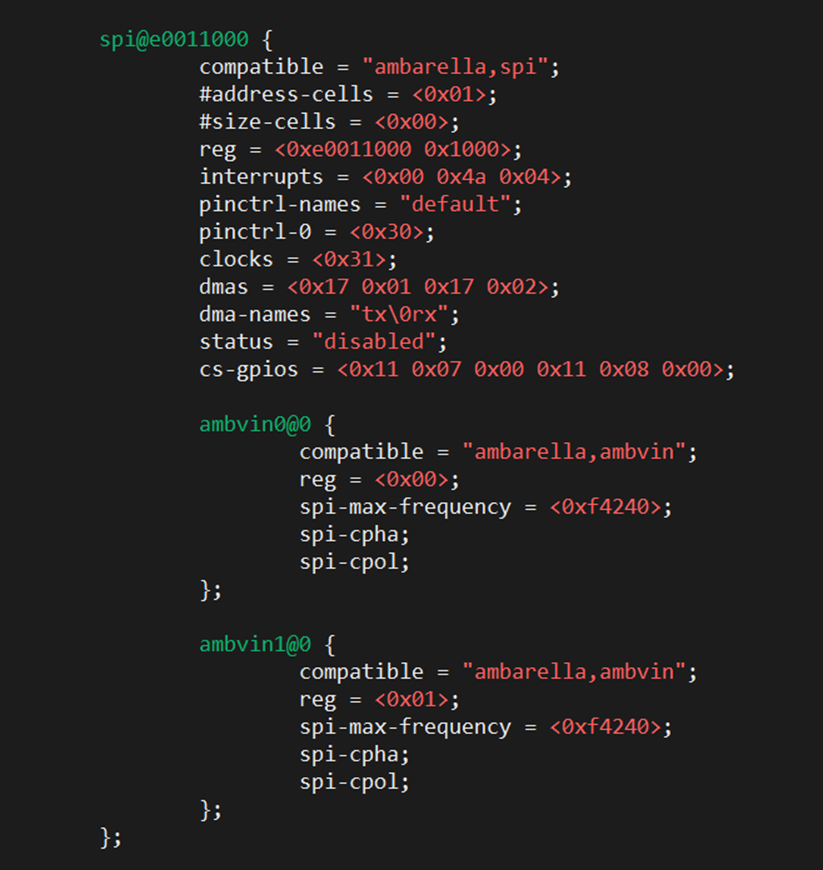

spi子系统与设备树

2.1 设备树中各个属性的含义

compatible:设备兼容属性,用于与设备绑定;

reg:表明spi控制器的基地址以及地址长度;

interrupt:表明控制器使用的中断资源;

pinctrl-name:定义设备的状态(休眠、唤醒等);

pinctrl-0/1/2:使用一组pin对应pinctrl-name定义的状态;

clock:使用的时钟源;

dma:表明控制器使用的dma控制器资源;

status:控制器状态

ambvin:子节点,表明挂载在这个总线下的设备。

cs-gpios:表明使用的cs-pin

2.2设备树与驱动

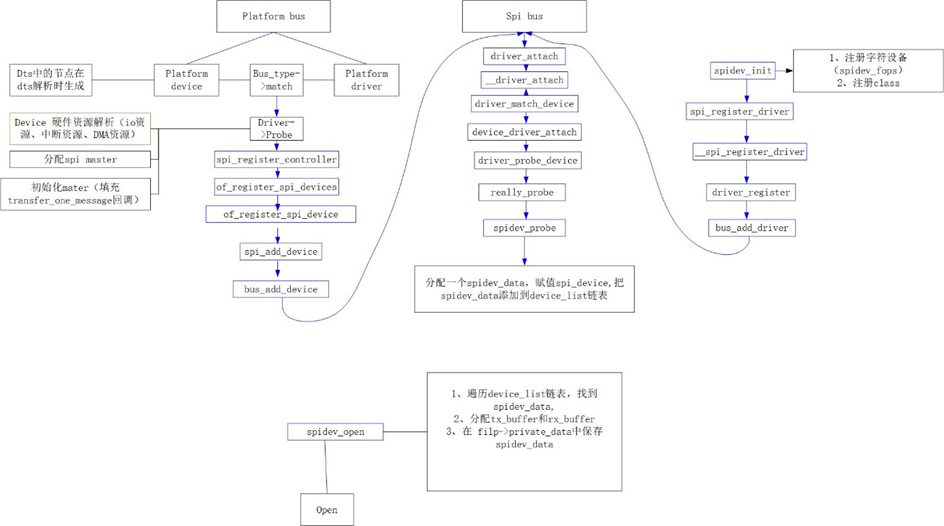

simple-bus下面的子节点会被解析成一个platform-device然后注册到platform-bus中,控制器驱动会被当成一个platform-driver注册到platform-bus中,然后通过compatible属性匹配上了之后,进入到对应的probe函数中,实现控制器的初始化。在spi控制器的子节点也会被解析成一个device注册到spi-bus中,等待对应的drive匹配。

Linux的spi子系统框架分析

879

879

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?