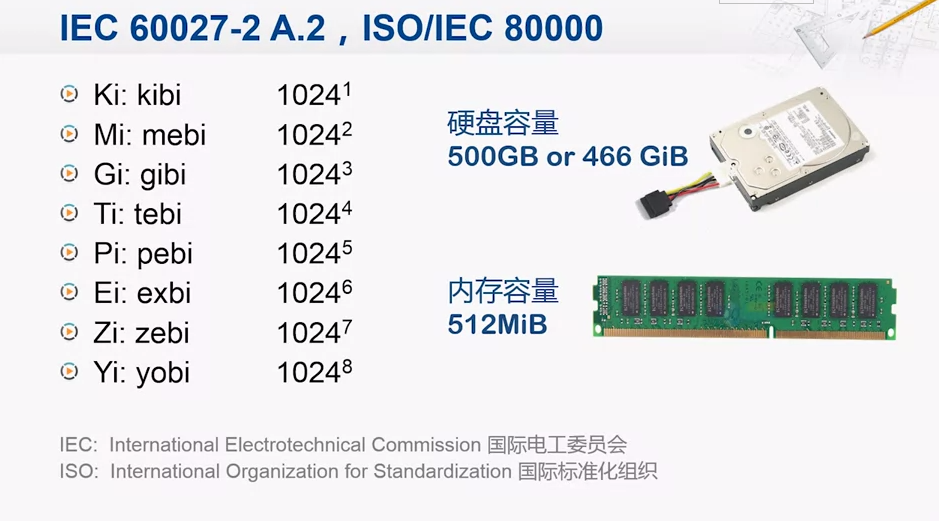

1. 首先科普下 Mbps

Mbps=Mbit/s即兆比特每秒。Million bits per second的缩写

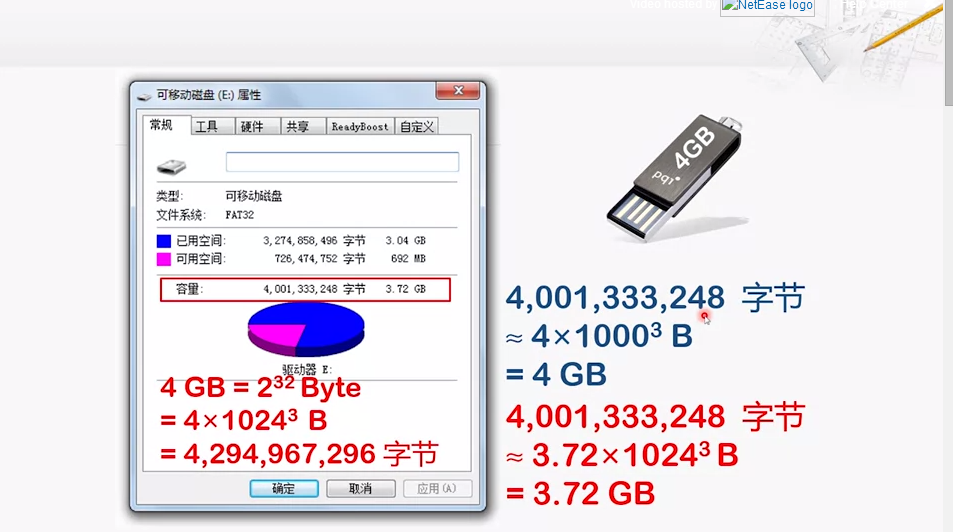

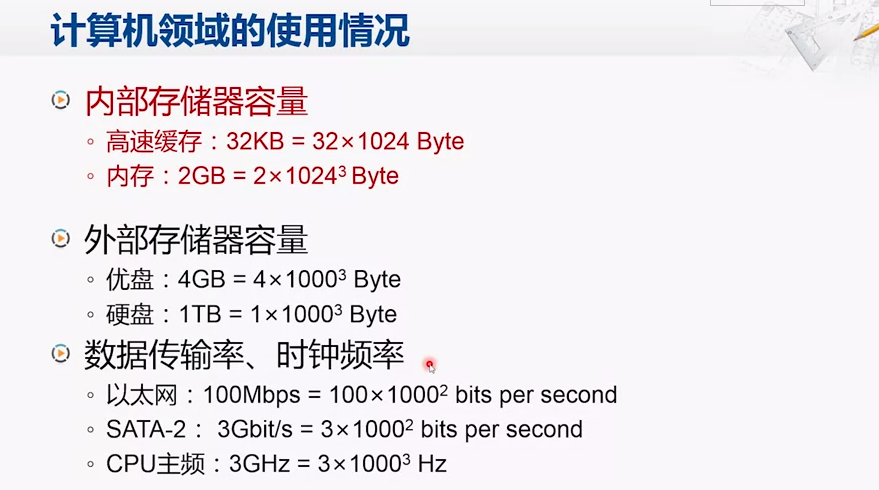

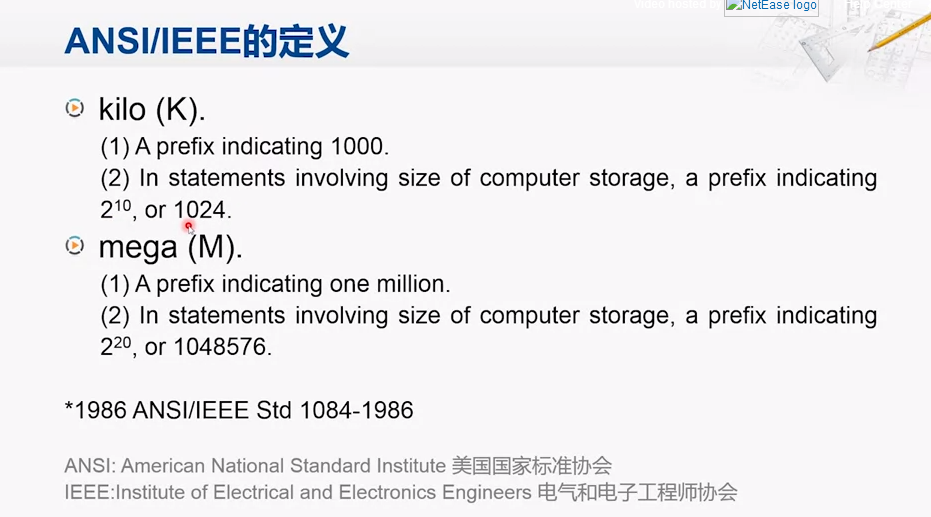

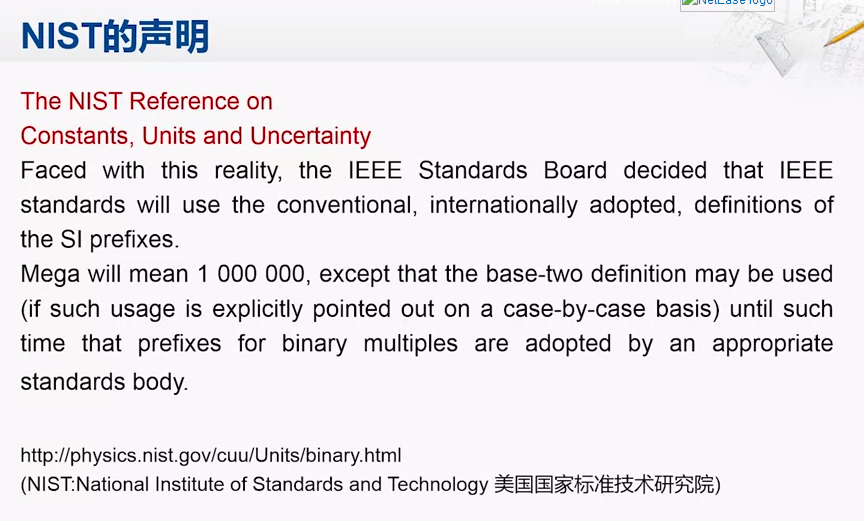

传输速率是指设备的的数据交换能力,也叫“带宽”,单位是Mbps(兆位/秒),目前主流的集线器带宽主要有10Mbps、54Mbps/100Mbps自适应型、100Mbps和150Mbps四种。1Mbps代表每秒传输1,048,576位,即每秒传输的数据量为:1,048,576/8=128K字节/秒=131072字节/秒

注意:

字母大小写的区别,小写b代表bit,大写B代表Byte,不能混用;Mbps缩写中严格限定M为大写,b、p、s为小写

常用单位还有Kbps 、Mbps 、Gbps(同样K、M、G严格限定为大写,参见KB)

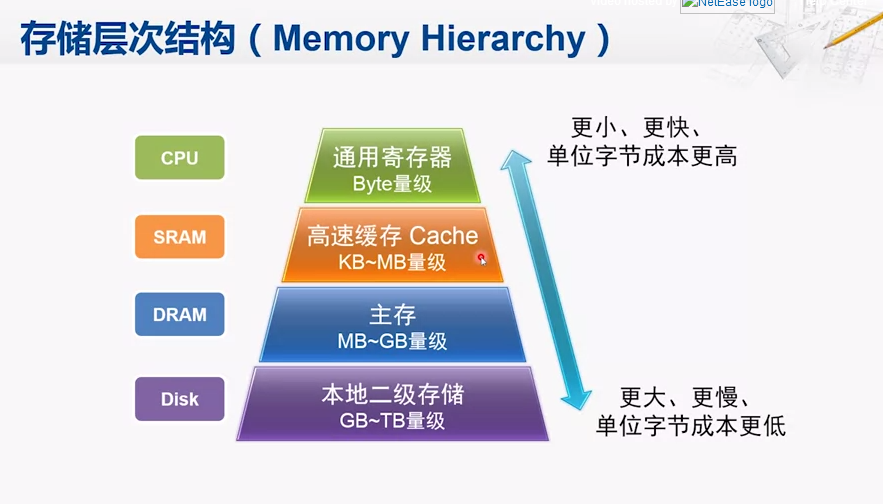

2. 高速缓存

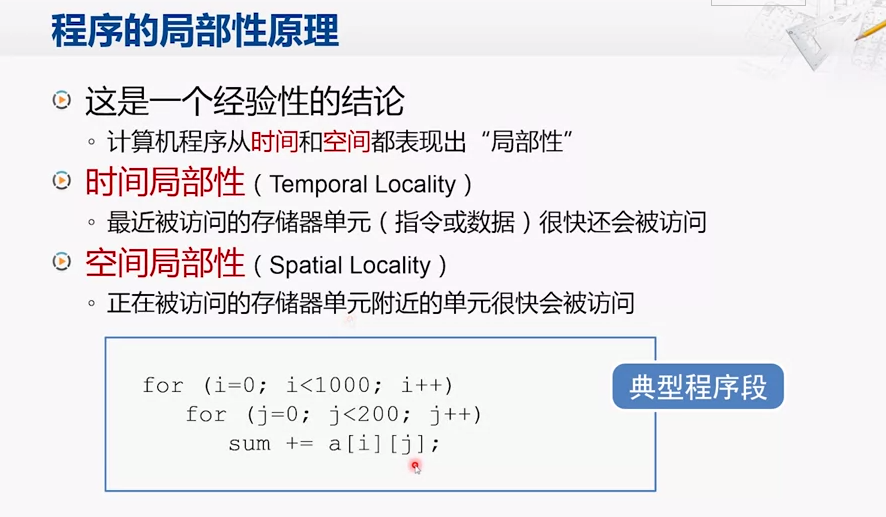

计算机运行程序的一个特点:

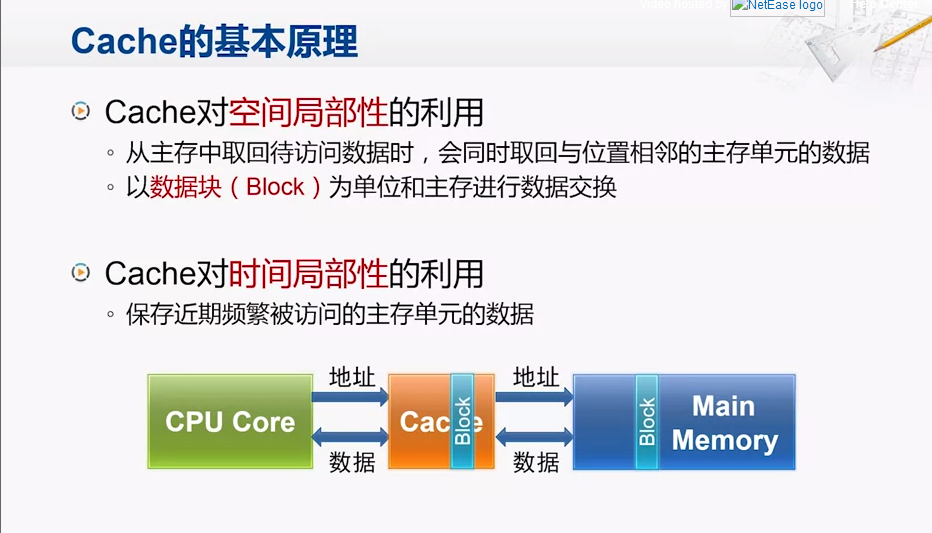

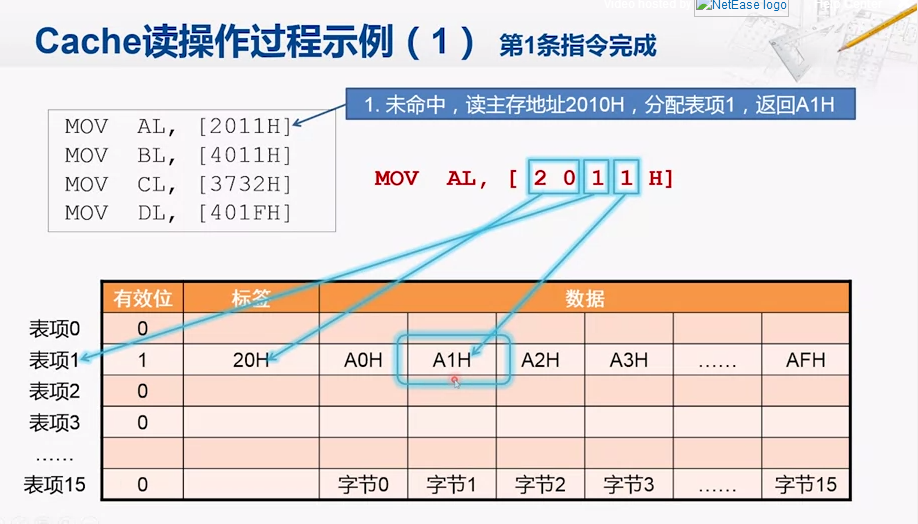

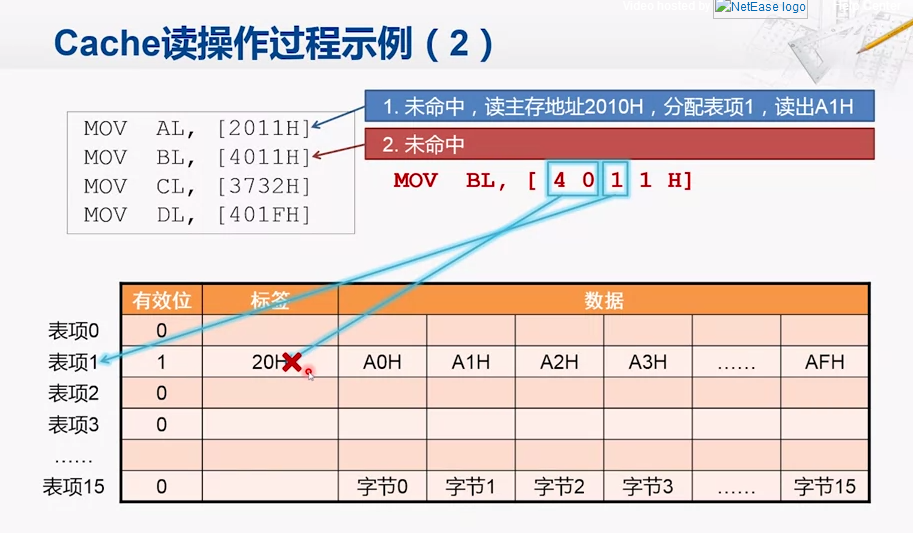

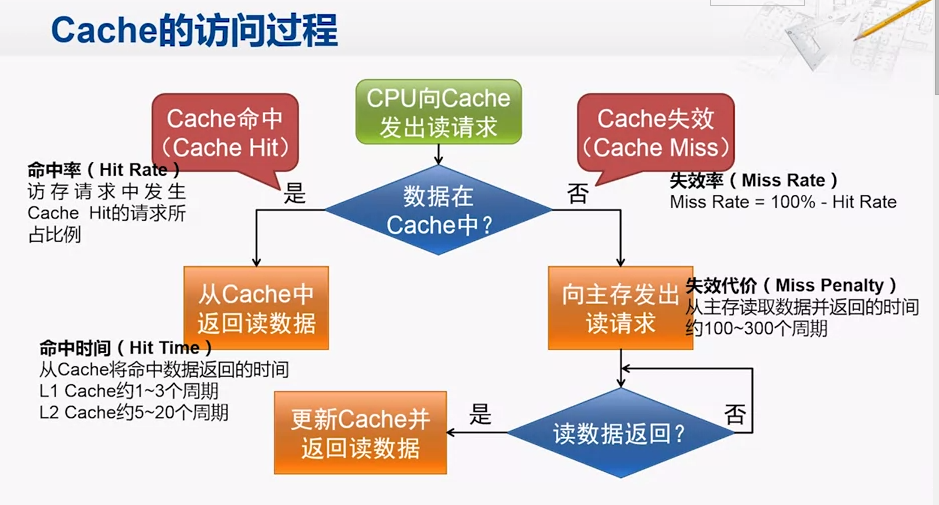

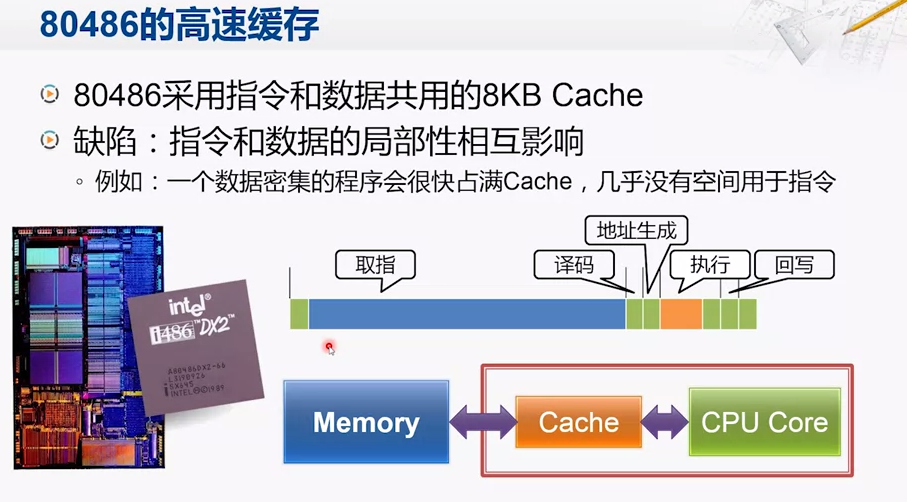

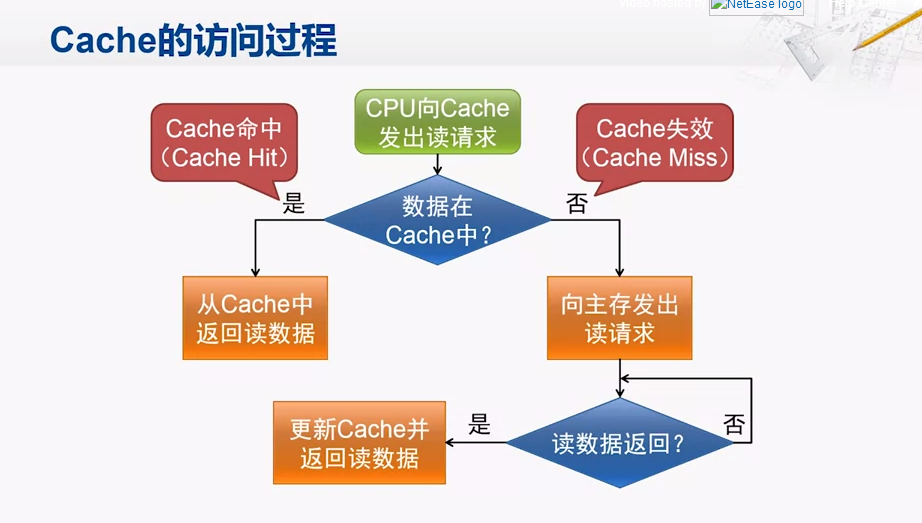

cache就是利用了程序的局部性原理设计出来的, 当CPU访问主存时 , 实际上是把地址发给了cache , 最开始cache里面是没有数据的 , 所以cache会把地址发给主存 , 然后在主存中取出对应的数据 , 这些都是用计算机硬件完成的

cache 主要组成 SRAM 和逻辑控制电路

3. 高速缓存的组织结构

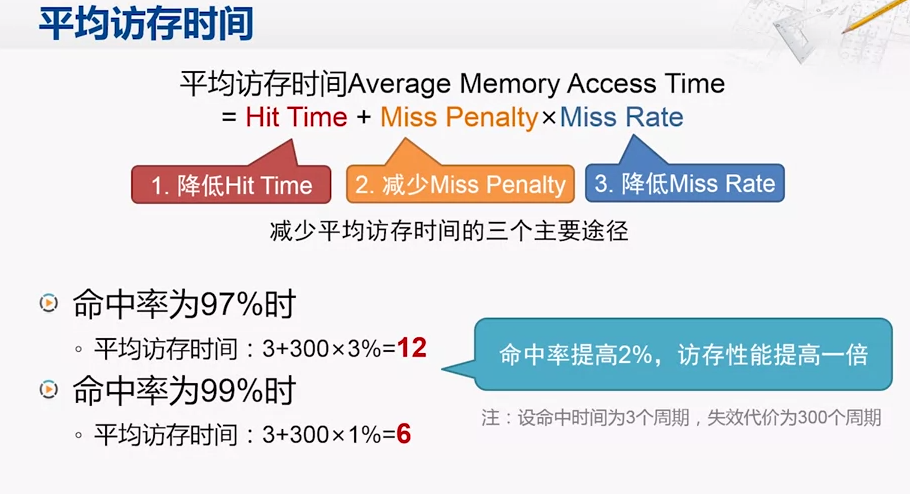

评价访存性能:

所以对于现在的cache来说 , 能够提高一点的命中率就能很好的性能提升

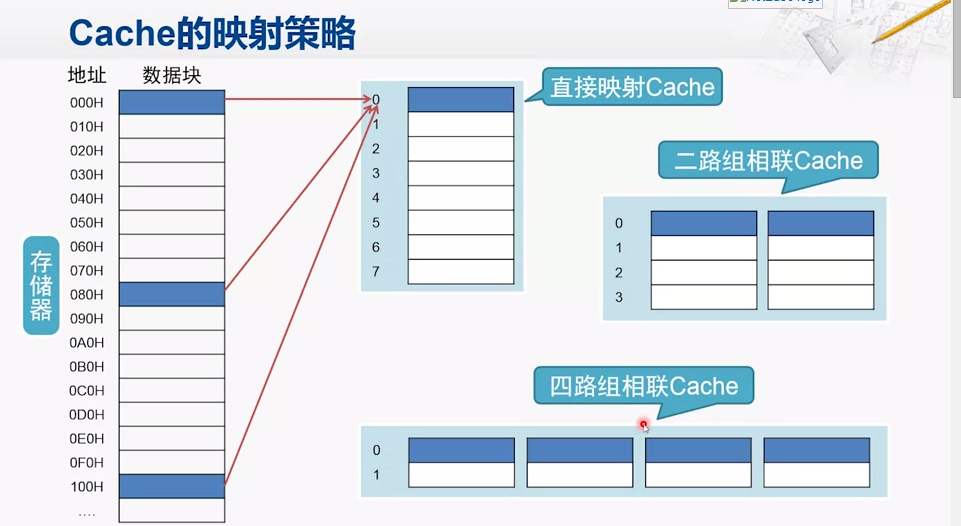

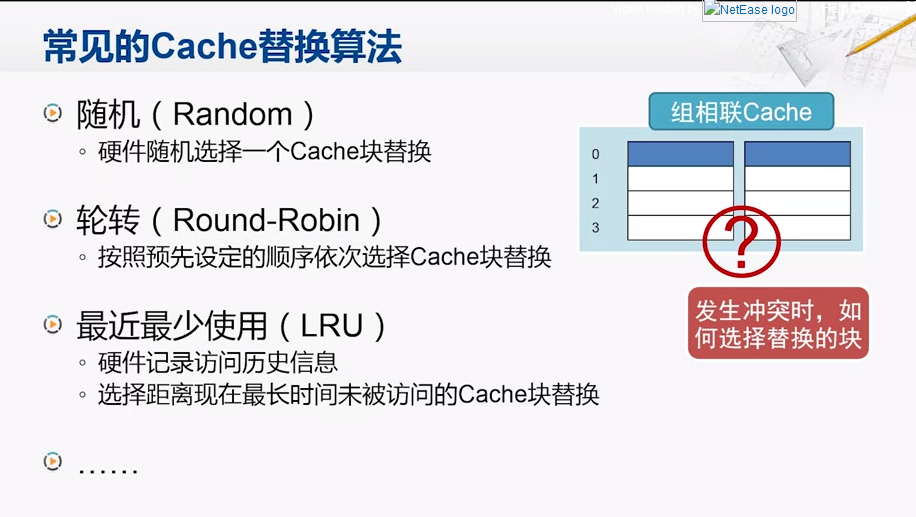

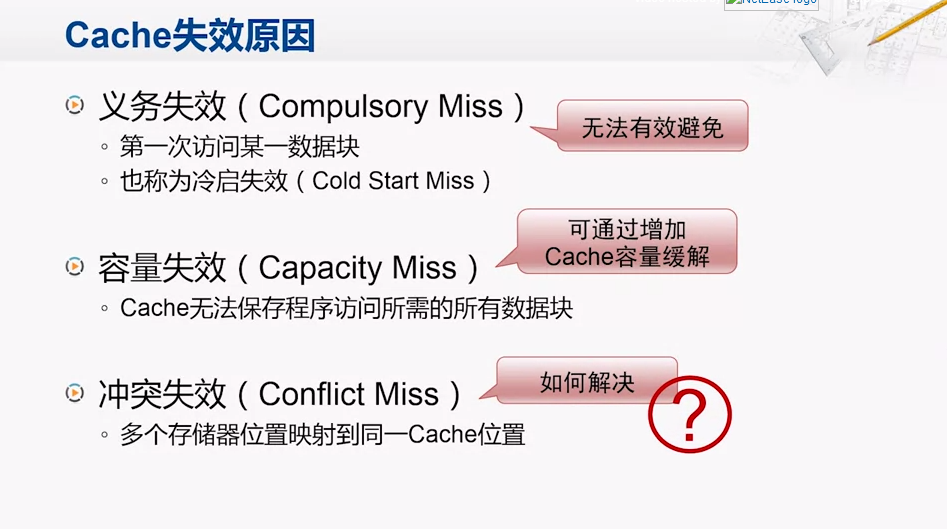

如何解决冲突失效????

当如图的 三个地址 , 如果系统不断地访问如图三个数据块 , 这样cache每次都没有命中 , 不如没有cache . 产生二路组相联cache

,取所有标签进行比较 , 这样在多路组相联的cache灵活性虽然高,但是控制逻辑电路很复杂 , 既增加了延迟又增加了功耗 , 如果划分的路数过多 ,虽然可能降低了失效率 , 但增加了命中时间 , 这样得不偿失了 . 而且也不一定能降低失效率 , 因为在多路组相联的cache当中 , 同一个数据块可以放在不同的地方 , 但如果这些地方都被占用了, 就要选择一行替换出去 , 这个替换算法好不好 , 就会对性能有很大影响 . 最近最少使用算法 表现性能比较好 , 但其硬件的设计也相当的复杂 , 所以映射策略和替换算法都会在性能和实现代价之间进行权衡

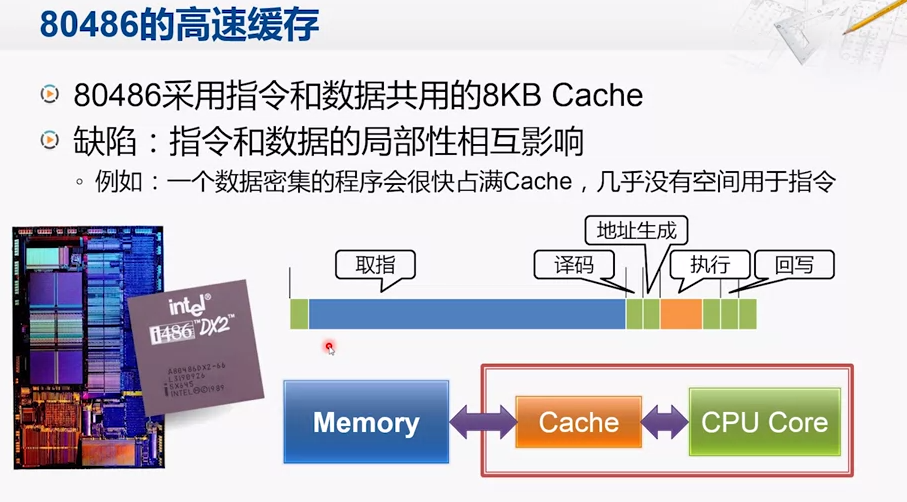

cache设计的实例

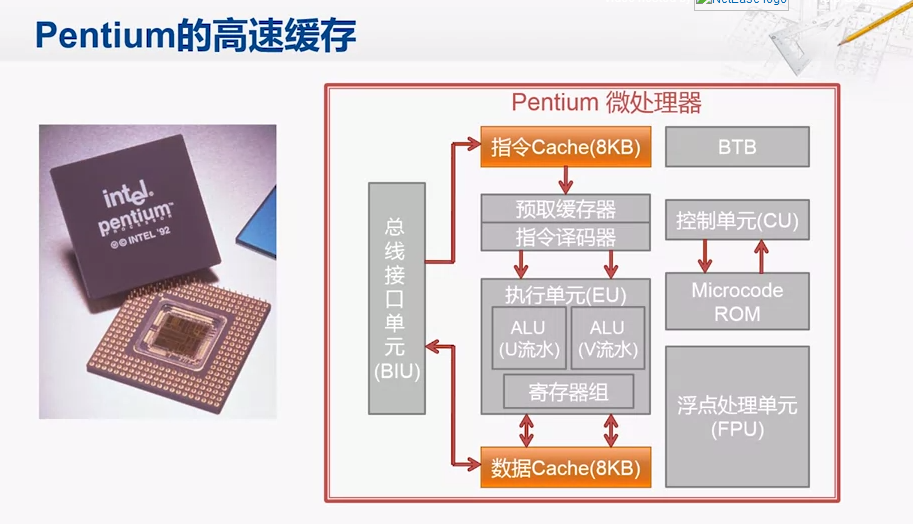

所以奔腾就把指令和数据分成两个独立的cache, 这样局部性就不会相互影响了 , 现在大多数CPU的一级cache都会采用这样的形式

4617

4617

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?