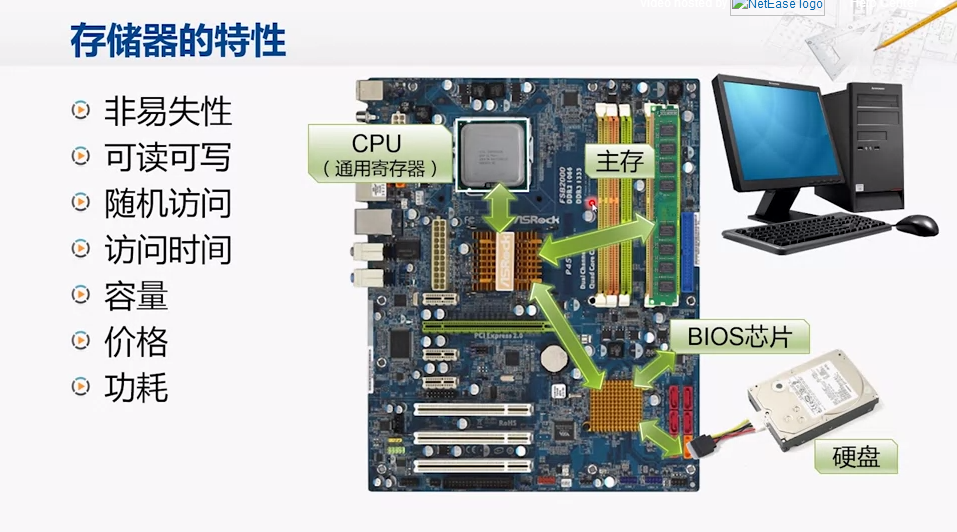

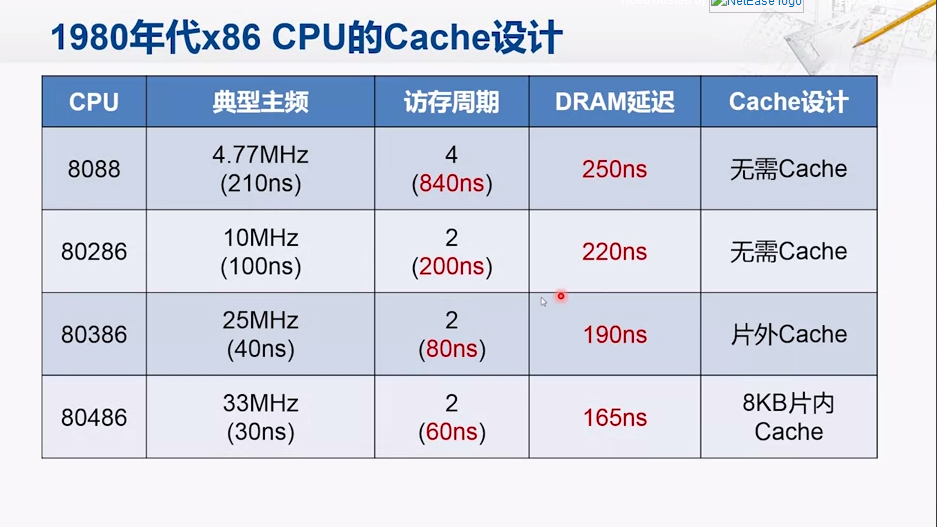

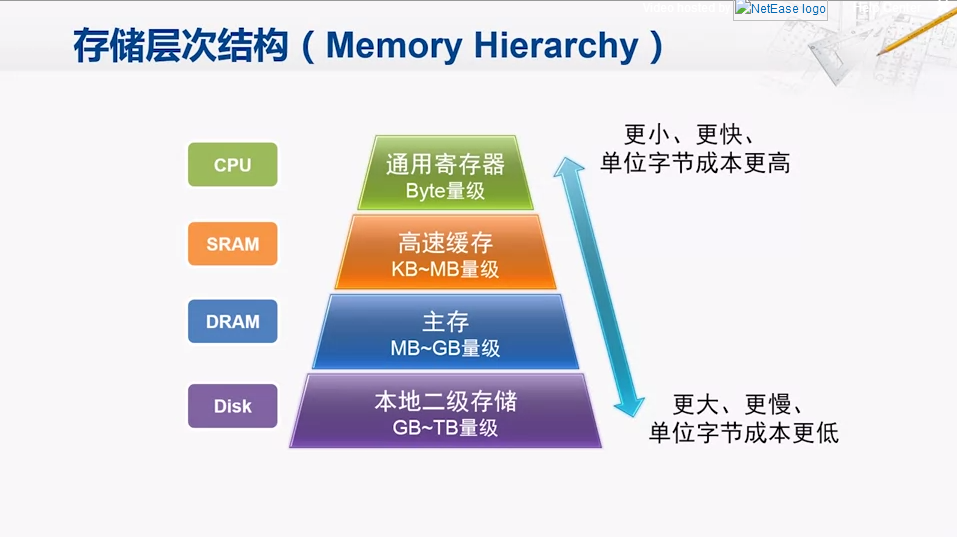

1. 存储结构概况

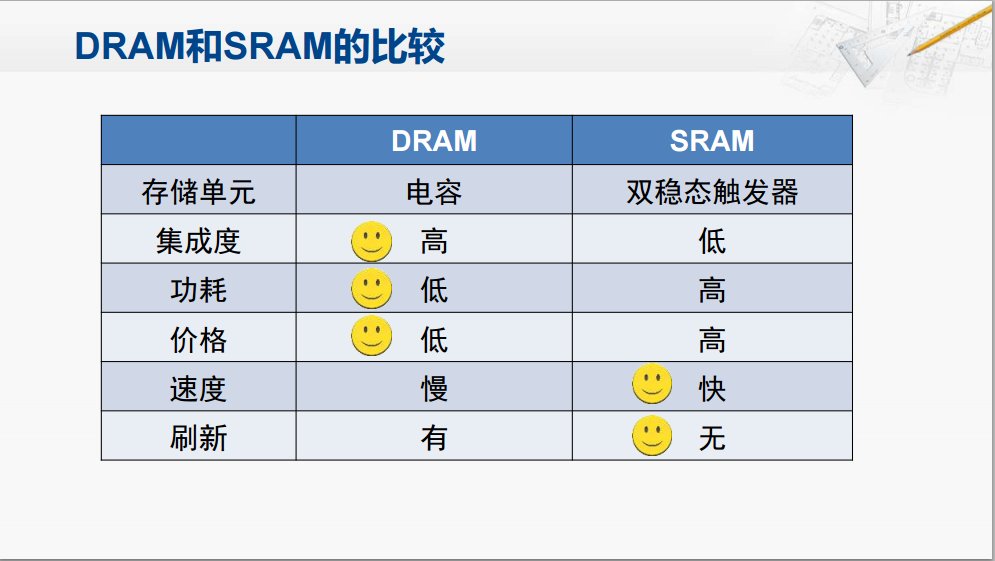

2. DRAM和SRAM

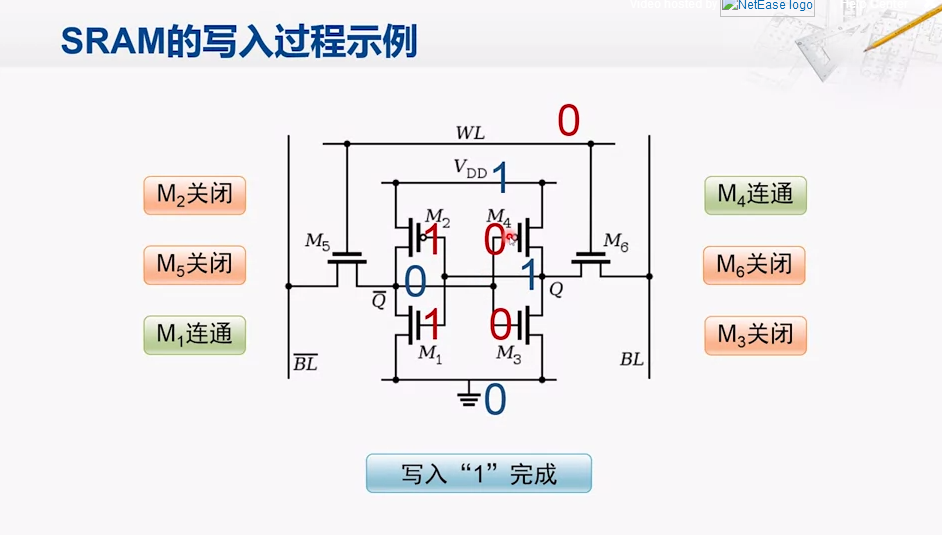

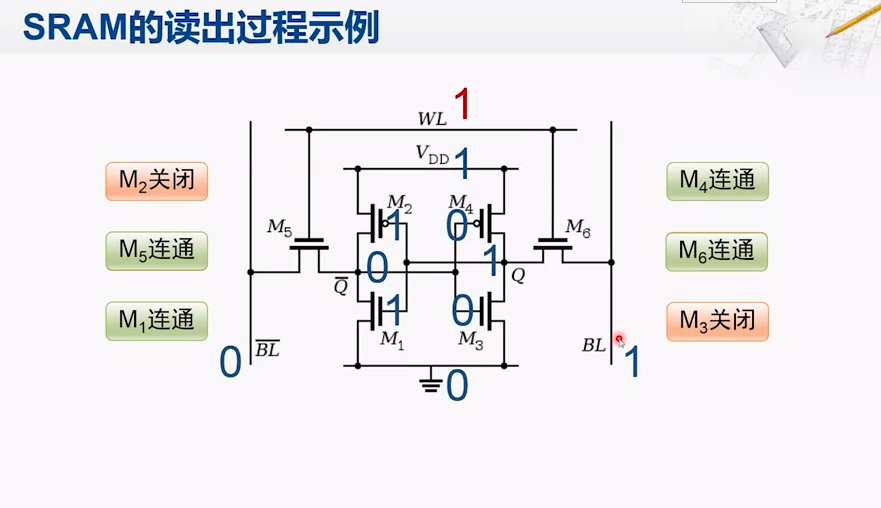

SRAM

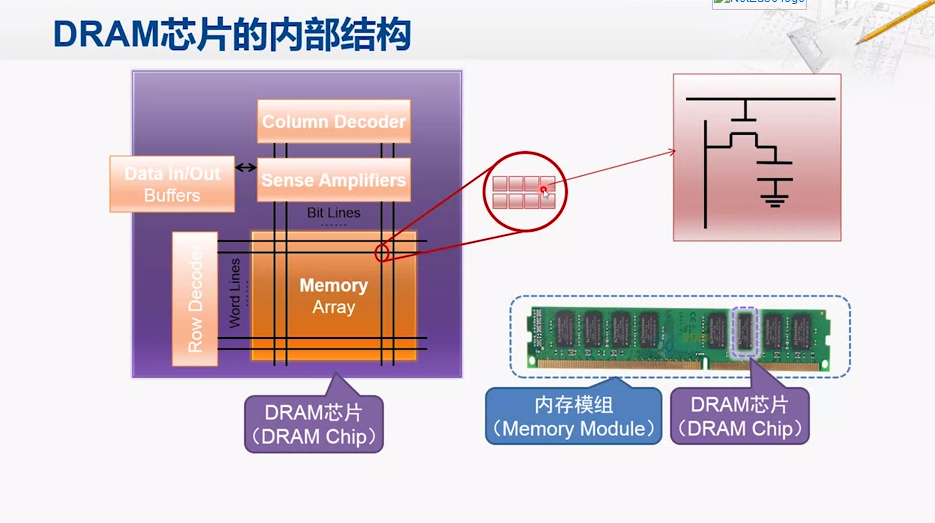

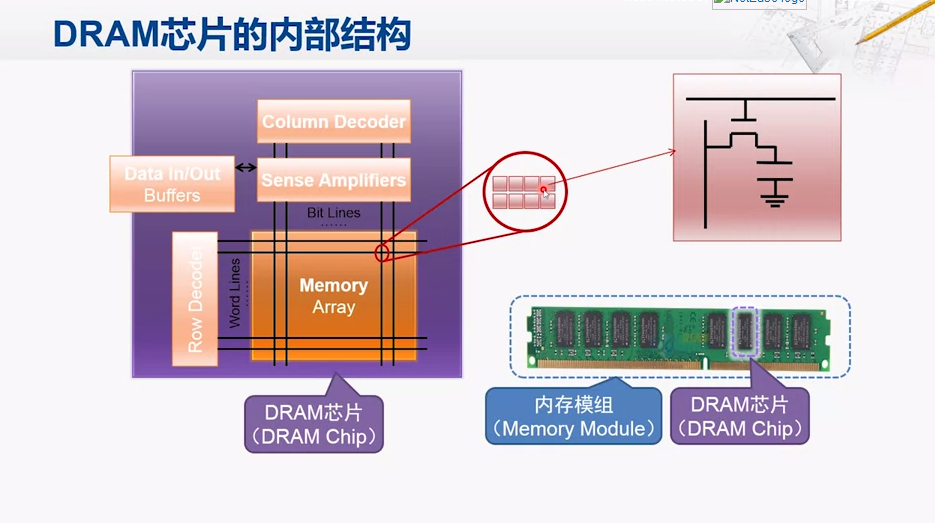

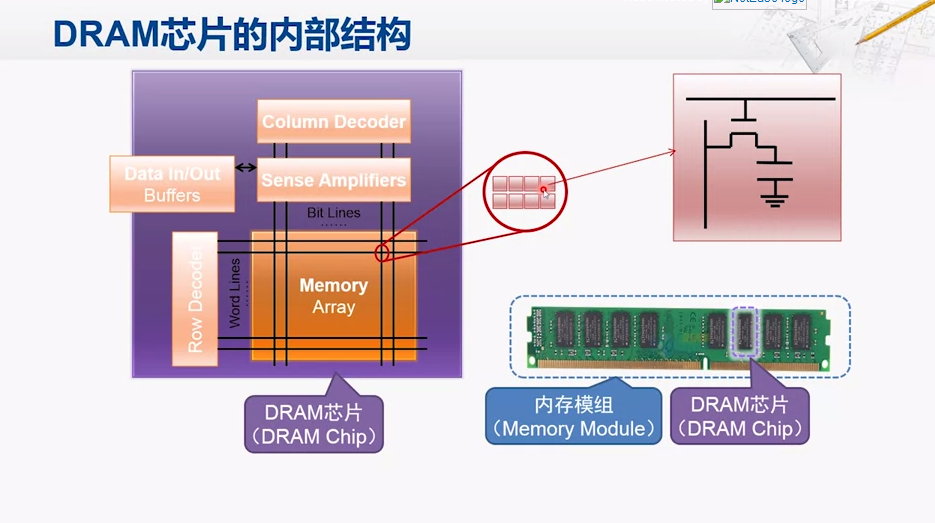

根据外部送入的行地址和列地址生产行选择信号和列选择信号 选中存储单元 .

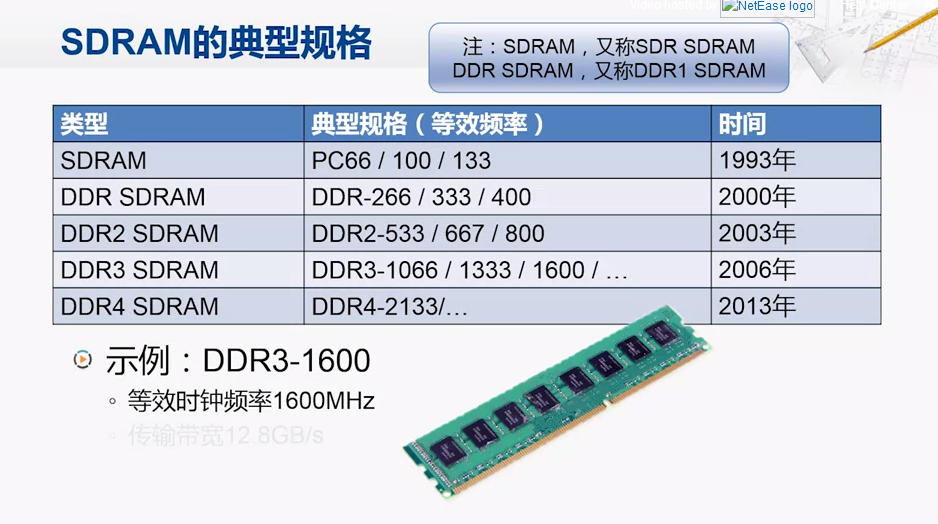

SDRAM是在DRAM的基础上对输入输出接口进行同步,从而提高了读写效率,而现在更为常用的内存则是在SDRAM的基础上又进行了进一步的改进. 如DDR1 SDRAM, DDR2 SDRAM ,DDR3 SDRAM.

DRAM

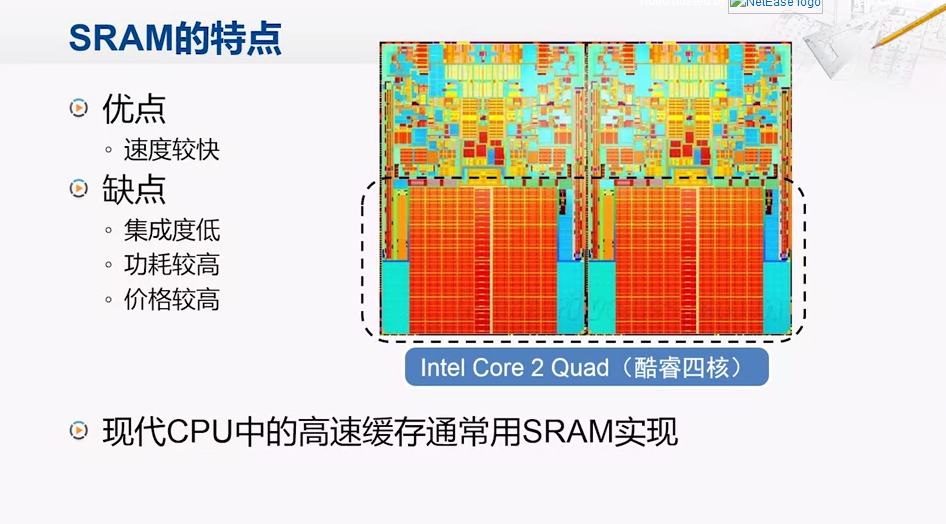

将上述的基本单元组成存储阵列 , 有地址信号,片选信号 , 读写 信号. SRAM 是由晶体管组成 ,自然有了它的优势和缺点

根据它们不同的特点用在不同的场合上

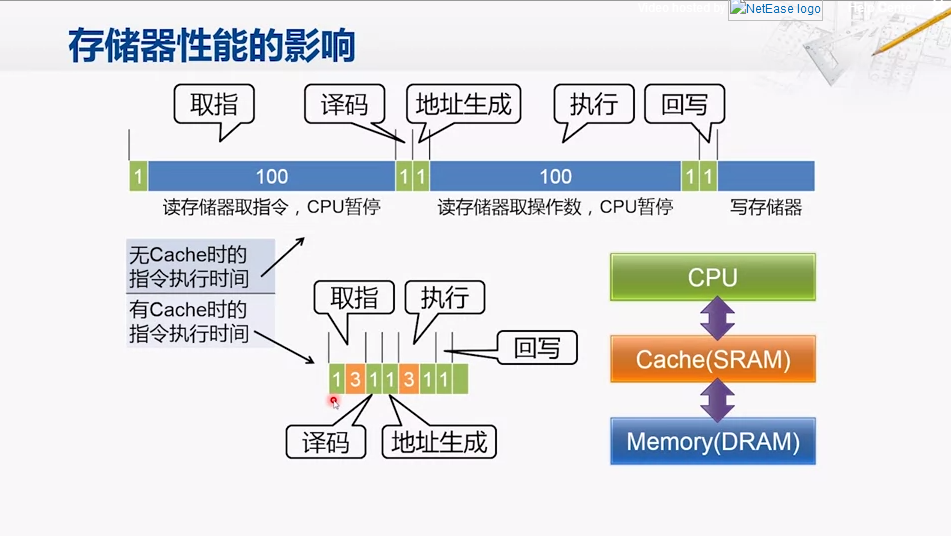

3. 主存的工作原理

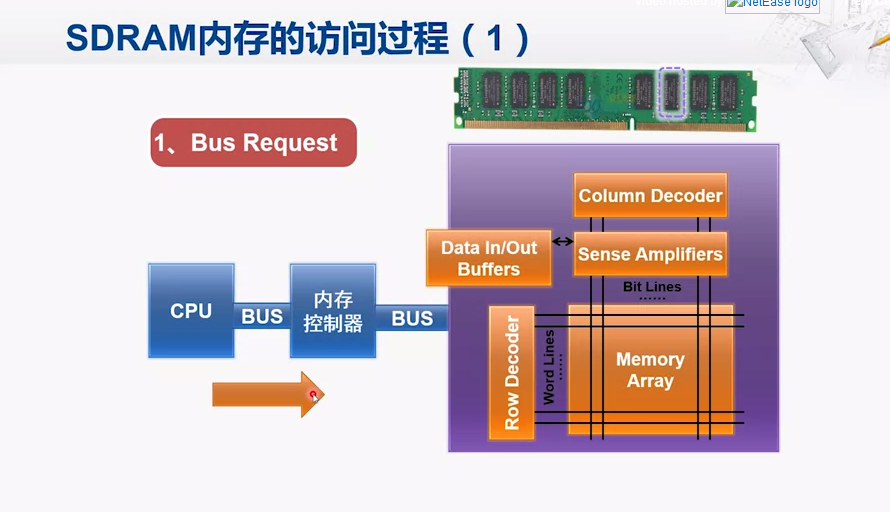

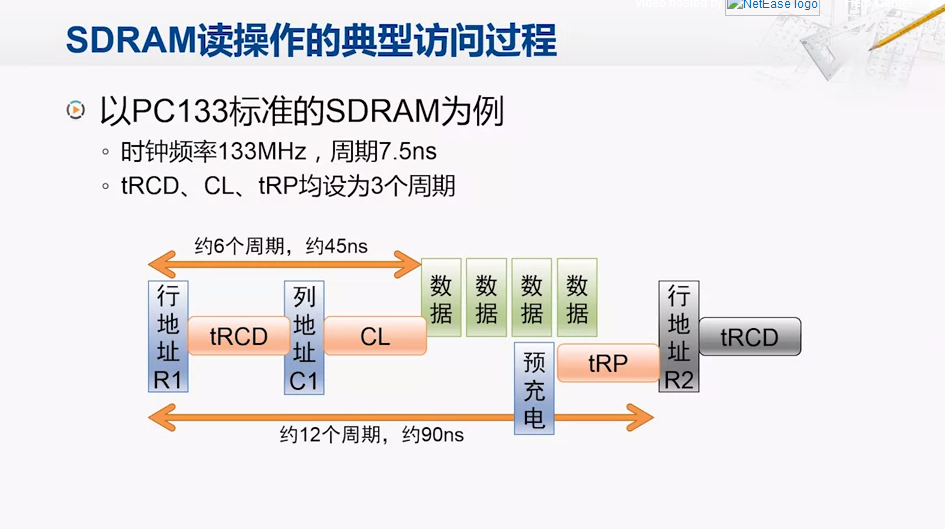

以同步的DRAM为例

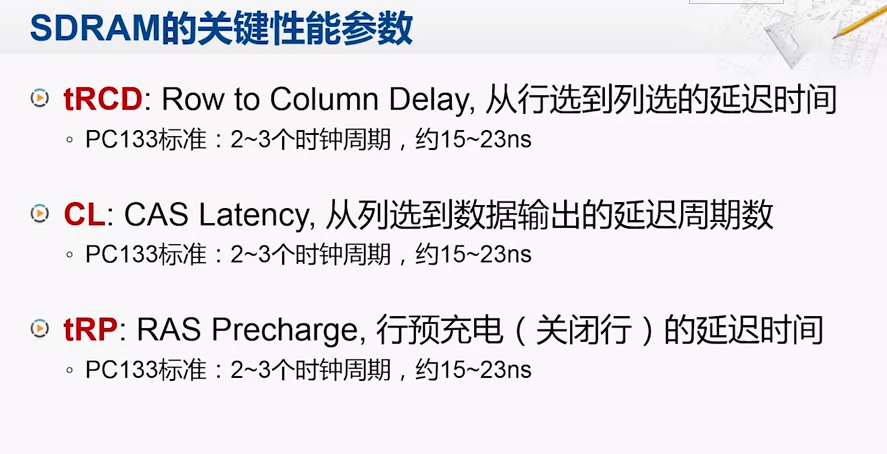

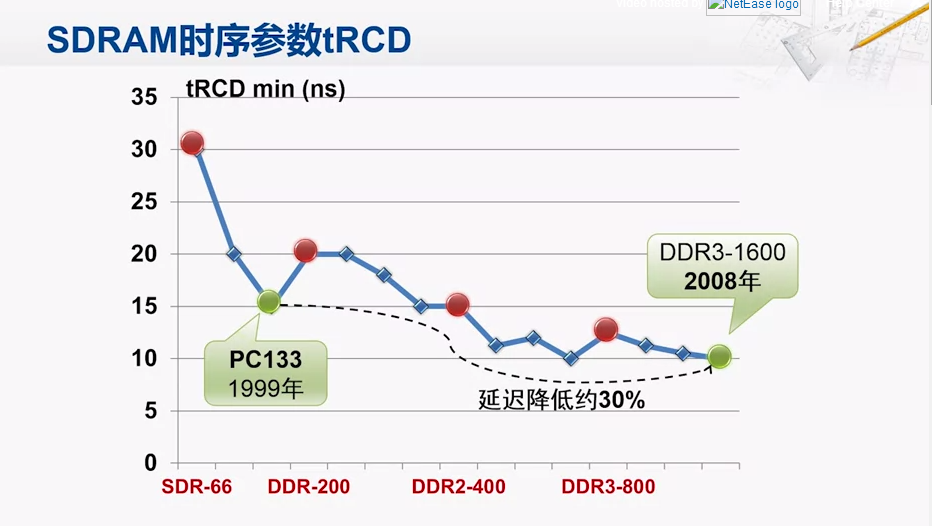

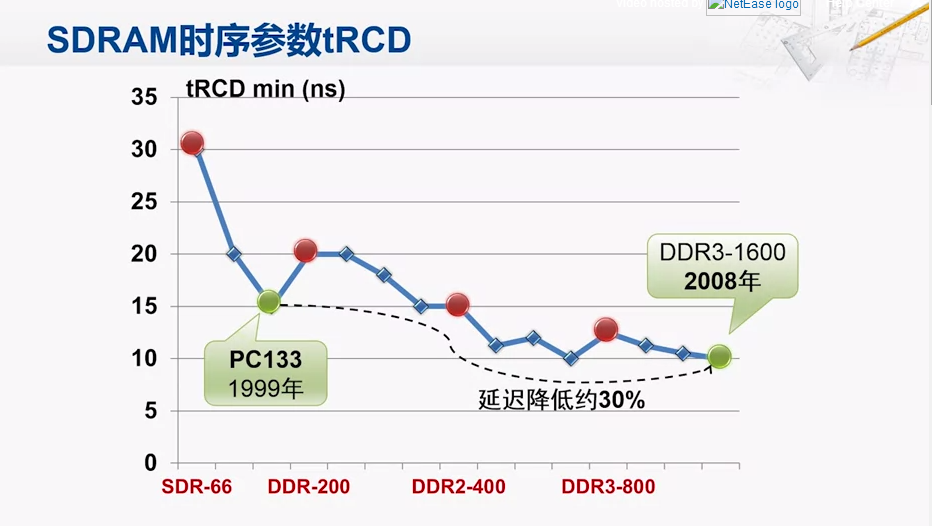

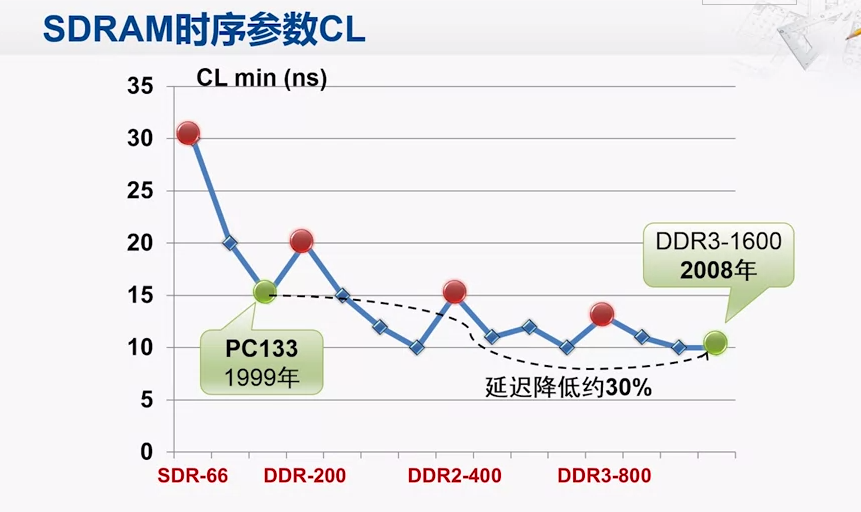

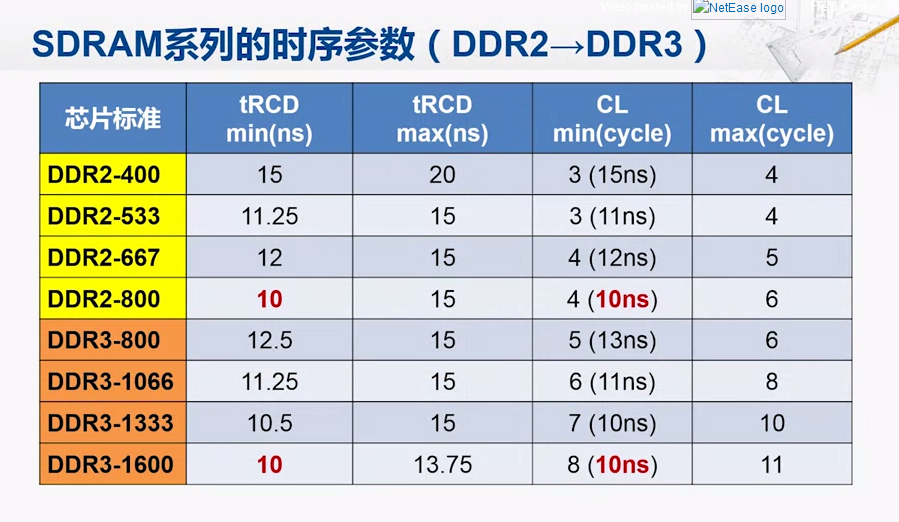

当CPU访问存储器时 ,先要申请系统总线 ,在获得总线的控制权后,会将地址发到内存控制器中对于一个32位的CPU这个地址就是32位的 ,注意在这个时候地址不会分为行地址和列地址 , 而是只有一个地址 , 然后内存控制器会将这个地址进行分解 , 形成行地址和列地址等多个部分 ,然后内存控制器会向DRAM芯片发起访存操作(预充电【可能有也可能没有】 和 行访问 ),进行行访问时 ,内存控制器通过总线发出的行地址会被DRAM芯片中行译码器接收到 , 就会在存储阵列中选出对应的那一行 , 这一行所有的存储单元的都会被放大之后放到缓冲区当中(此过程被称为是激活或者行访问过程)。只有等这个缓冲区的信号都稳定了 , 我们才可以进行下一步的操作。因此我们需要关注的一个时间就叫tRCD , 时间的长短是由DRAM本身的特性决定的 。等tRCD之后内存控制器发出列地址 , 由列地址译码器接收 ,之后到缓存区选出对应的那一列 ,如果现在进行读操作 , 被选中的存储单元的数就会送到数据输出接口上去。从发出列地址到选中存储单元里的数的过程 称为列访问过程,列访问也需要时间,从列选到数据输出的延迟。当DRAM送出数据之后 , 内存控制器就会采样对应的数据,然后将采样的数据送入到CPU当中 , 那过段时间CPU又会发出访存的地址 ,如果这次访问的数据和刚才访问的地址在同一行,那不需要发行地址,只需要发列地址 ,从缓存区中取相应的地址就行了。 当然如果不在一行 ,那么需要把激活的一行关闭,这一过程我们称为预充电 ,实际上预充电可以最早在前一次传输 , 后一个数据即将送出的时候开始,因为我们不确定下次传输到底会不会在同一行 , 所以我们用两种可以选择的策略:1)一种方式是等到新的传输开始如果发现要访问的数据不在已经被激活的这一行 , 那时再进行预充电 。2)另一种方式是在一次传输之后就进行预充电, 这样是在下一次的传输是在同一行概率不高的情况下,反而会获得更好的性能 ,预充电也需要花一定的时间的,tRP

从此可以看出 ,虽然内存的时钟频率是7.5ns , 但并不意味着只需7.5ns 就可以从内存中得到想要的数据

4.主存技术的发展

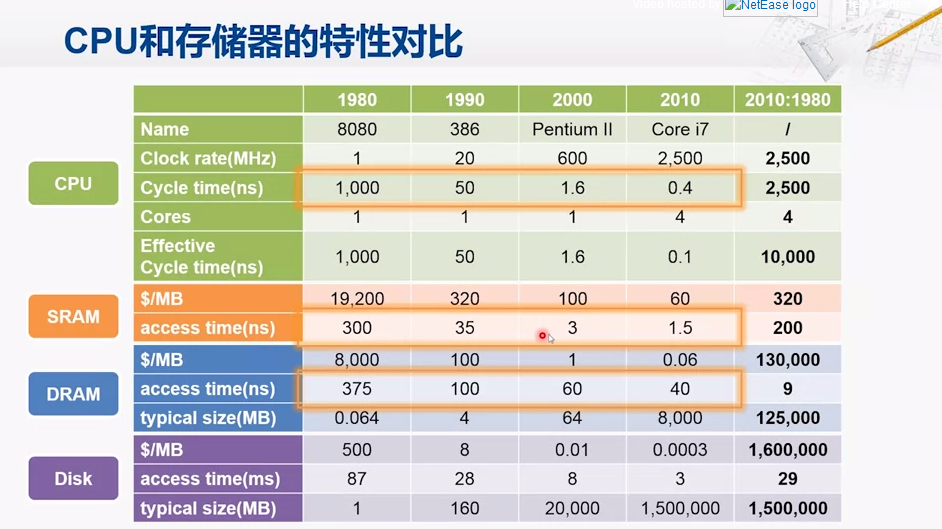

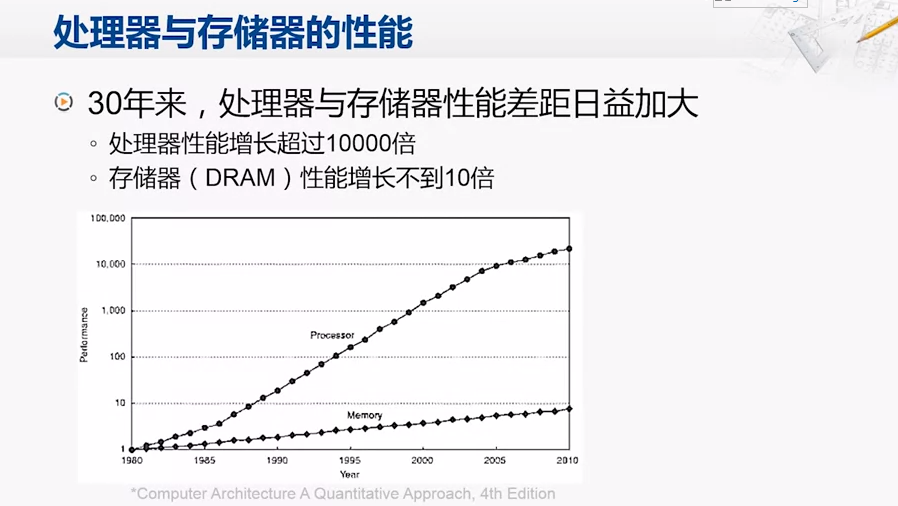

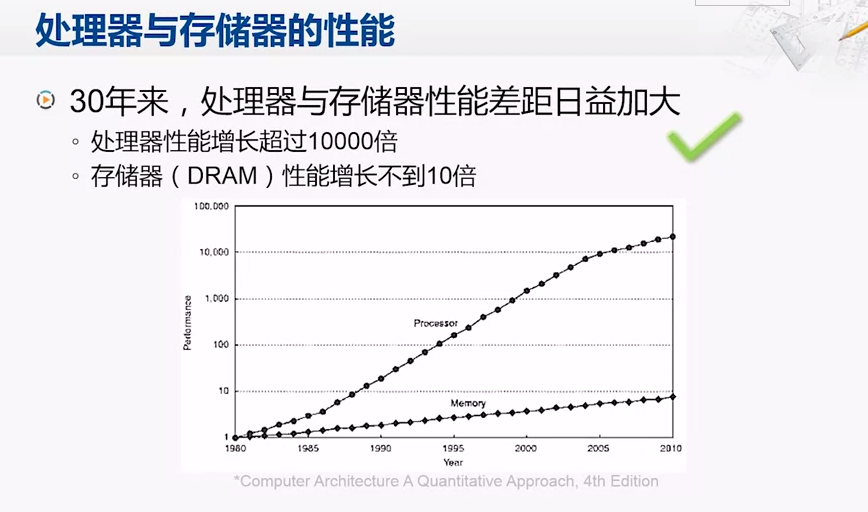

计算机的处理器和存储器的性能差距日益加大 ,这个说法有问题吗?

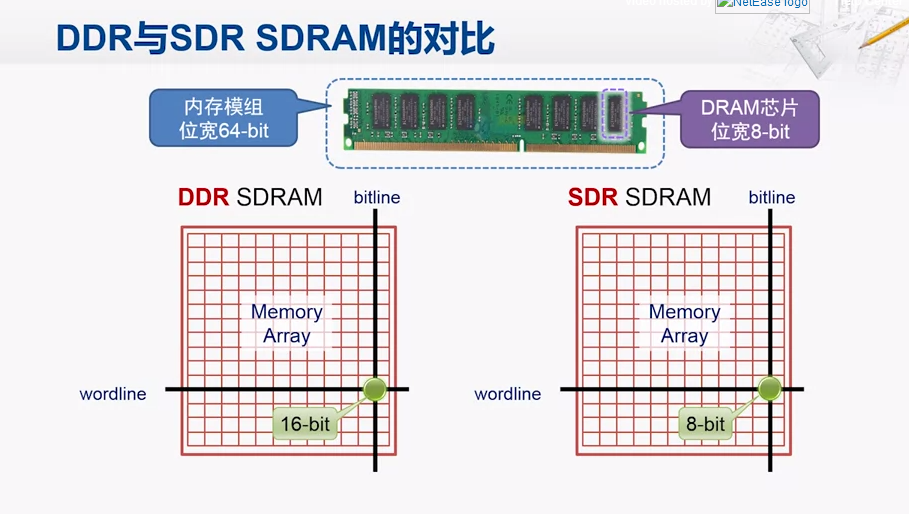

之前提到过SDRAM的结构, SDRAM的基本单元是一个电容和一个晶体管, 对SRAM的读写 ,最终体现了对电容的充放电上 , 而要减少充放电时间是十分困难的 ,因此当 SDR SDRAM时代,当时钟频率提升到133M/hz之后再很难进一步提升了,那后来的DDR SDRAM是如何提升性能的呢?

对于位宽8bit的SDR SDRAM芯片 , 每次访问存储阵列 ,都会取出8 bit 的数据 , 而对于相同位宽的DDR SDRAM芯片,每次访问存储阵列都会取出两倍的数据量 ,这16bit的数据怎么传输的呢? 这就用到双倍数据率的概念。

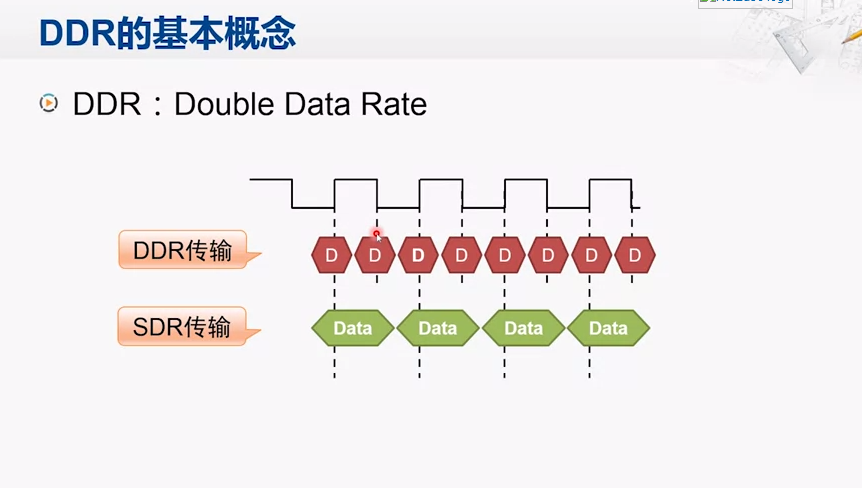

DDR在时钟上升沿和下降沿都传输数据 ,同样的时钟频率下传输双倍的数据 ,注意,DDR是一种传输方式,用在SDRAM 上 就成了DDR SDRAM ,但它不仅仅用在内存上,还用在其他很多领域。

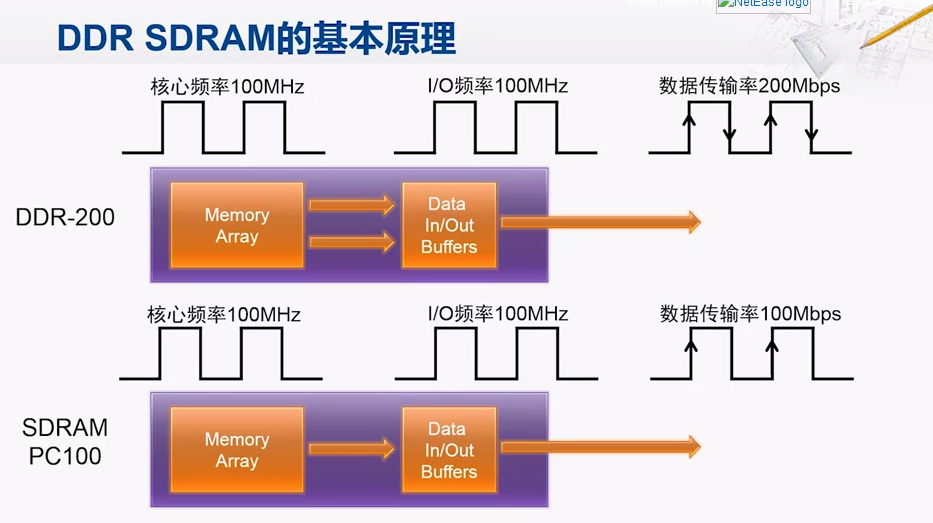

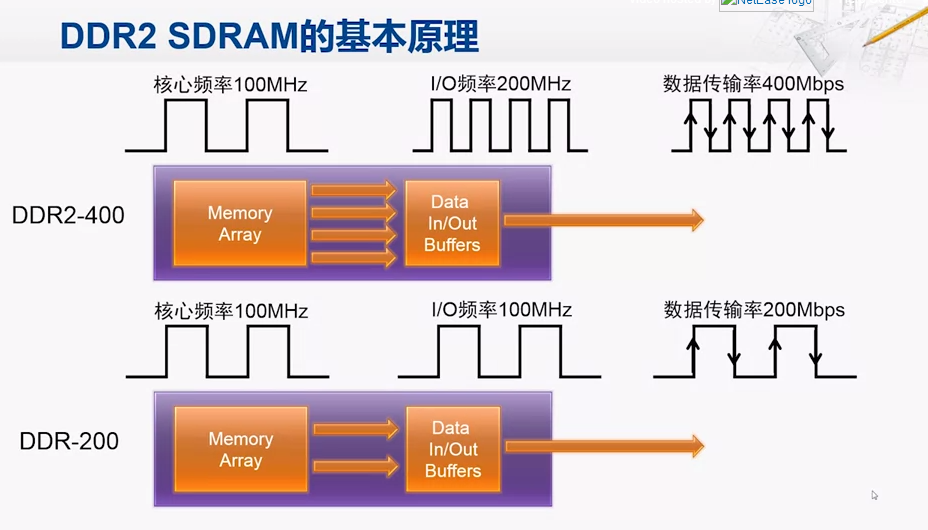

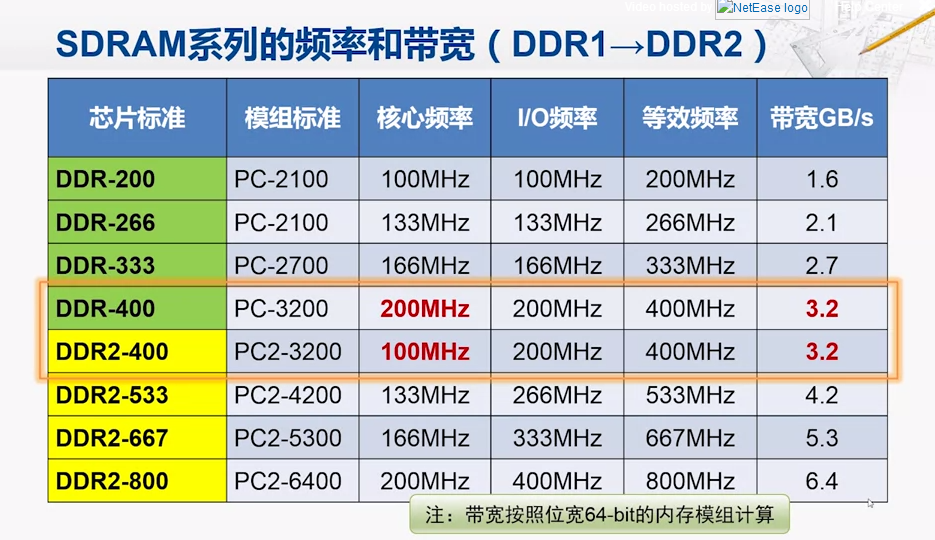

第一代DDR标准 ,即DDR-200存储阵列核心频率依然100M/HZ,但每个时钟周期读出两个数据,而接口的时钟频率依然也是100M/HZ,但因为两个时钟沿都传输了数据所以仍然在一个时钟周期内把这两个数据都传输出去了,从外部看来每个时钟上升沿和下降沿各传输了一个数据,单根数据线上的数据传输率为200Mbps,此乃DDR-200的由来.

我们由下可以明白个问题:通常理解的提升内存性能应该是减少数据读写的时间 ,而此DDR-200没有这么做,

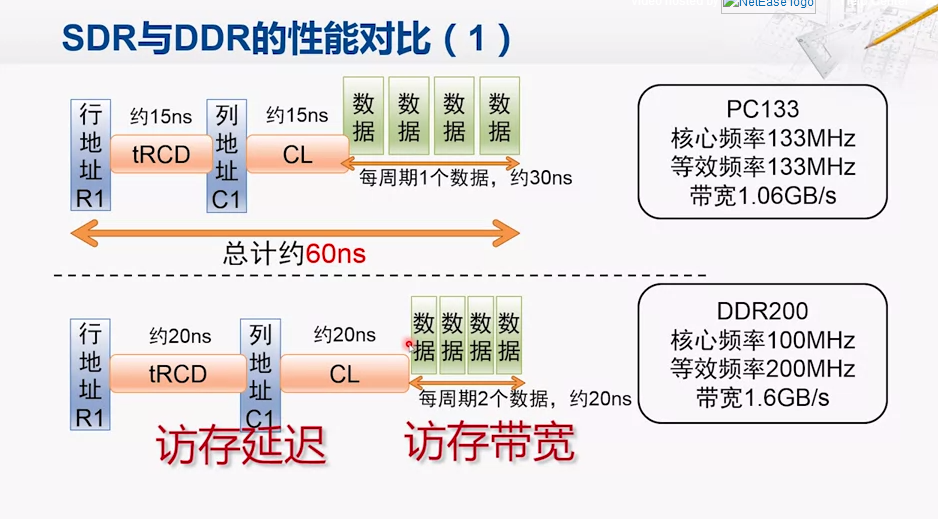

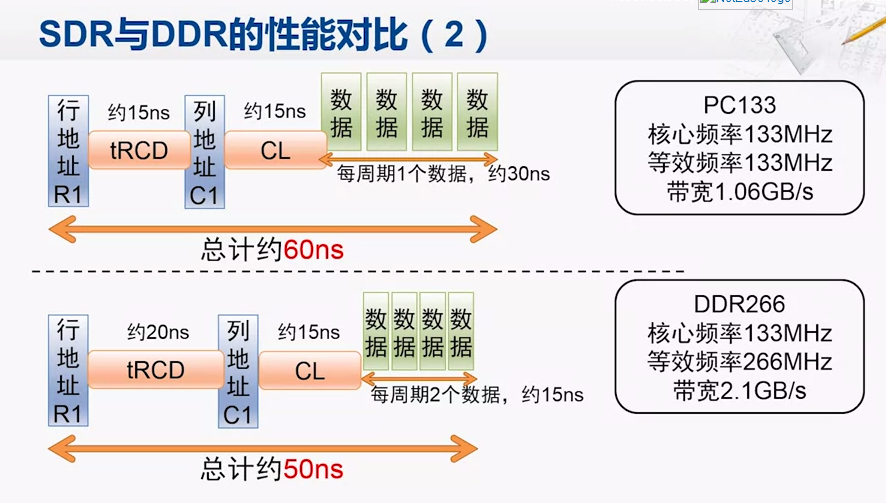

注意:评价内存的性能要看两个指标:1.访存带宽 2.访存延迟

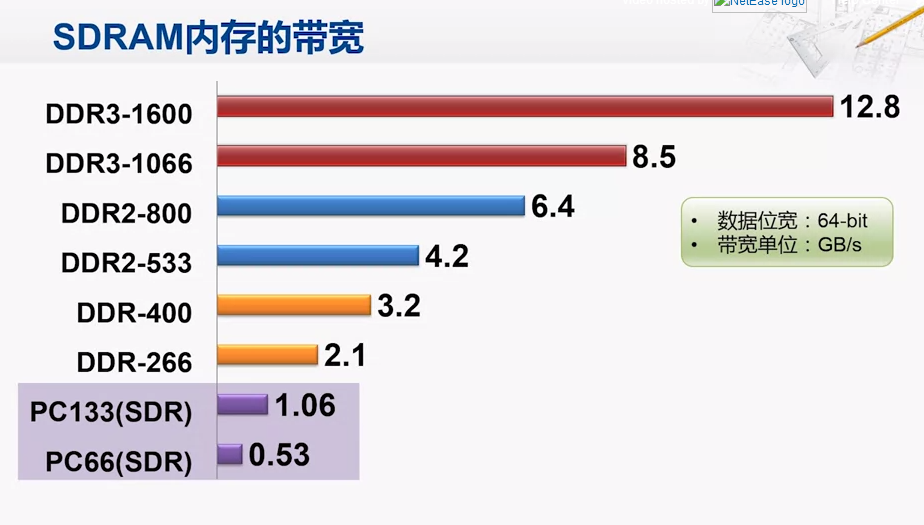

访存带宽是内存厂商大力宣传的.有以下图比较,可以看出DDR-200的性能是比PC133差的,DDR-400的性能明显优于PC133了但是,到了这个时候核心频率的提升又遇到了困难. 那么怎么提升核心频率呢?

既然提升核心频率有困难 , 那就增加预先取出数据的数量,之前从存储阵列中取出双倍的数据 , 现在就取出4 倍的数据 , 这样在外界看来数据传输率为400Mbps , 此时单靠双倍数据率的传输也不够了 , 所以I/O接口时钟频率也提升了一倍,变成了200M/HZ ,这样上下时钟沿都传输数据 , 正好在一个核心时钟的一个周期内把4个数据都传输出去了.

和之前的一样DDR2 SDRAM的第一代性能也不好, DDR2-400性能不如DDR-400 , 很快就被市场淘汰了.

而从DDR2 到 DDR3 的升级基本上也是同样的套路

从下面三个图可以看出 , 内存的发展过程 , 基本上以就是以牺牲访存延时为代价 ,努力提高访存带宽 , 访存带宽确实有了几十倍的提升, 但是访存延时的优化的幅度很有限 , 这是由 SDRAM 的基本单元结构决定的 , 也就是那个电容的充放电过程 ,如果不从材料和结构上做根本的改变 , 基于现在的SDRAM结构 ,想要优化访存延迟是很困难的 , 所以说从处理器访存的基础要求来看 , 读出一个指定数据所需要的时间确实没有多少改善,这个说法是正确的。这就是所谓内存越来越高的真相 , 如果我是CPU ,我想要的数据你并不能快点给我 , 但你却给我很多我现在用不着的数据 ,这对现状有帮助吗?

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?