总结来自于文章《arm嵌入式系统开发–软件设计与优化》

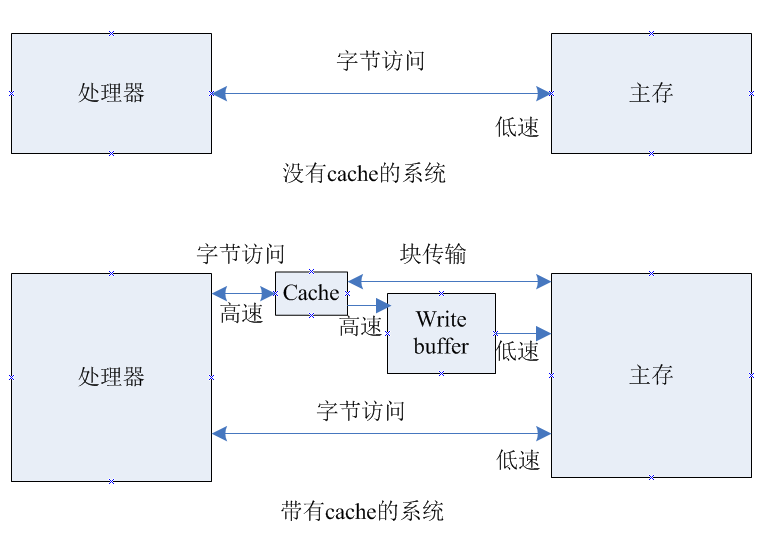

cache是一种容量小,速度快的存储阵列,它位于主存和处理器核之间,保存着最近一段时间处理器涉及到的主存内容。在某些场合需要进行数据读取操作时,为了改善系统性能,处理器尽可能从cache中读取数据,而不从主存中获取数据,这主要是为了减小慢速存储器给处理器造成的访问瓶颈问题。

write buffer是一个非常小的FIFO,也位于处理器和主存之间,为了将处理器和cache从较慢的主存写操作中解放出来,通常搭配cache一起使用。

cache与主存的关系主要体现在高速cache和低速主存之间传输的小块数据上,这种小块数据被称为cache行。write buffer作为临时缓冲区帮助cache释放存储空间,从cache中搬出的数据暂存在write buffer中。cache控制器将cache行以比较高的速度存放到write buffer,之后write buffer以较低的速度将该cache行写入主存中。

哈佛架构的处理器核中,cache被分为I-cache和D-cache,指令被存储在I-cache中,数据被存储在D-cache中。

一个简单的cache存储器,每个cache行都由3个部分组成:directory store,status information,data section。

其中directory store用来标记每个cache行是从主存中的哪个地方拷贝来的,这个目录项被称为cache标签;

status information用来记录状态信息,常见的状态位是有效位和脏位,有效位用来标记当前的cache行是活动的,脏位则用来标记该cache行中所含的内容与主存中对应内容是否一致。

下面介绍cache控制器,cache控制器将主存中的数据或者代码自动拷贝到cache存储器中,自动完成搬移工作,不需要软件额外介入。读/写存储器的请求在被发送到存储器控制器时,会先被cache控制器截获,cache控制器将该请求的地址信息分成3个部分:标签域tag field,组索引域set index field,数据索引域data index field。

控制器通过组索引域在cache存储器中确定可能cache行的位置,接下来检查cache行中有效位,以确定该cache行当前是否处于活动状态,并且将请求地址的标签域和cache标签比较。如果该cache行当前是活动的,而且标签域和cache标签值一致,则cache命中;否则,则cache失效,在失效的情况下,控制器从主存中拷贝整个cache行到cache存储器,这种拷贝的操作称为cache行填充(cache line fill)。

2082

2082

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?