重庆交通大学信息科学与工程学院

《嵌入式系统应用开发》课程

实验报告

班 级: 物联网工程2002姓名-学号 : 谢志聪632007060527

实验项目名称: 实验1-FPGA编程入门

实验项目性质: 设计性

实验所属课程: 《嵌入式系统应用开发》

实验室(中心): 南岸校区语音大楼

指 导 教 师 : 娄路

完成时间: 2023年 5 月 5 日

一、实验内容和任务

1、基于Quartus件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。开发板基于Intel DE2-115。

详细过程可参考附件实验指导书或者学长博客。

嵌入式系统应用开发-实验1-FPGA编程入级-.pdf

FPGA——1位全加器的实现_fpga全加器代码_HarrietLH的博客-CSDN博客

2、在此基础上,用原理图以及Verilog 编程两种方式,完成4位全加器的设计,对比二者生成的 RTL差别;使用modelsim验证逻辑设计的正确性,并在DE2-115开发板上实际验证。

二、实验要求

提交 作业博客地址和 MD文档,FPGA工程项目打包文件。

三. 实验过程介绍

一、原理图设计全加器

1、 半加器设计

(1)半加器的设计

项目创建:

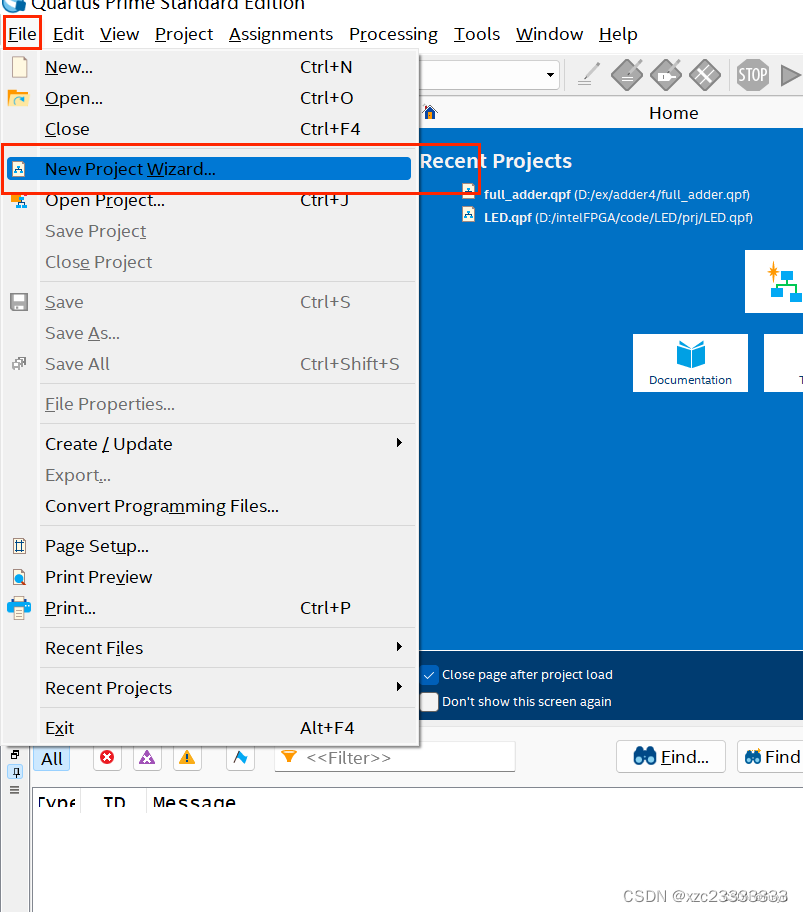

打开Quartus创建新项目:

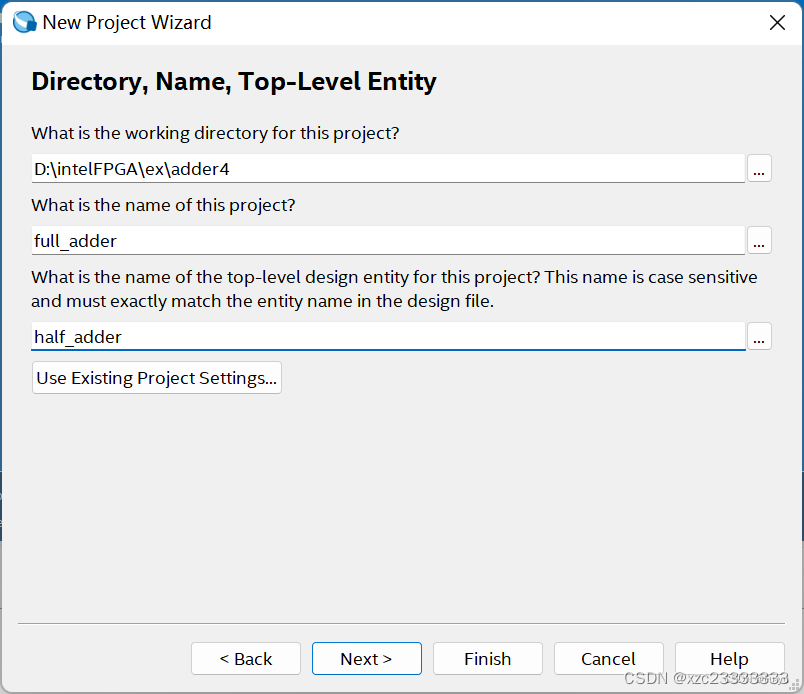

设置项目路径及名称(adder4位实验名命名):

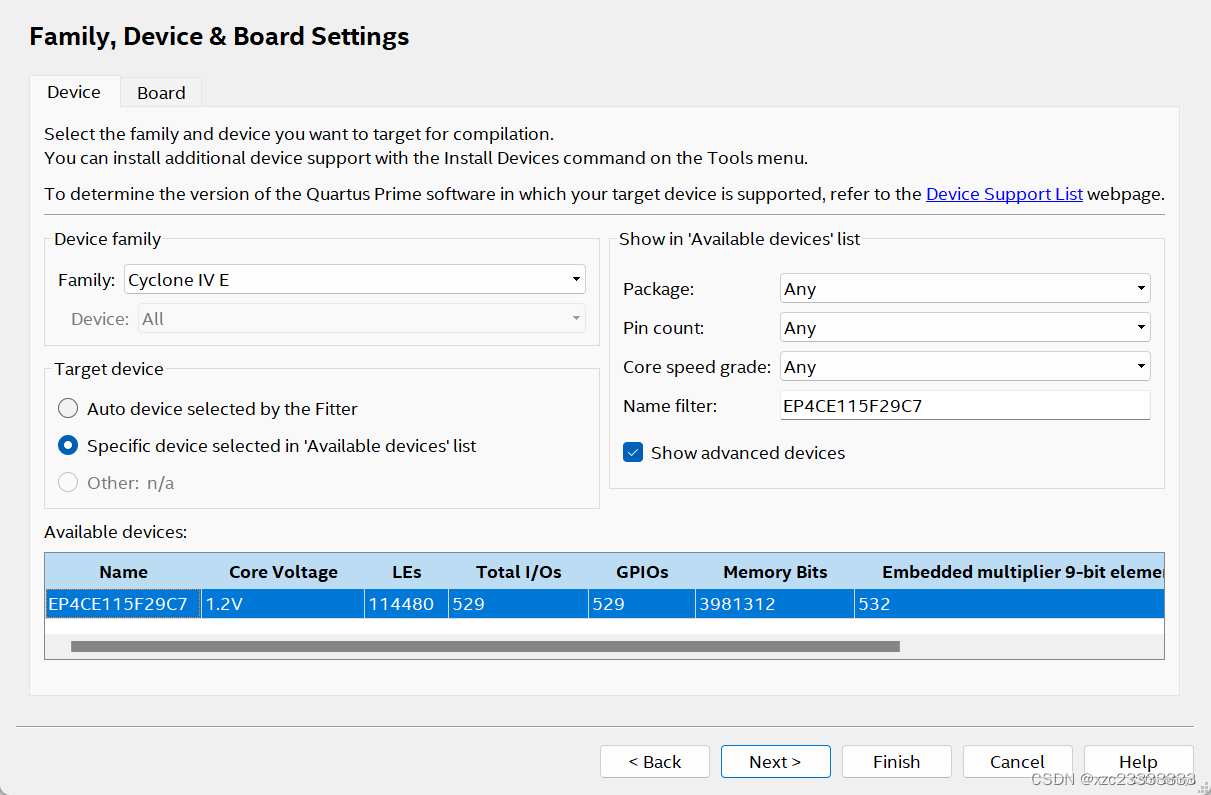

选择芯片(EP4CE115F29C7):

新建原理图文件:

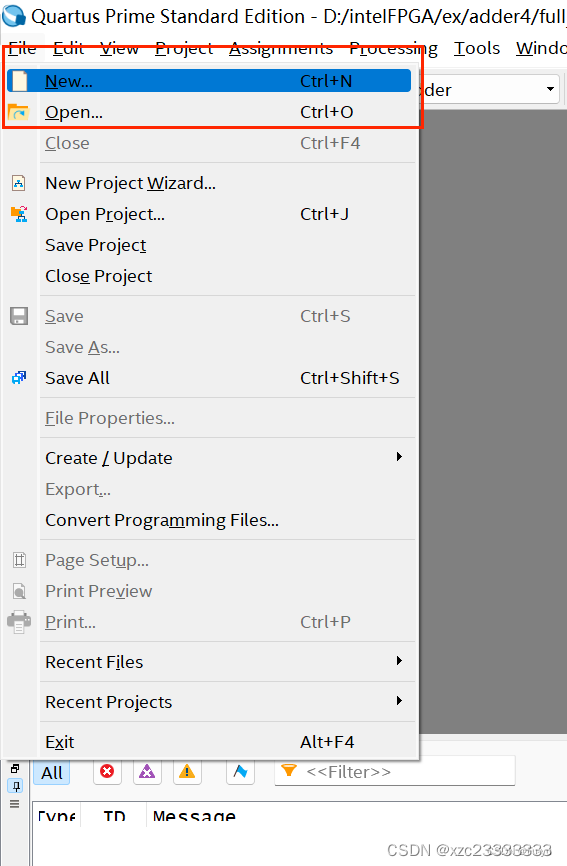

点击File->New,然后选择Block Diagram/Schematic File:

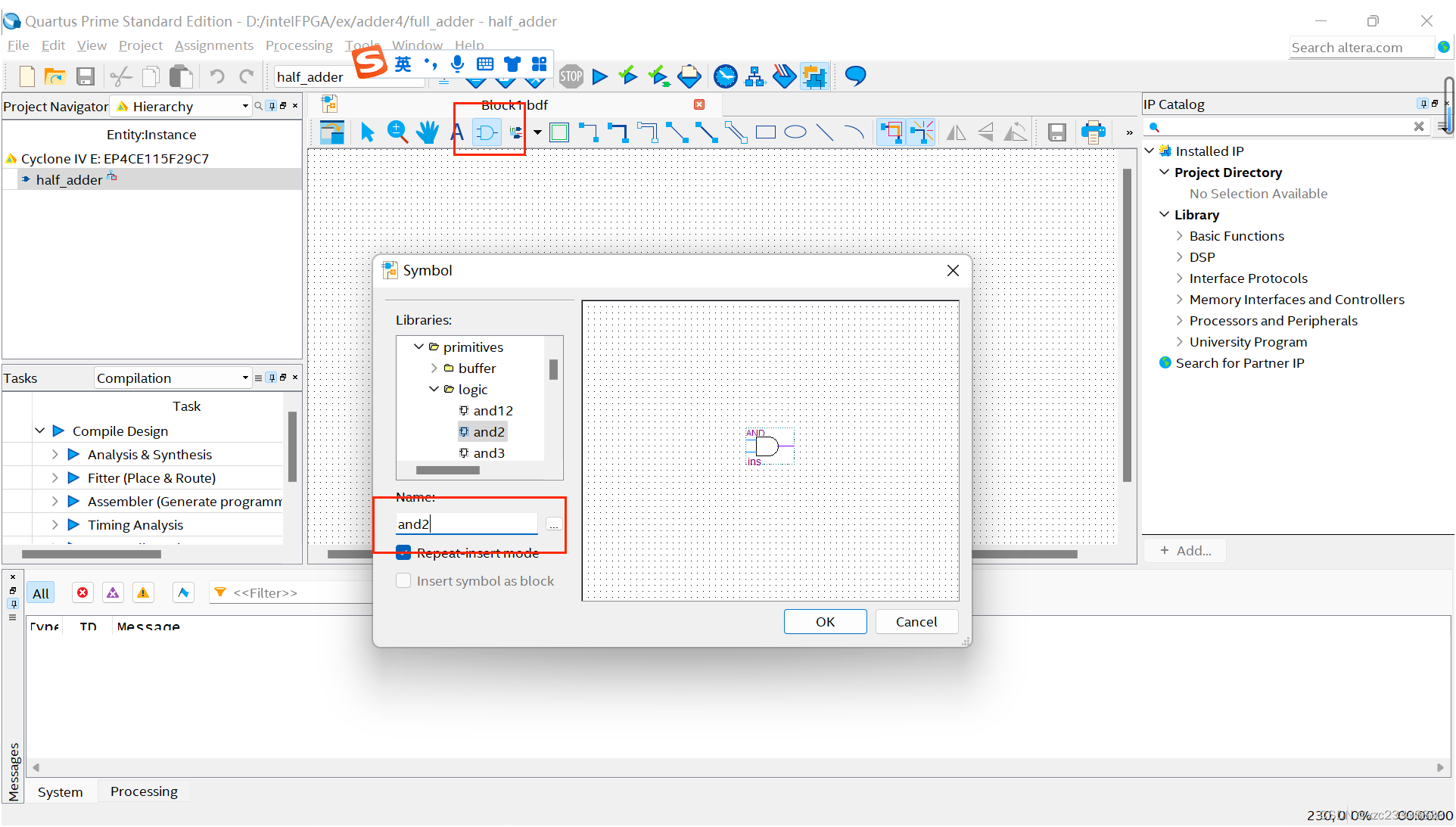

选择元件and2和xor,并绘制原理图:

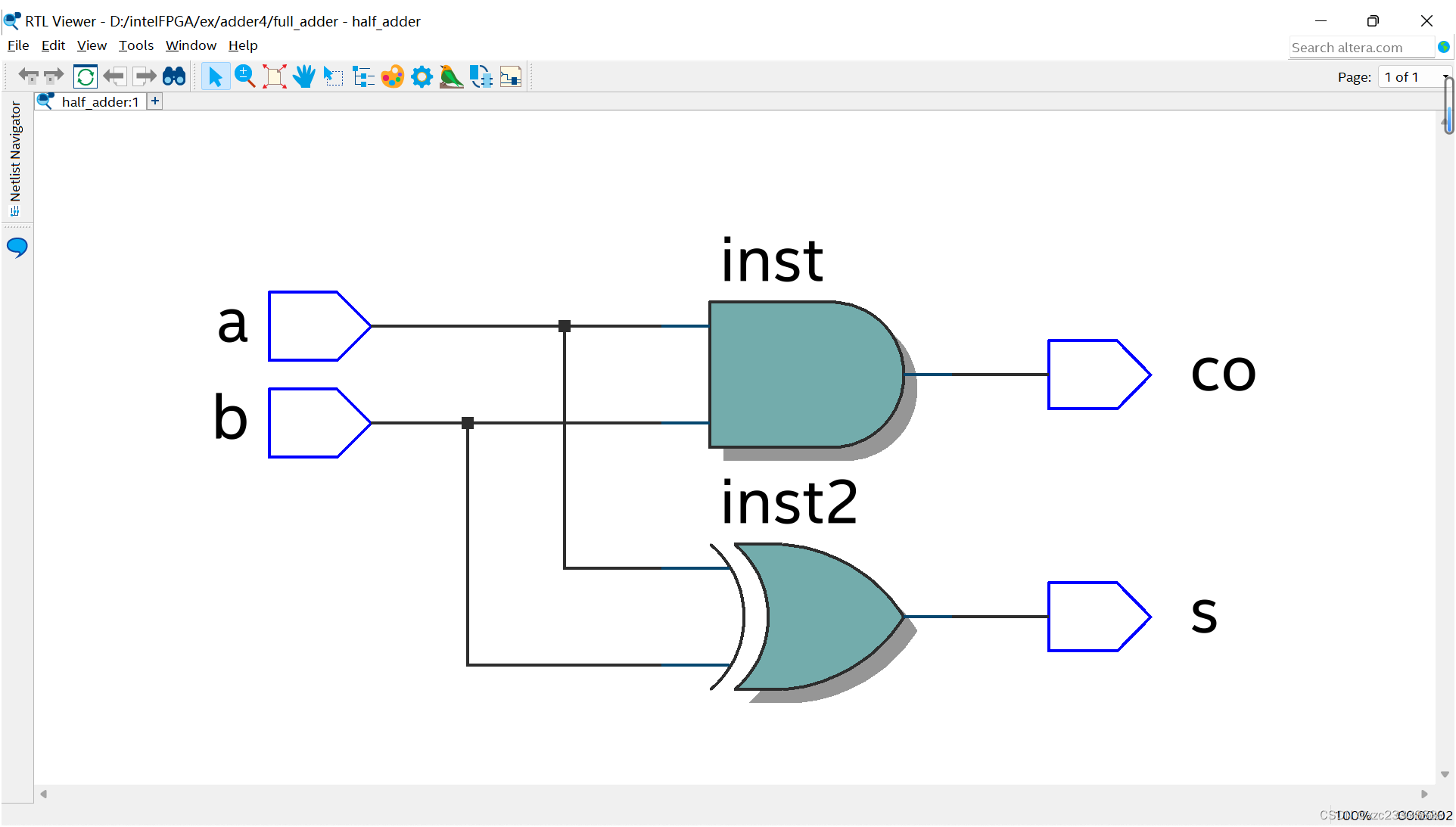

此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

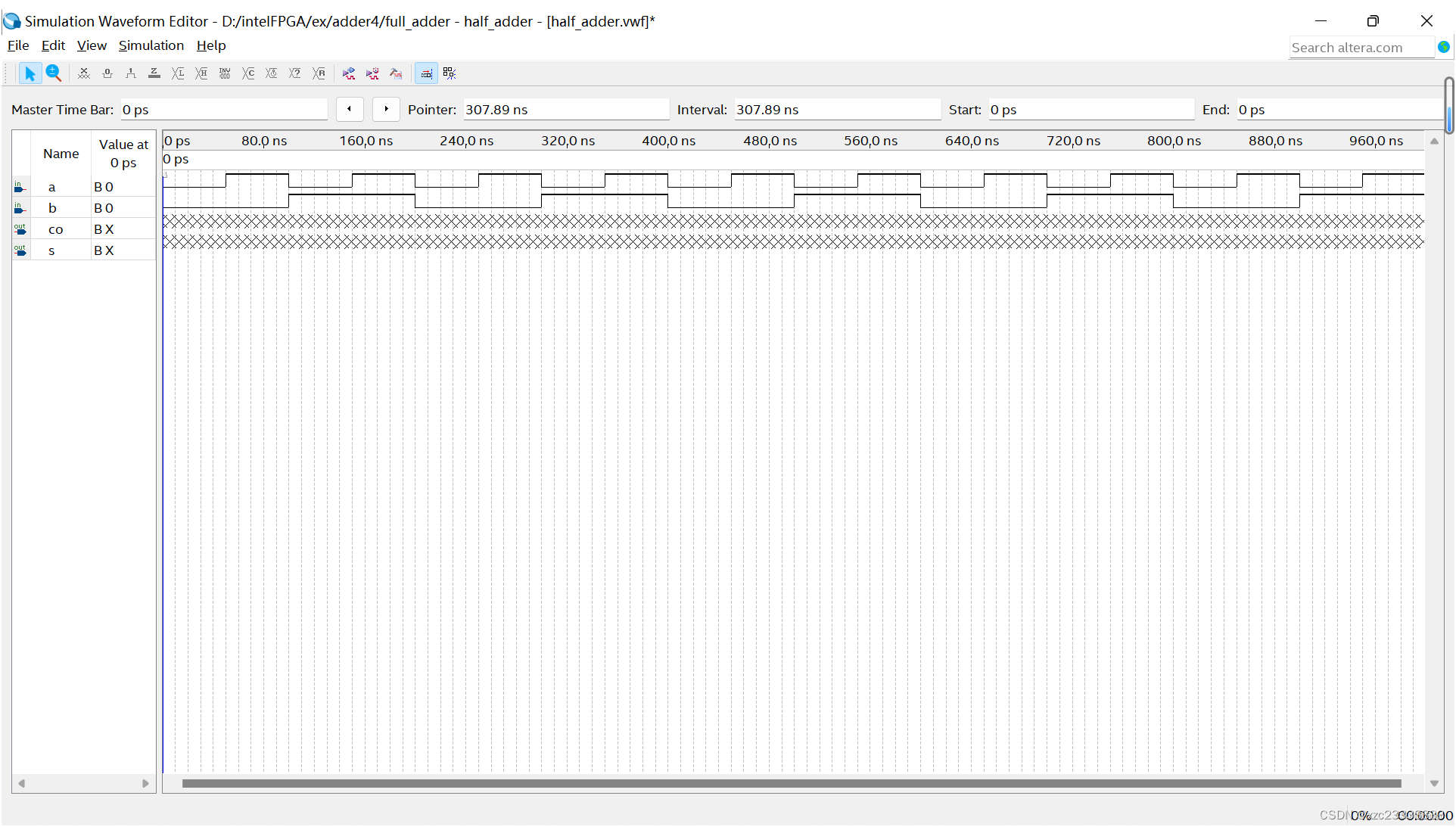

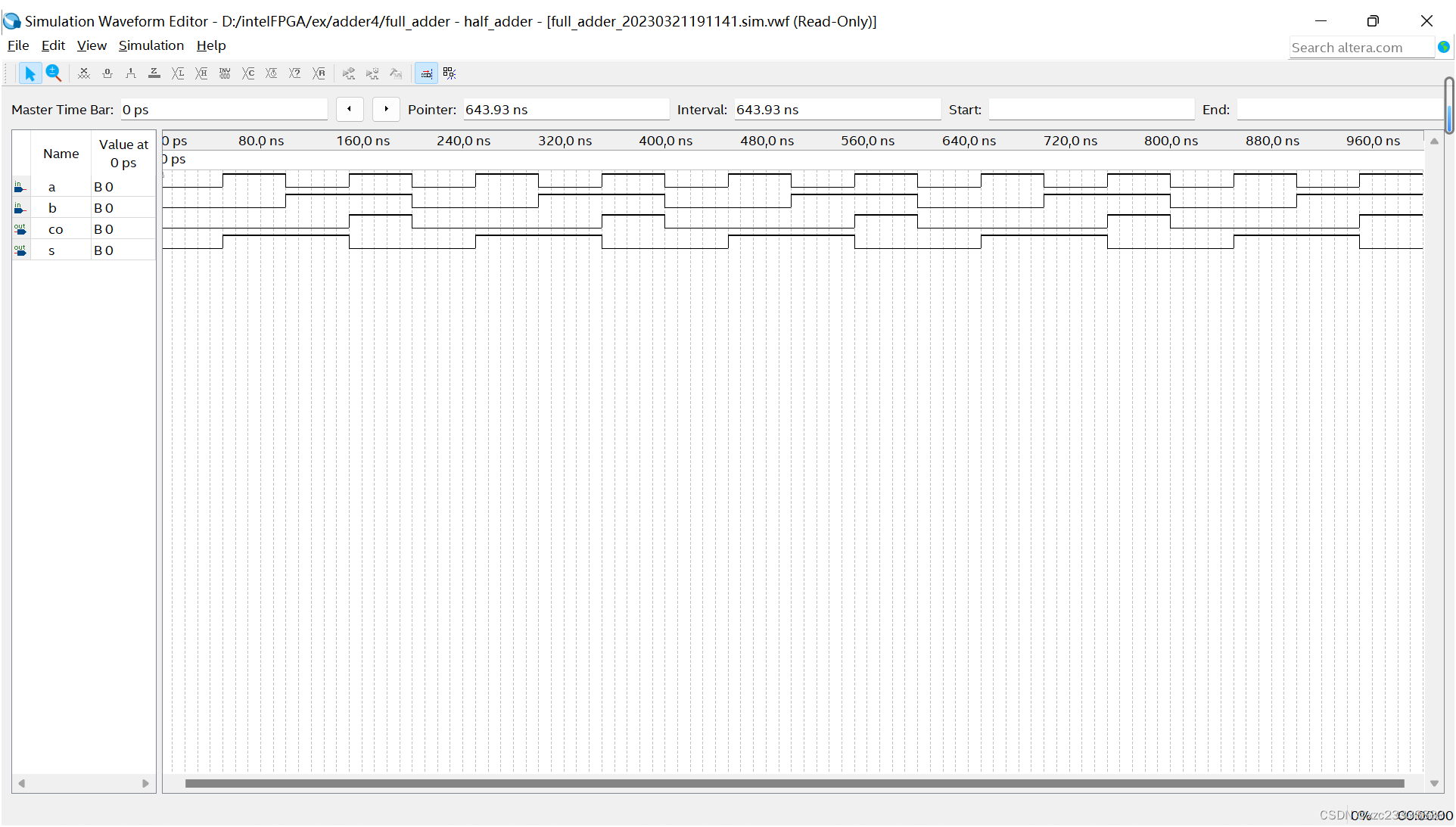

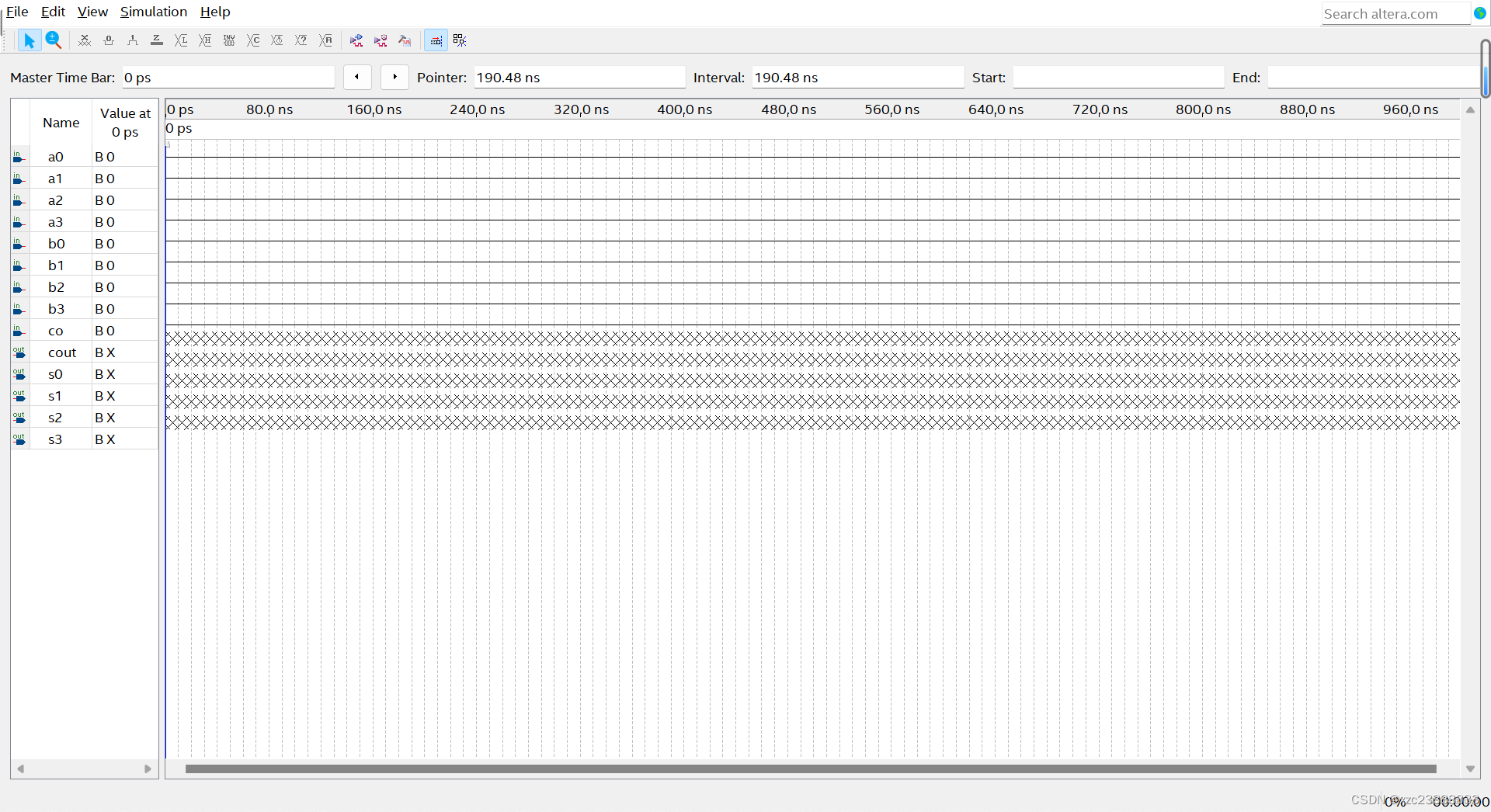

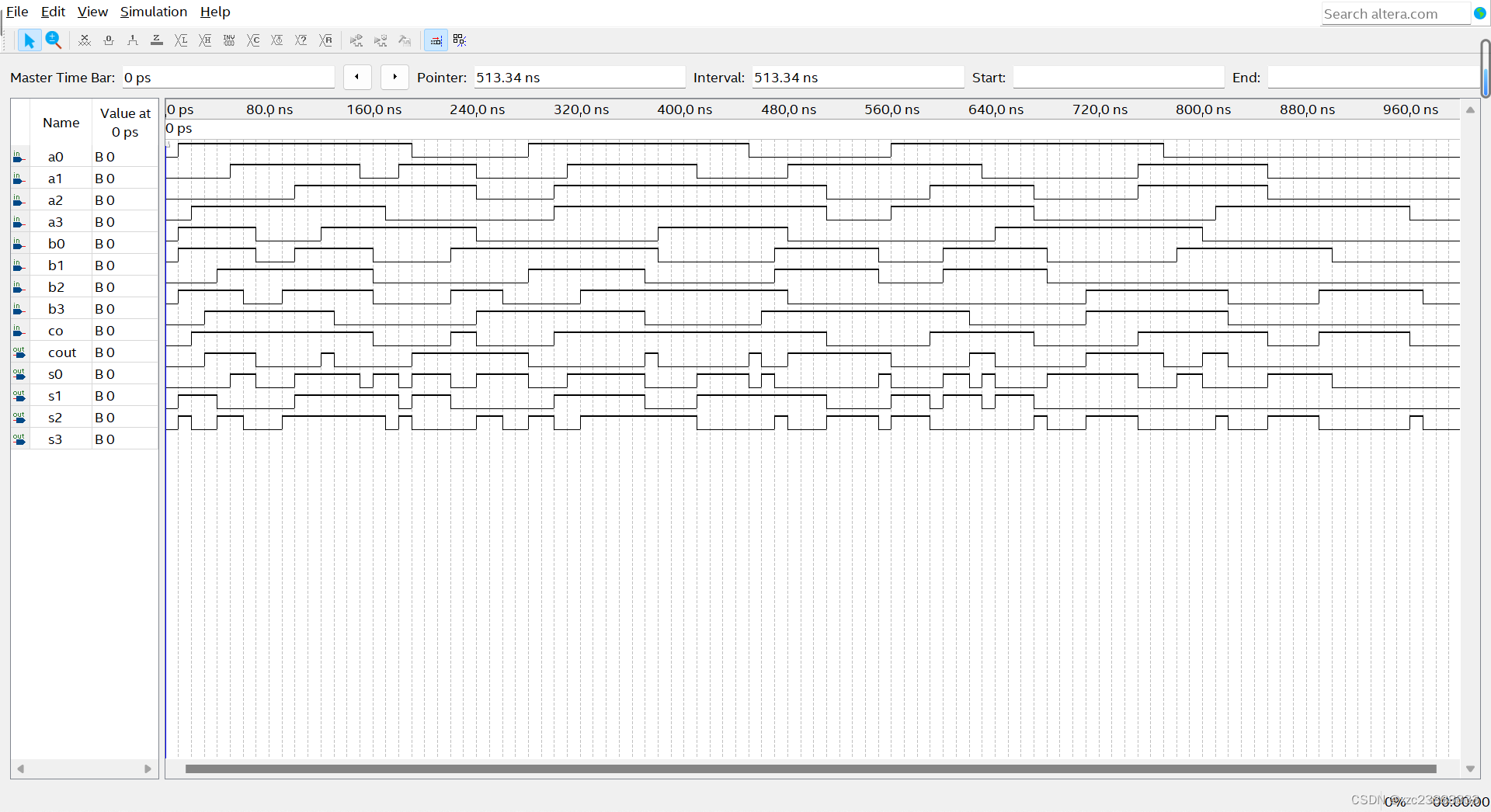

半加器仿真:

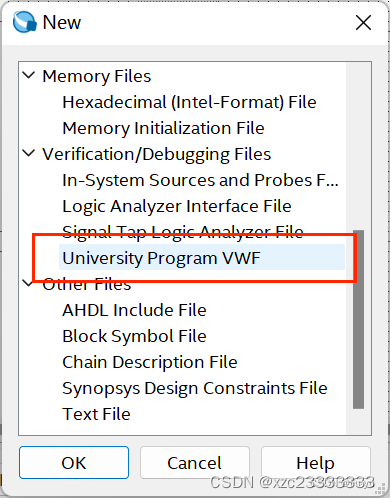

创建一个向量波形文件,选择菜单项 File→New->VWF:

编辑信号:

保存文件并启动功能仿真:

保存文件并启动功能仿真:

通过仿真结果可以发现当a和b相同时s为0,否则为1;逻辑关系属于异或;当a和b同时为1时,co等于1,其余都为零,逻辑关系为与。

通过仿真结果可以发现当a和b相同时s为0,否则为1;逻辑关系属于异或;当a和b同时为1时,co等于1,其余都为零,逻辑关系为与。

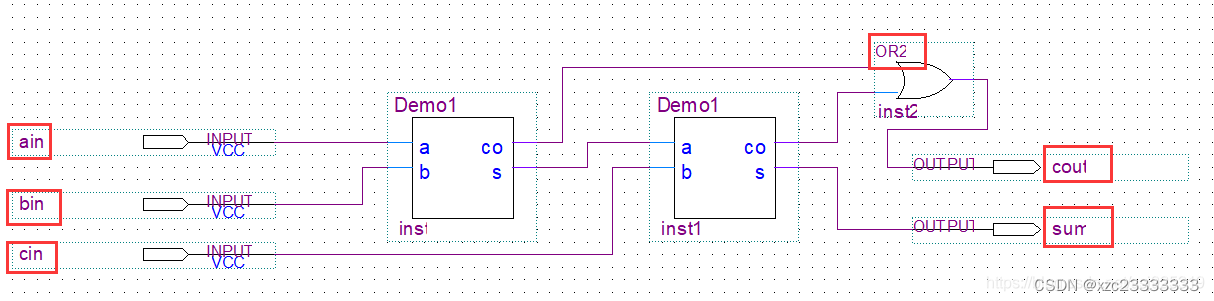

(2)、全加器的设计

全加器: 全加器是指对输入的两个二进制数相加(A与B)同时会输入一个低位传来的进位(Ci-1),得到和数(SUM)和进位(Ci);一位全加器可以处理低位进位,并输出本位加法进位。

①新建原理图

新建一个原理图文件,方法同上。

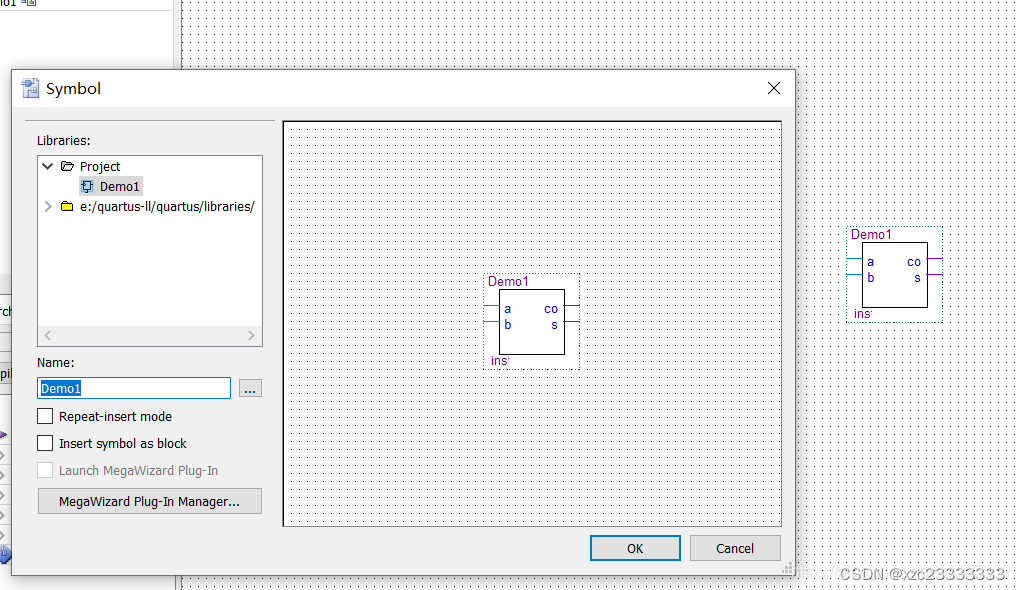

添加上面创建的半加器,我的文件名为 Demo1 。

编辑原理图如下:

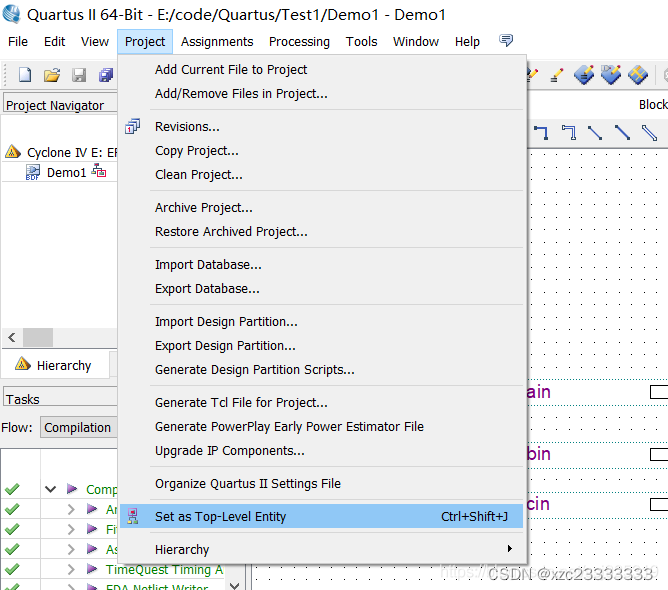

②将设计项目设置成顶层文件并编译仿真

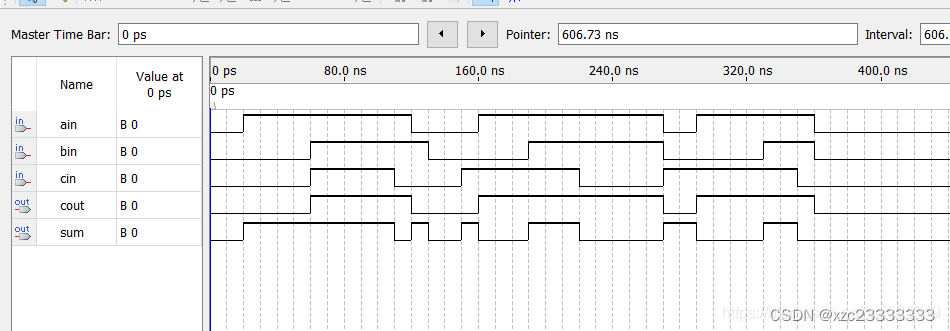

③全加器仿真

2、Verilog实现全加器

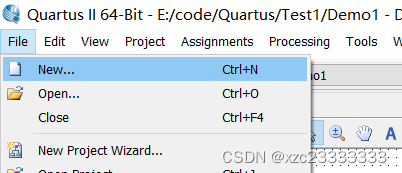

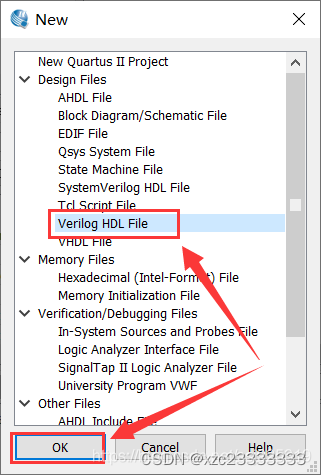

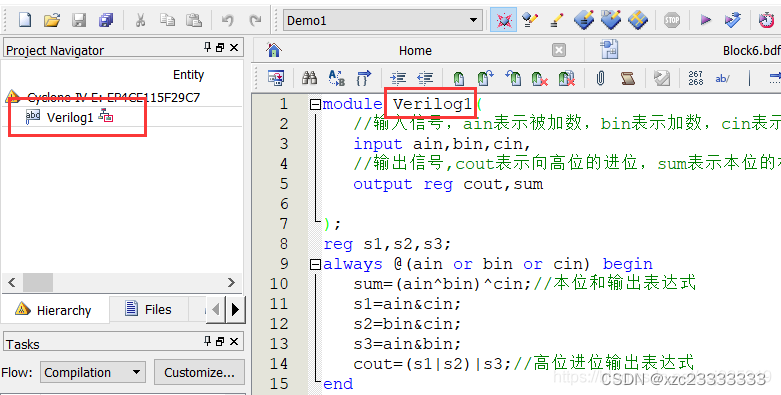

①创建 Verilog 文件

【File】→【New…】。

选择【Verilog HDL File】,点击【OK】。

代码如下:

module Verilog1(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

然后保存文件。

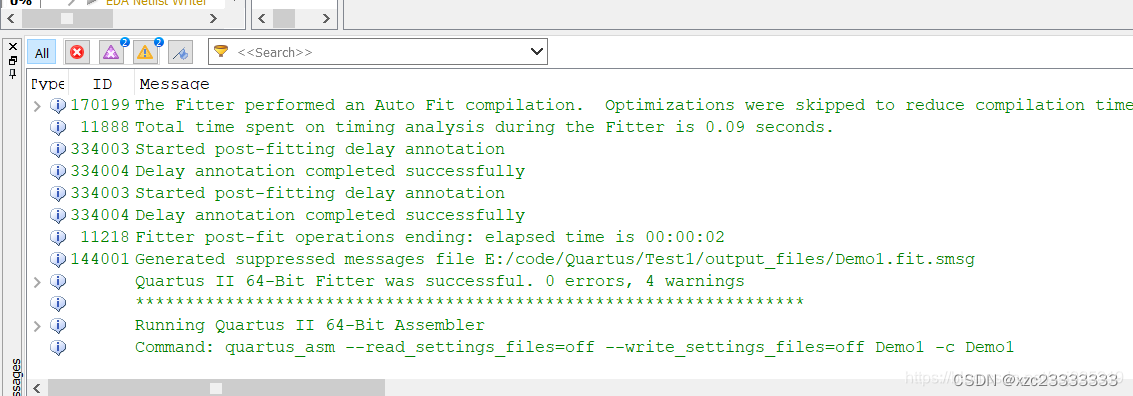

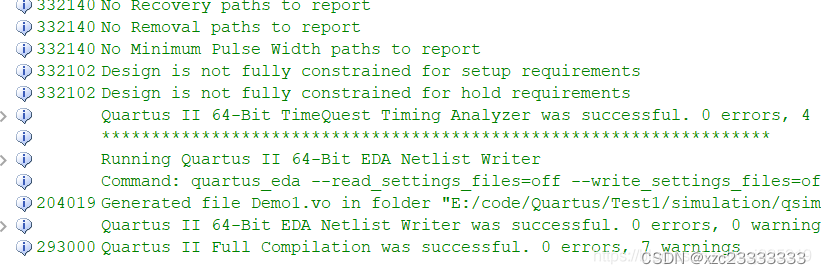

编译 Verilog 文件。

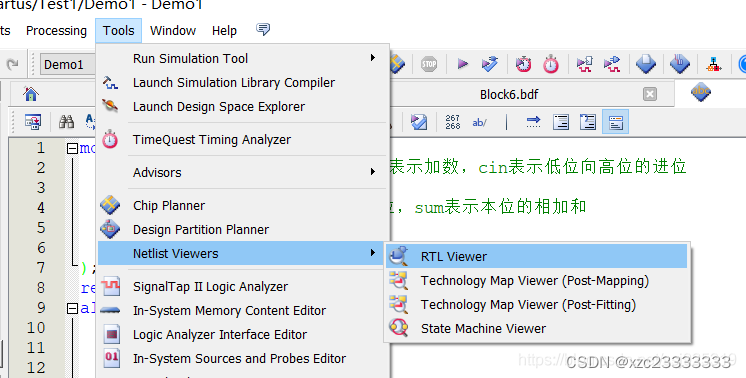

通过【Tools】→【Netlist Viewers】→【RTL Viewer】查看电路图。

②仿真实现

二、4位全加器设计

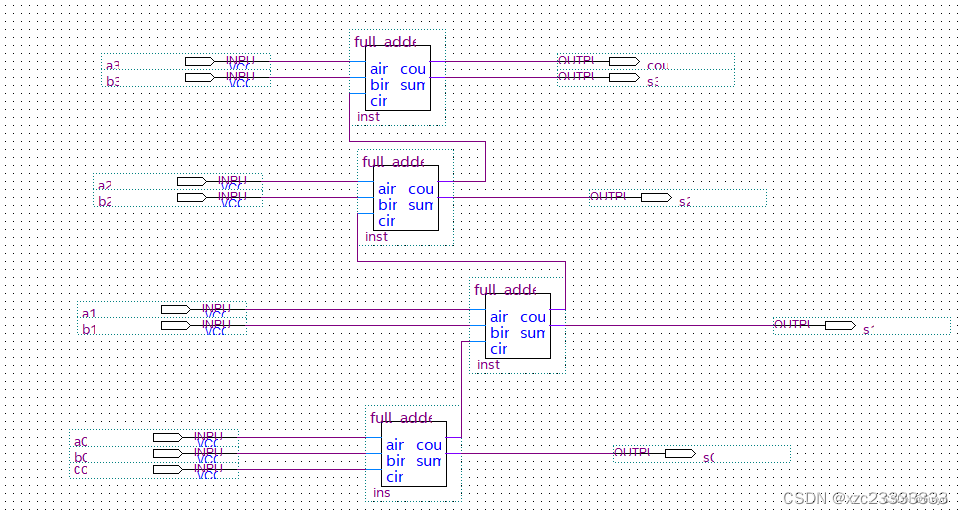

1、输入原理图方法设计4位全加器

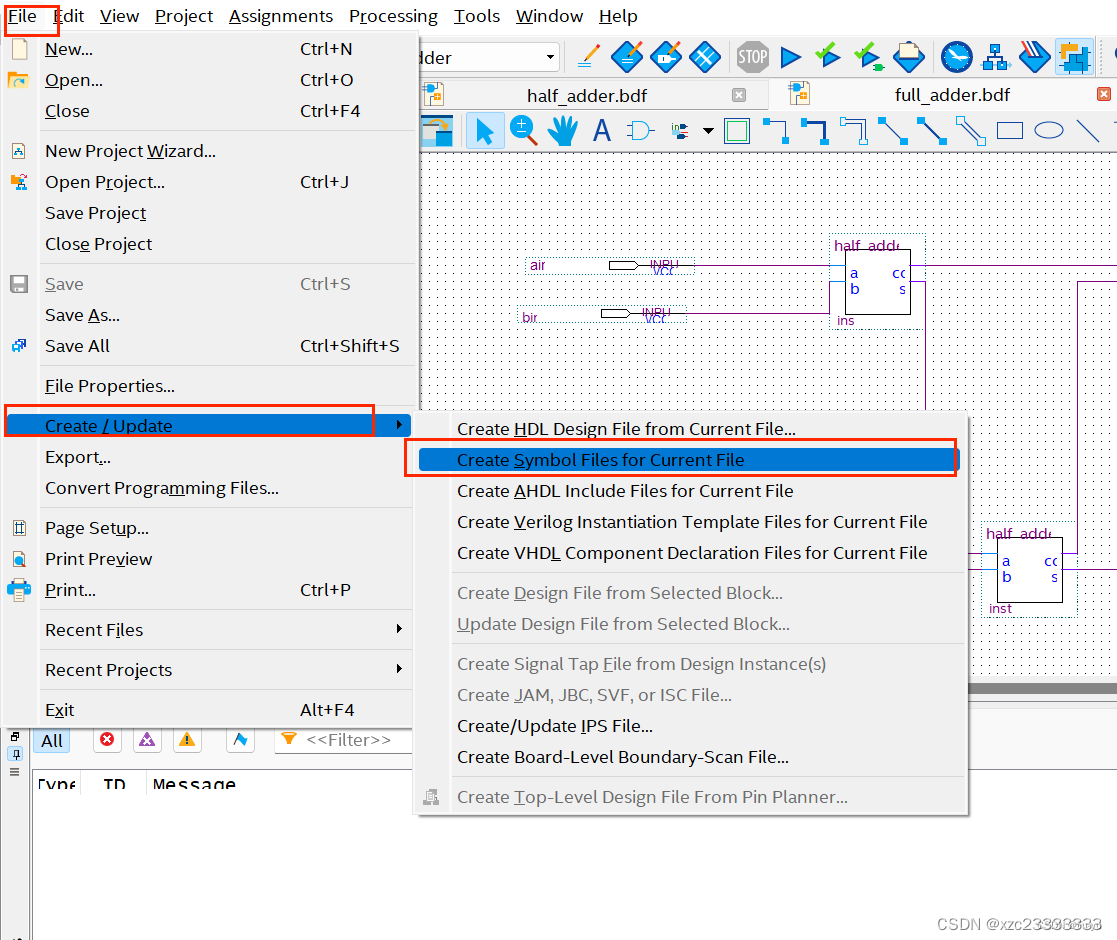

将full_adder设置为可调用元件:

新建原理图文件:

点击File->New,然后选择Block Diagram/Schematic File,选择元件full_adder,并绘制原理图:

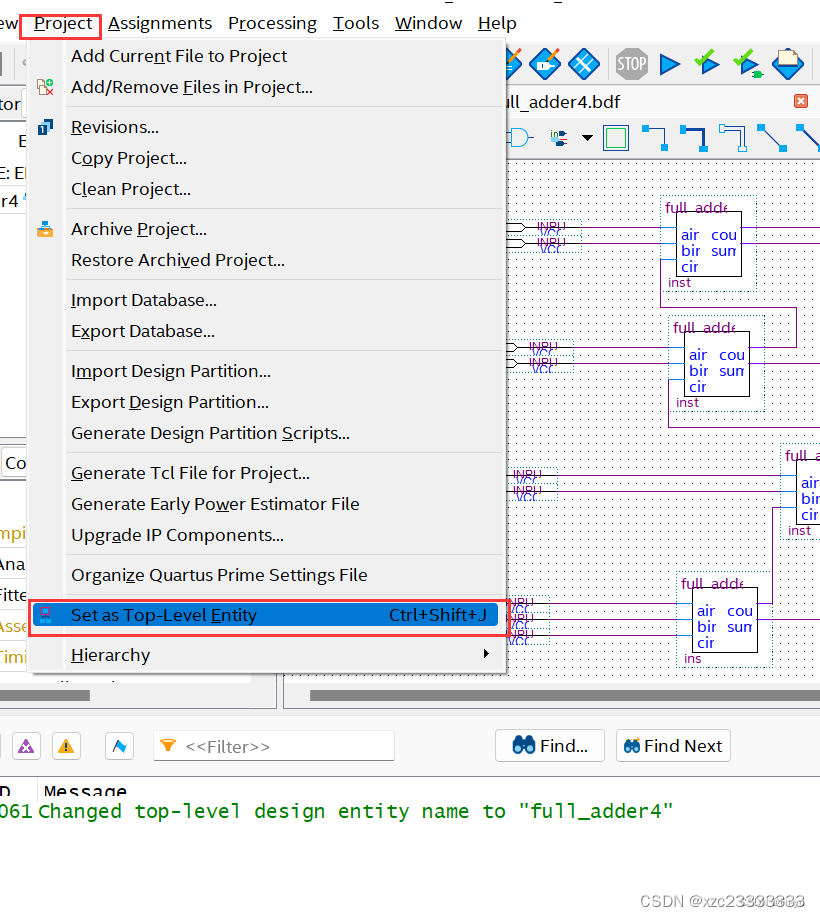

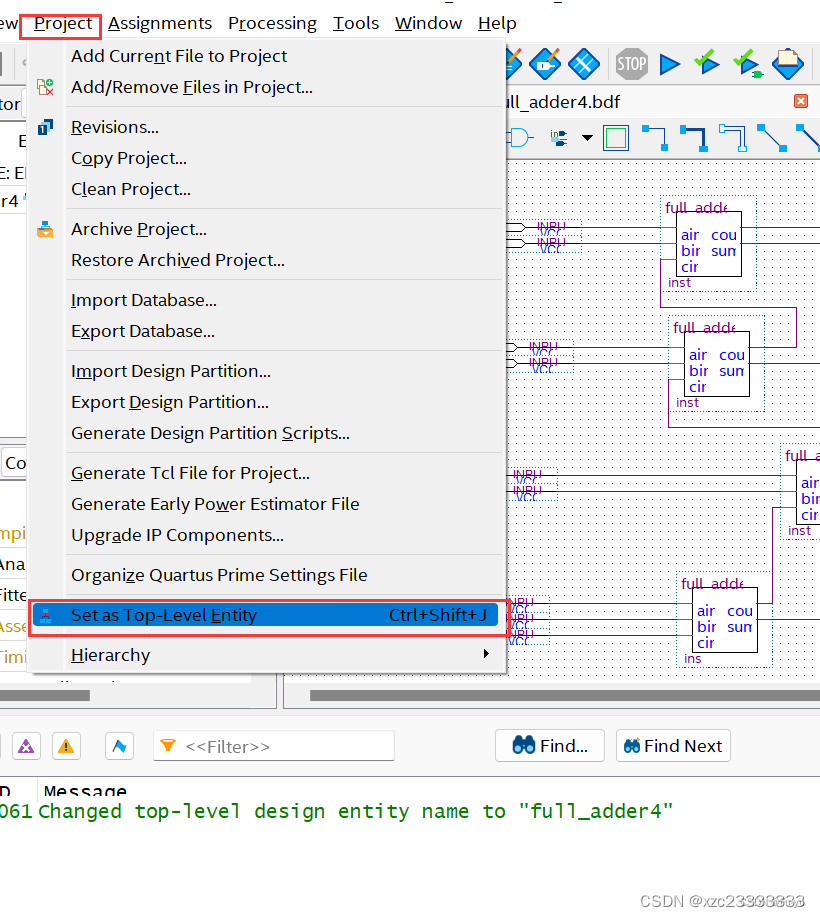

将原理保存至adder4文件夹下,并命名为full_adder4.bdf,将full_adder4.bdf设置为顶层文件并编译:

仿真:

保存文件并启动功能仿真:

2、Verilog编程方法设计4位全加器

module four (

num1,

num2,

cin,

cout,

sum

);

input [3:0] num1;

input [3:0] num2;

input cin;

output cout;

output [3:0] sum;

reg cout;

reg [3:0] sum;

reg add;

reg [1:0] cnt;

always @(num1 or num2 or cin)

begin

// 第一位

sum[0] = (num1[0] ^ num2[0]) ^ cin;

cout = (num1[0] & num2[0]) | (num2[0] & cin) | (num1[0] & cin);

add = cout;

// 第二位

sum[1] = (num1[1] ^ num2[1]) ^ add;

cout = (num1[1] & num2[1]) | (num2[1] & add) | (num1[1] & add);

add = cout;

// 第三位

sum[2] = (num1[2] ^ num2[2]) ^ add;

cout = (num1[2] & num2[2]) | (num2[2] & add) | (num1[2] & add);

add = cout;

// 第四位

sum[3] = (num1[3] ^ num2[3]) ^ add;

cout = (num1[3] & num2[3]) | (num2[3] & add) | (num1[3] & add);

add = cout;

end

endmodule

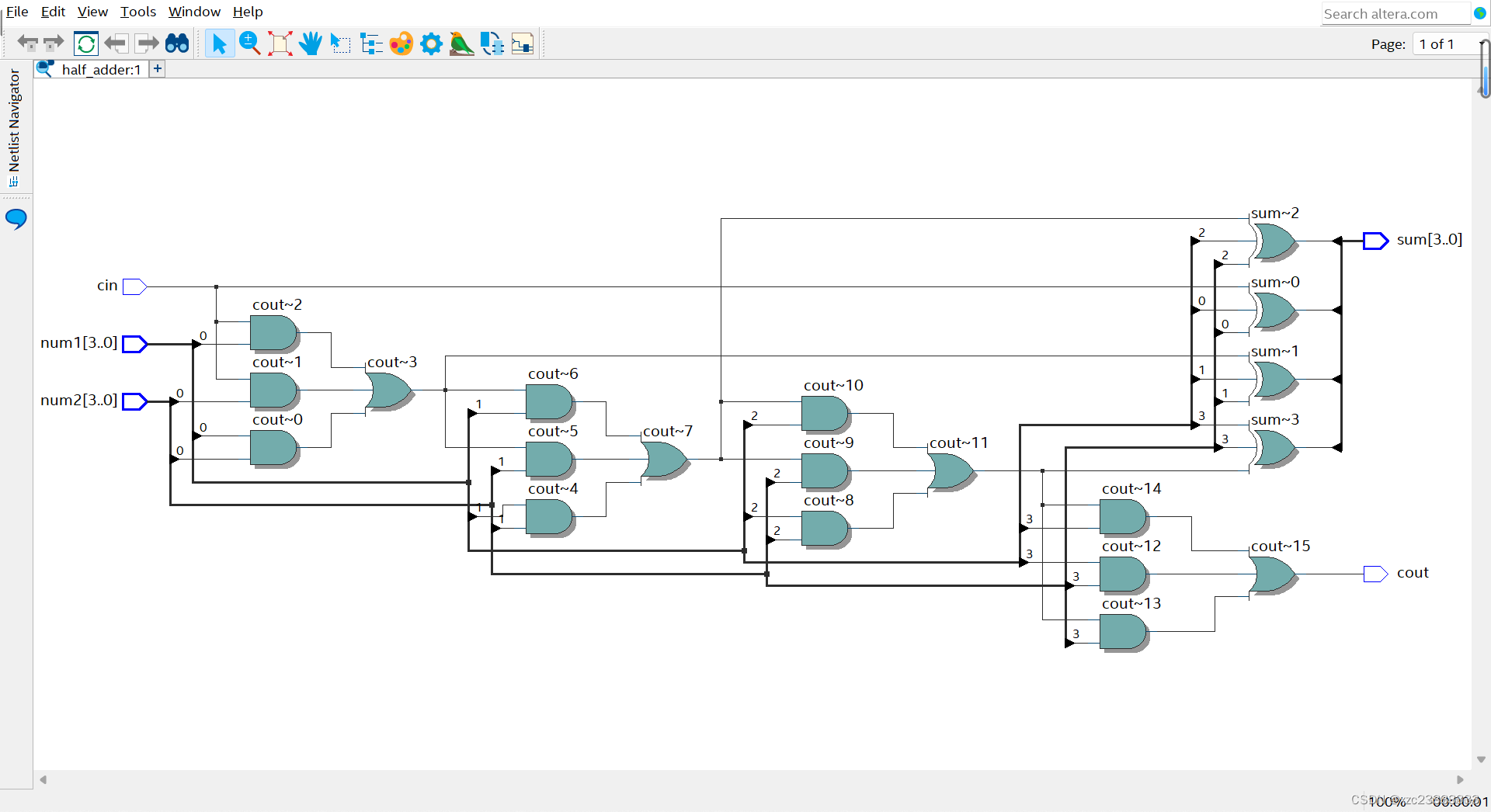

保存并编译,此时编译无误可以通过tool->Netlist Viewers->RTL Viewer,查看电路图:

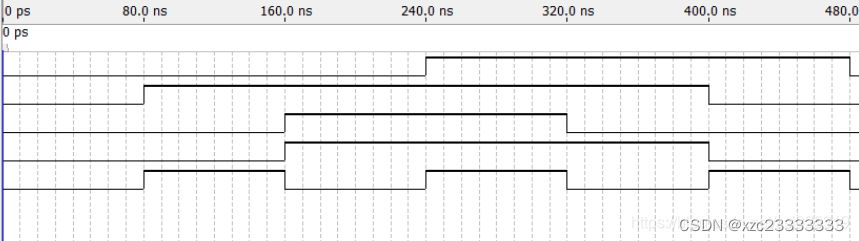

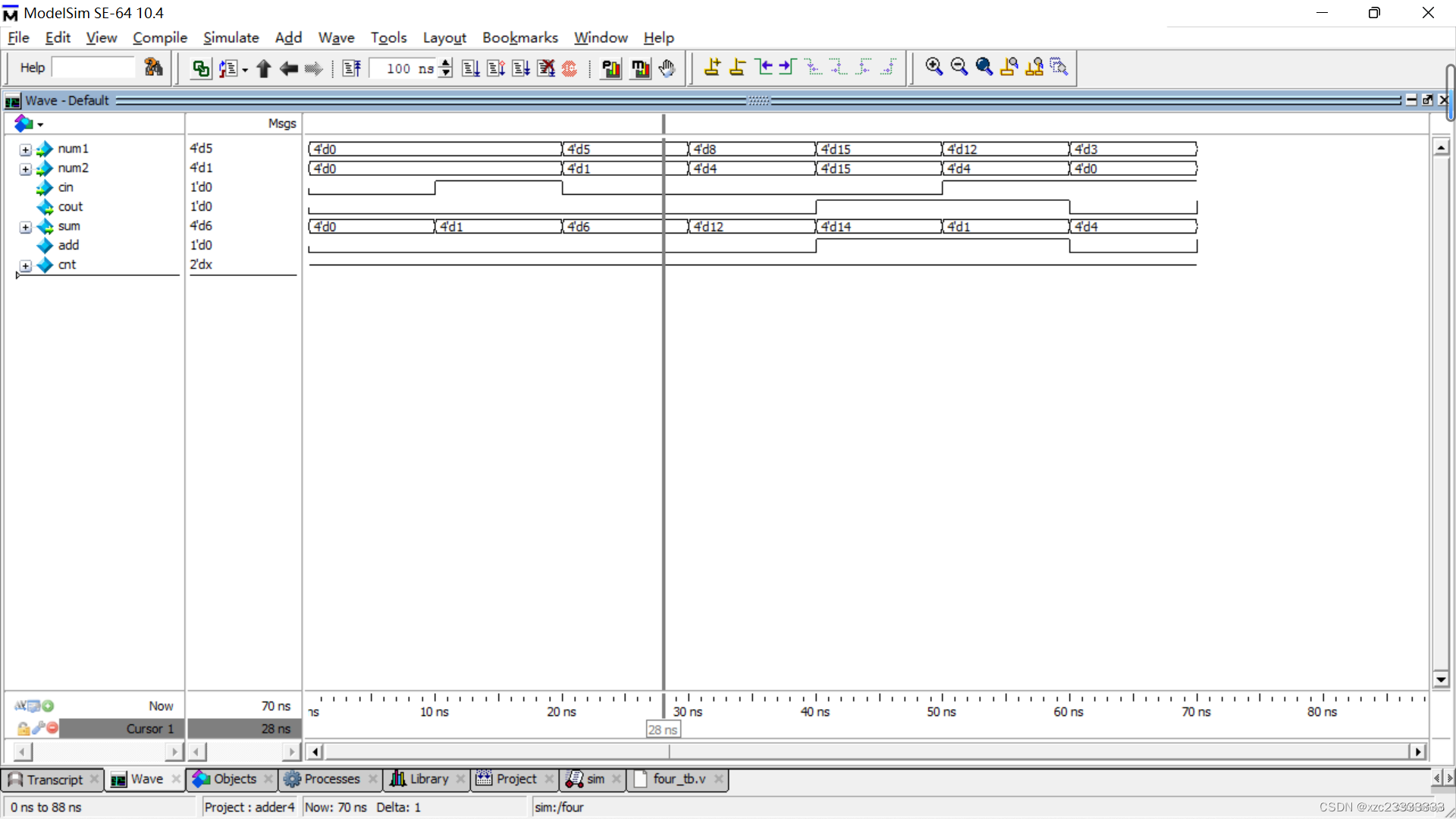

使用modelsim进行验

module four_tb ();

reg [3:0] num1;

reg [3:0] num2;

reg cin;

wire cout;

wire [3:0] sum;

four uut(

.num1(num1),

.num2(num2),

.cin (cin),

.cout(cout),

.sum (sum)

);

initial

begin

num1 <= 4'b0000; num2 <= 4'b0000; cin <= 0;

#10 num1 <= 4'b0000; num2 <= 4'b0000; cin <= 1;

#10 num1 <= 4'b0101; num2 <= 4'b0001; cin <= 0;

#10 num1 <= 4'b1000; num2 <= 4'b0100; cin <= 0;

#10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 0;

#10 num1 <= 4'b1100; num2 <= 4'b0100; cin <= 1;

#10 num1 <= 4'b0011; num2 <= 4'b0000; cin <= 1;

#10 num1 <= 4'b1111; num2 <= 4'b1111; cin <= 1;

end

endmodule

验证结果:

最后上板验证

三、总结

用Quartus-ll 来仿真很方便,有一定的数字电路基础后,再来使用这个软件来仿真会熟悉很多。

7282

7282

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?