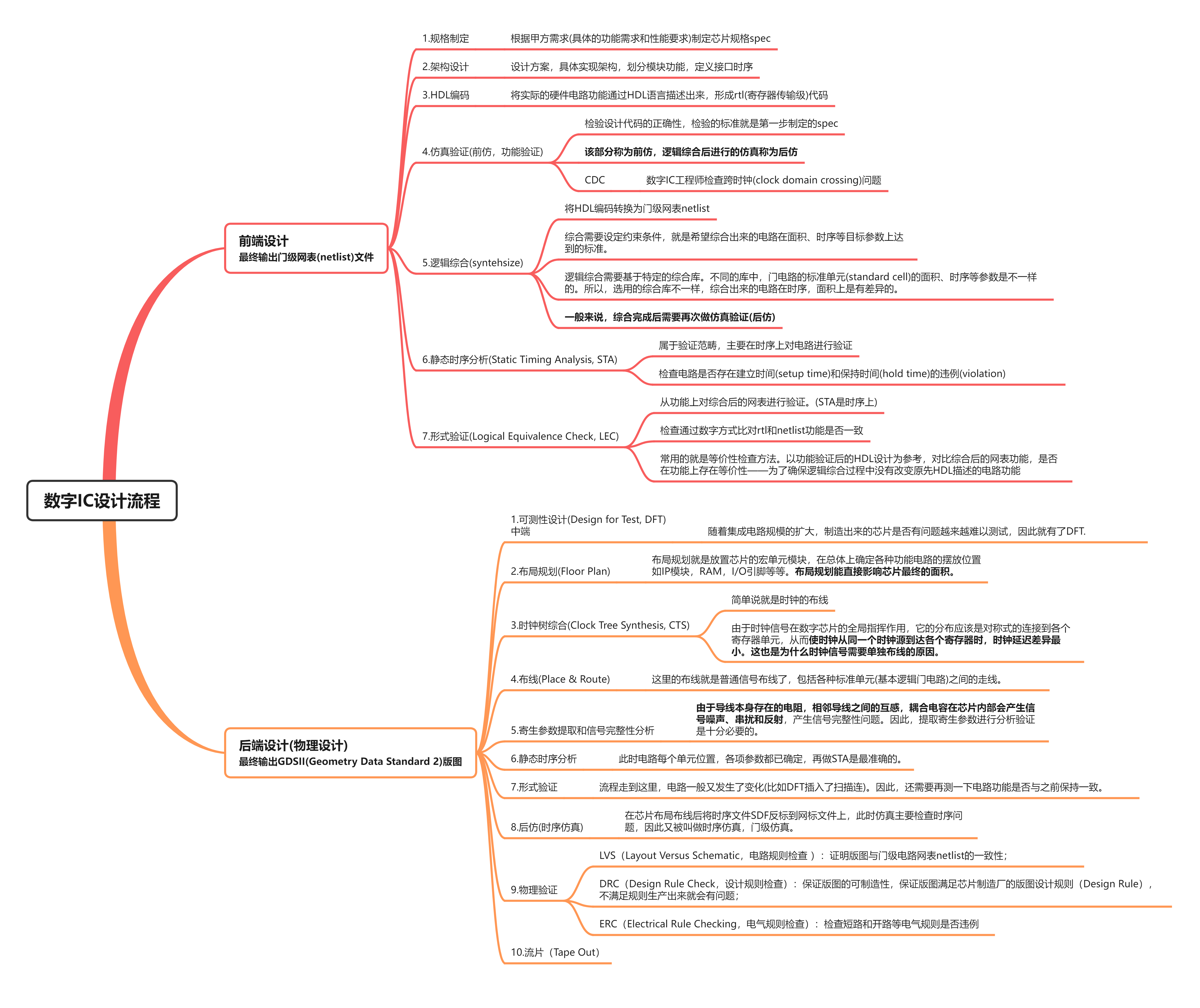

芯片设计全流程

概述

Q:后仿和逻辑综合后的STA有什么区别?STA后为什么还要进行后仿?

A:

1.和STA互补,分析STA中无法分析的路径。主要有异步时钟,false path,multicycle path。

2.对DFT的测试向量进行仿真

3.防止SDC文件给的不完备

4.功耗分析更加准确。动态仿真提供用于功耗的波形分析,比如开关因子的计算更加准确(switching factor)。

GLS can catch issues that static timing analysis (STA) or logical equivalence tools are not able to report. The areas

where GLS is useful include:

- Overcoming the limitations of STA, such as:

–The inability of STA to identify asynchronous interfaces

–Static timing constraint requirements, such as those for false and multi-cycle paths

- Verifying system initialization and that the reset sequence is correct

- DFT verification, since scan-chains are inserted after RTL synthesis

- Clock-tree synthesis

- For switching factor to estimate power

- Analyzing X state pessimism or an optimistic view, in RTL or GLS

Gagandeep Singh, Cadence Design Systems, Inc. Gate-Level Simulation Methodology.

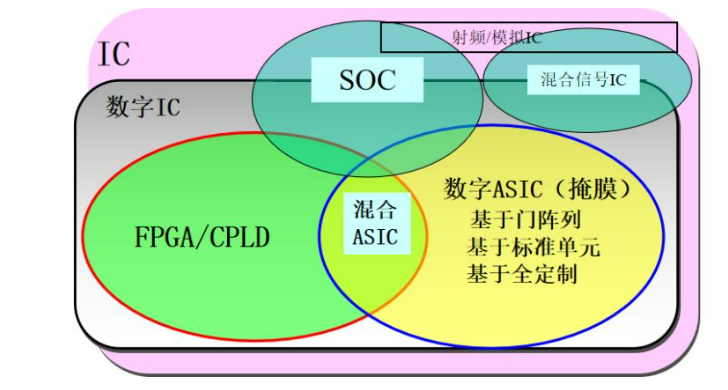

IC设计分类

IC设计可以粗分为数字IC设计和射频/模拟IC设计;数字IC设计又可分为ASIC设计和FPGA/CPLD设计;此外还有一部分IC设计采用数模混合设计,如:SOC设计和数模混合信号IC设计。

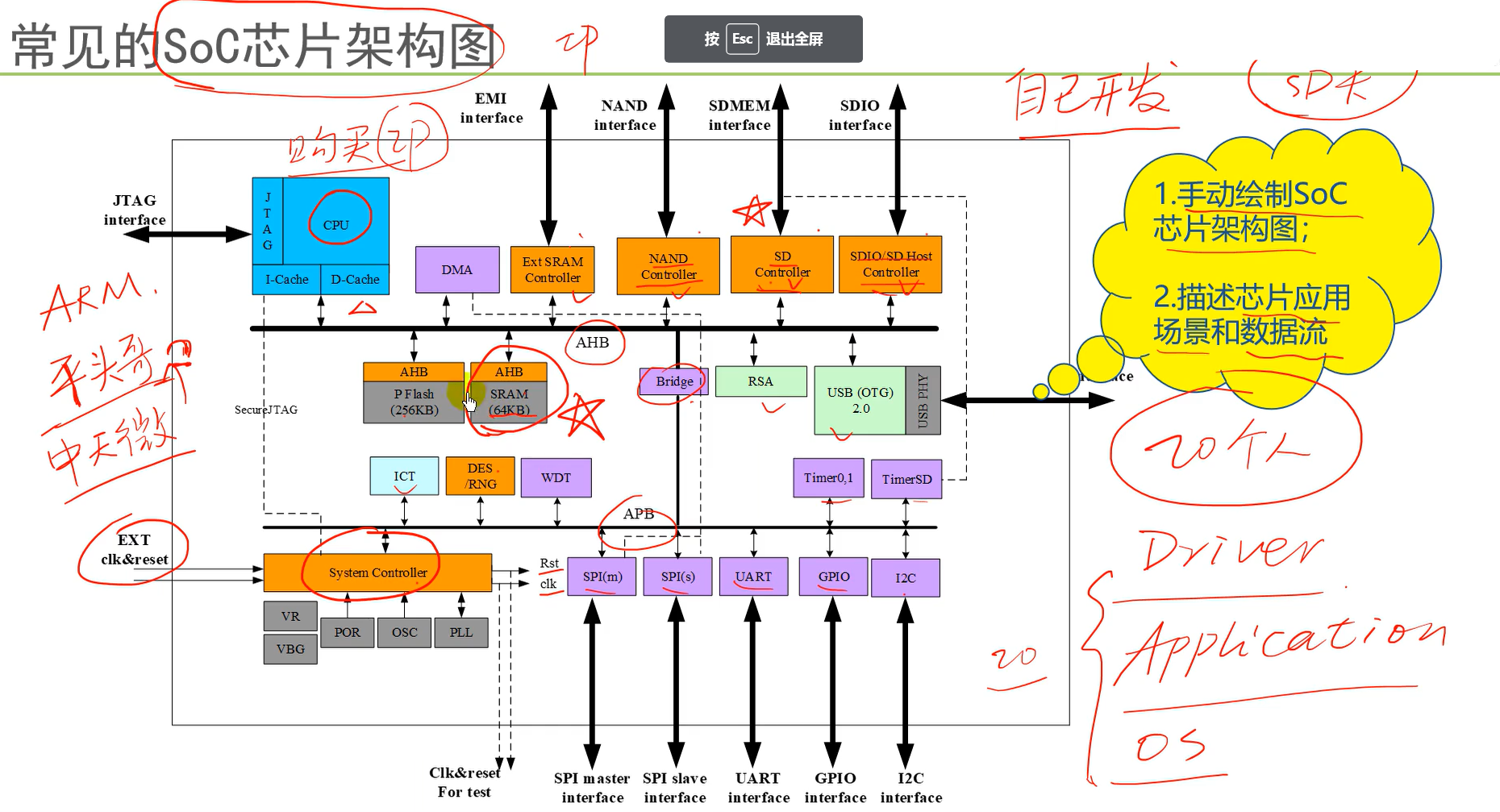

关于数字IC中的ASIC与FPGA/CPLD的区别:ASIC(Application Specific Integrated Circuit,专用集成电路):需制作掩模,设计时间长,硬件不能升级;芯片面积小,性能可以得到较好的优化;适合芯片需求量大的场合:片量用于平摊昂贵的光罩掩模制版费,降低单片生产成本。FPGA/CPLD(Field Programmable Gate Array,现场可编程门阵列 / Complex Programmable Logic Device,复杂可编程逻辑器件):不需要后端设计/制作掩模,可编程;开发门槛较低,设计时间较短,可方便和快速地升级优化硬件;芯片面积大,性能不够优化 ;适合芯片需求量小的场合:不用支付昂贵的光罩掩模制版费。作为数字ASIC设计流程中的必要步骤:ASIC设计中前端设计的FPGA原型验证(HDL功能验证)。模拟/射频IC:处理模拟信号,规模远不如数字IC,放大器( RF放大器、中放、运放、功放);比较器;振荡器;混频器;模拟PLL;稳压稳流源等数模混合信号IC: ADC、DAC;某些Driver;电源管理;等等SOC:System on Chip(系统集成电路,片上系统)

设计

- rtl

- 设计工程师要懂低功耗设计方法,跨时钟域的解决方案,面积,功耗,逻辑综合

验证

- 检验rtl级的HDL设计是否实现了Spec需要的功能等,保证设计代码的正确性;

- 验证工程师要懂设计,能看懂rtl,能够理解设计的各种方法;

- 作为soc验证工程师,要了解soc芯片中各个IP的功能。

- 包括regression,分阶段验证(rtl/gate/postsim),硬件原型验证(当设计的ip所需门电路很多,比如十亿个门电路,用EDA仿真太慢了,通过FPGA或硬件加速平台进行验证)

中端

- 逻辑综合:将描述电路的RTL级HDL转换到门级电路网表netlist的过程;根据该电路性能的要求(限制),在一个由制造商提供的包含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个门级逻辑网络结构的最佳实现方案,形成门级电路网表netlist;

- 会用到synthesis(逻辑综合),formality(形式验证,就是说rtl转为netlist之后,如何保证netlist功能和rtl功能是一致的),STA(静态时序分析,验证门级逻辑网络结构netlist的时序是否正确),DFT等技术

后端

- 布局布线:将门级电路网表(netlist)实现成版图(layout),输出GDSII文件。APR(Auto Place & Route) PR(placement and routing布局布线)

- 版图验证(PV,physical verification):包括DRC,LVS和ERC;

- DRC(Design Rule Check,设计规则检查):保证版图的可制造性,保证版图满足芯片制造厂的版图设计规则(Design Rule),不满足规则生产出来就会有问题;

- LVS(Layout Versus Schematic,电路规则检查 ):证明版图与门级电路网表netlist的一致性;

- ERC(Electrical Rule Checking,电气规则检查):检查短路和开路等电气规则是否违例

一些专业名词

在芯片设计中,EC0(Enginering hange 0rder)、PR(Place and Route)、和**PG(Post-ayout eneration) **网表是三个重要的概念,它们分别表示设计修订、布局布线以及布局后生成的网表:

EC0(Enginering hange 0rder)网表: E0是指在片设计流程,当设计已经完成或在进一步验证阶段时,可能会发现一些需要修改或优化的问题。这些问题可能是设计缺陷、性能改进、功耗优化等。EC0网表是经过设计修订后的版本,用于实现这些修改或优化。EO网表通常是通过更新设计原始网表或设计文件来实现的。

PR(Place ad Route)网表:是芯片设计中的一个重要步骤,用于将逻元素 (刻门、寄存器等)放置在芯片布局上,并进行连线 (Bouting)以实现物理设计。PR网表是经过布局和连线后的版本,它表示了逻辑元素在芯片布局中的位置以及它们之间的物理连线。PR网表用于后续的时序分析、功耗分析等验证步骤。

PC(Pot-ayout enerat00)网表:PG网表是在物理设计完成后生成的最终版本的网表,在PR阶段,布局布线工具会生成初步的网表,但在后续的布局布线优化和序收敛过程中,可能会进行一些微调和修正。PG网表是经过这些优化和修正后的最终网表,用于进一步的验证、仿真和制造流程。

综上所述,ECO网表是经过设计修订后的版本,PR网表是经过布局和连线的版本,PC网表是最终优化后的版本,它们分别代表了芯片设计的不同阶段和不同层次的网表信息。

7209

7209

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?