500MHz频率源设计(西电通院高频大作业)

注意:阅读时发现空白,稍等图片加载

关于本文章配套的PPT、报告以及工程文件可在链接下载:https://download.csdn.net/download/yifantan/85940145

文章目录

题目要求(21年下学期)

1、设计目的

掌握数字锁相频率源芯片ADF4351的使用;

频率源输出最佳匹配方法;

数字频率源性能评判方法及指标测量;

2、设计任务

采用ADF4351芯片设计一个数控频率源,要求输出频率100MHZ-550MHZ,输出信号幅度-5dbm-8 dbm;相位噪声:优于-70dBc/Hz@1kHz;参考频率源:10MHz。

3、注意:调整输出电平的方法

芯片输出信号电平和信号频率有关,调整输出回路器件参数,使输出回路反射系数最小;

芯片输出功率支持软件编程控制,可分三个输出量级;

如需要输出大于10dBm信号,可在输出端增加放大器。

| 下面从完整报告方面说一下这个实验 |

一、设计目的

1.掌握数字锁相频率源芯片ADF4351的使用;

2.频率源输出最佳匹配方法;

3.数字频率源性能评判方法及指标测量;

二、设计任务

采用ADF4351芯片设计一个数控频率源,要求输出频率100MHZ-550MHZ,输出信号幅度-5dbm-8 dbm;相位噪声:优于-70dBc/Hz@1kHz;参考频率源:10MHz。

注意:调整输出电平的方法

芯片输出信号电平和信号频率有关,调整输出回路器件参数,使输出回路反射系数最小;

芯片输出功率支持软件编程控制,可分三个输出量级;

如需要输出大于10dBm信号,可在输出端增加放大器。

三、芯片信息

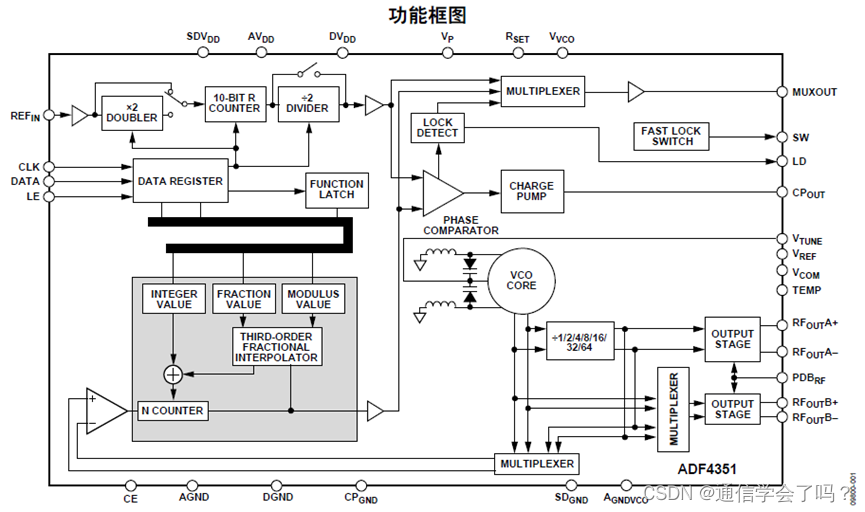

本实验采用ADI公司的ADF4351锁相环芯片。

ADF4351结合外部环路滤波器和外部参考频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。

ADF4351具有一个集成电压控制振荡器(VCO),其基波输出频率范围为2200 MHz至4400 MHz。此外,利用1/2/4/8/ 16/32/64分频电路,用户可以产生低至35 MHz的RF输出频率。对于要求隔离的应用,RF输出级可以实现静音。静音功能既可以通过引脚控制,也可以通过软件控制。同时提供辅助RF输出,且不用时可以关断。

所有片内寄存器均通过简单的三线式接口进行控制。该器件采用3.0V至3.6V电源供电,不用时可以关断。

根据官网的芯片信息,其芯片功能框图如下:

由于其详细技术规范内容篇幅过长,所以只在这里列举关键系统参数。

关键系统参数:

输出频率范围:35 MHz至4,400 MHz

VCO灵敏度(压控增益):40MHz/V

电荷泵电流:5mA

最小RF输出功率:−4dBm

最大RF输出功率:5dBm(输出功率可以3 dB步进编程)

四、设计过程及结果分析

1. PLL仿真计算环路滤波器

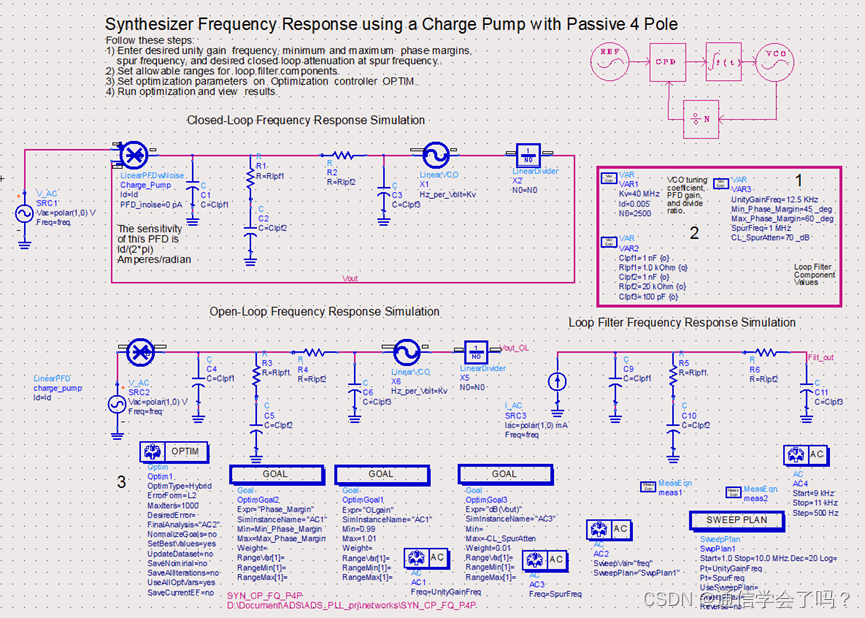

我们使用ADS的Design Guide设计工具箱来进行辅助设计,这里使用ADS2008进行设计仿真。

该仿真可以帮助我们应用实际的系统参数和设计目标进行元件参数设定,以便找到最佳的设计参数,以使得系统满足设计目标。

使用PLL工具箱后,我们得到如下的仿真原理图:

该原理图可以分为五大部分。左上角的电路图用于仿真系统闭环特性,右上角的变量设置区用于设置环路各个参数。中间靠左的电路图用于仿真系统开环特性,中间靠右的电路图用于仿真环路滤波器频率响应。最下方的一系列器件为仿真器、优化器、优化目标以及公式编辑器。

1)系统变量设置

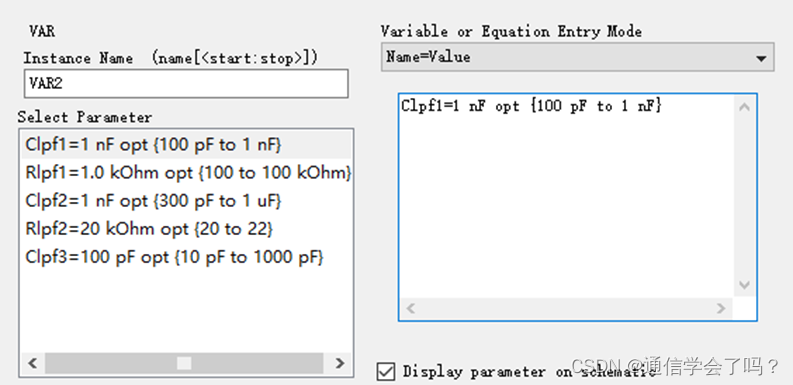

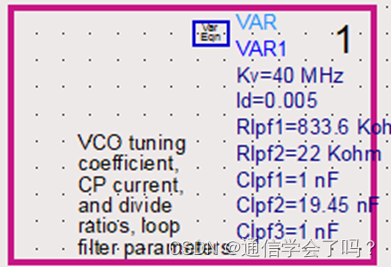

变量列表VAR1内存储的是环路各模块的参数,Kv是VCO调谐增益,这里改为40MHz.由于ADF4351是整数分频芯片,因此鉴相频率应选为系统频率间隔200kHz。射频分频器的分频比应设置为2500(500MHz/200kHz=2500),芯片的电荷泵电流选取5mA。相应的更改Kd和N0。

变量列表VAR2内存储的是环路滤波器的器件值。这些器件值稍后将通过ADS的自动优化计算出来,这里需要预先指定器件变动的初始值和优化范围,设置后如下图所示:

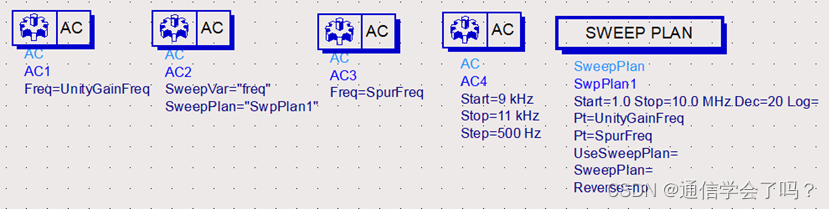

2)仿真参数配置

扫描计划(SWEEP PLAN)、交流仿真器 (AC)配置如下图所示

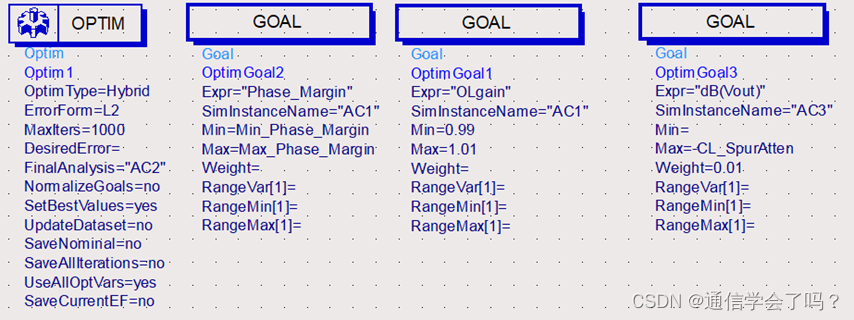

优化目标(GOAL)和优化器(OPTIM)具体设置如下

扫描计划用来设定扫描的范围,交流仿真器用于设定该原理图采用小信号交流仿真,优化器用于设定优化算法的类型。优化目标用于设置优化仿真的收敛条件。至此,就完成了原理图各个模块参数的设置。

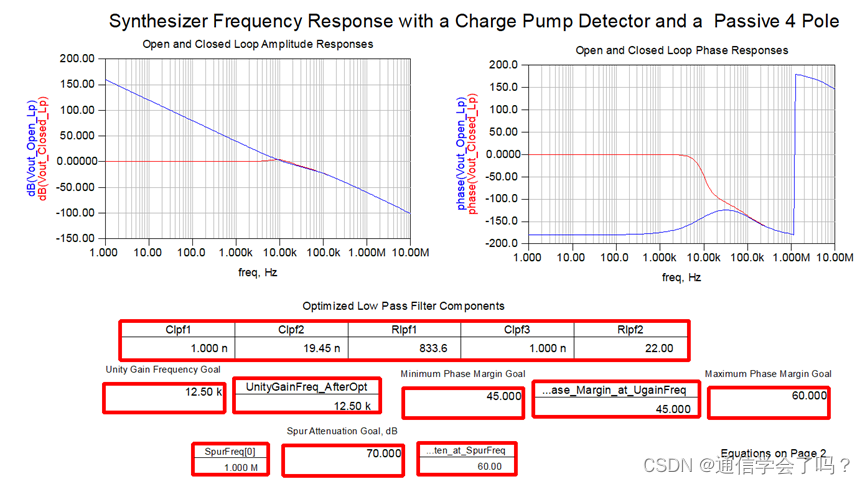

随后进行仿真,得到如下仿真结果:

2. 估算相位参数

同样使用ADS的Design Guide设计工具箱来进行辅助设计,该仿真可以计算出系统的相位参数,验证是否满足题中优于-70dBc/Hz@1kHz的要求。

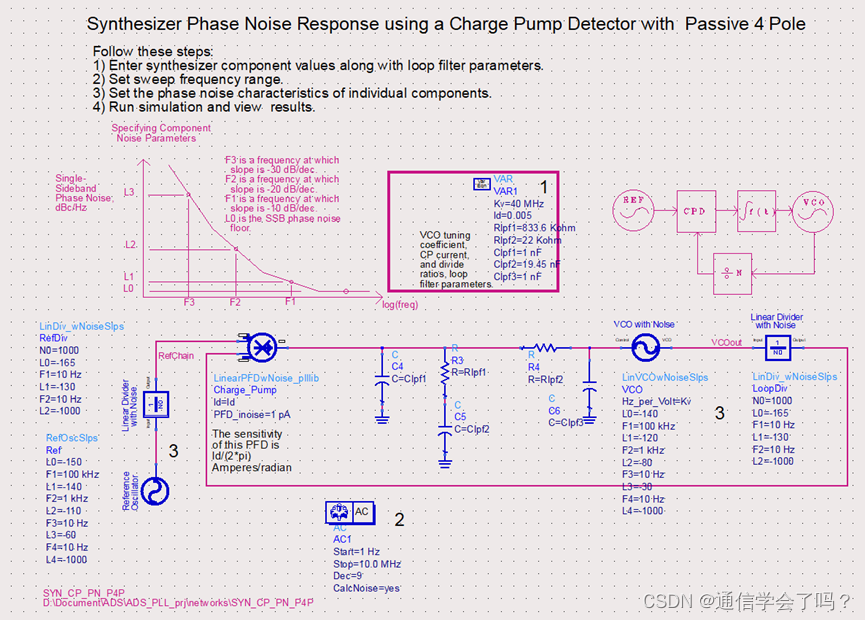

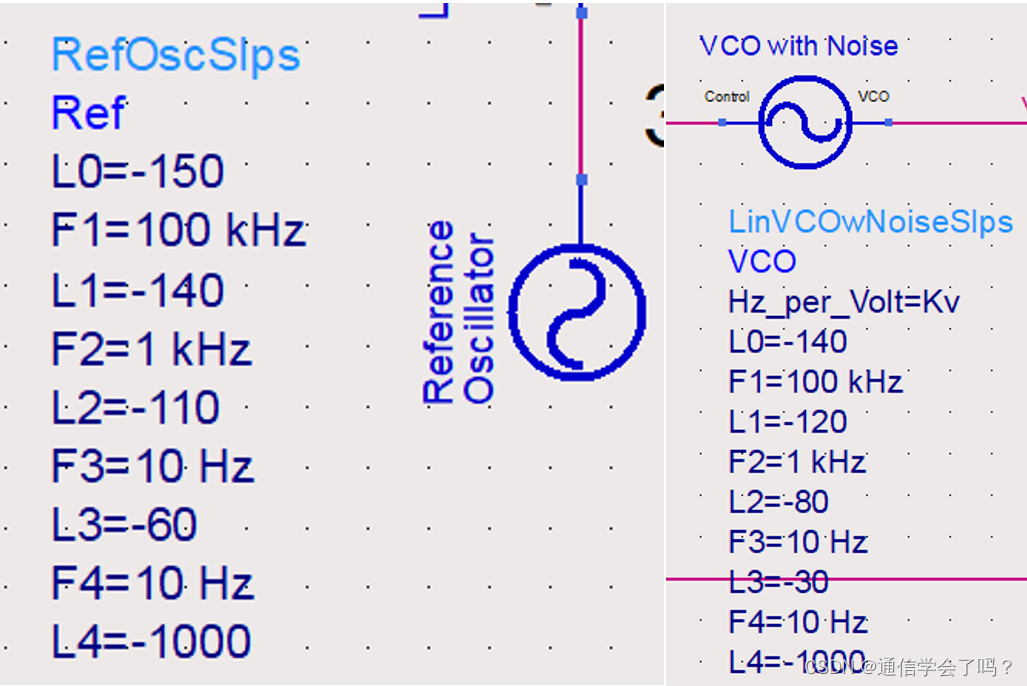

使用PLL工具箱后,我们得到如下的仿真原理图:

其中,上方红框是变量设置区,中间电路部分是PLL环路模型,下方为仿真器。我们主要根据计算出的环路滤波器和实际的系统参数和设计目标进行元件参数配置。

首先根据上述环路滤波器的优化结果设置VAR1的参数

接下来,需要设置PLL环路模型中各个模块的参数,根据使用的参考源与VCO的实际性能修改对应模块的参数。

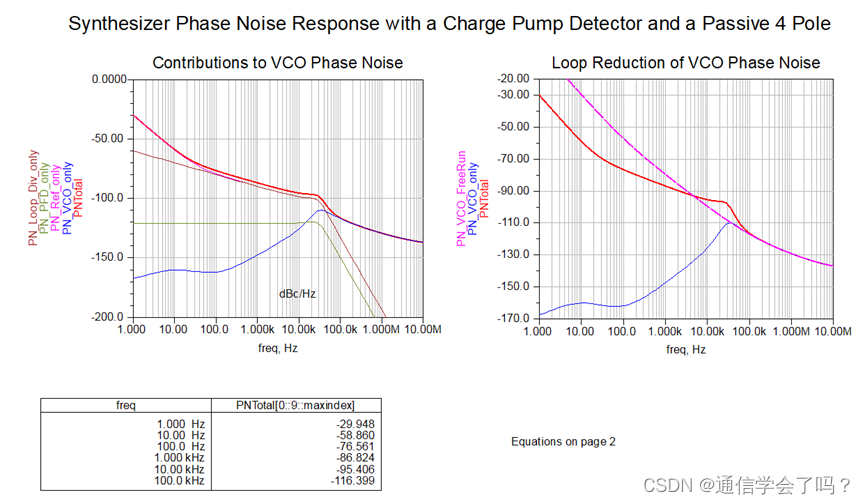

运行仿真可以得到结果:

可以看到相位噪声为-86.814dBc/Hz@1kHz,优于-70dBc/Hz@1kHz,符合设计要求。

3. 输出匹配

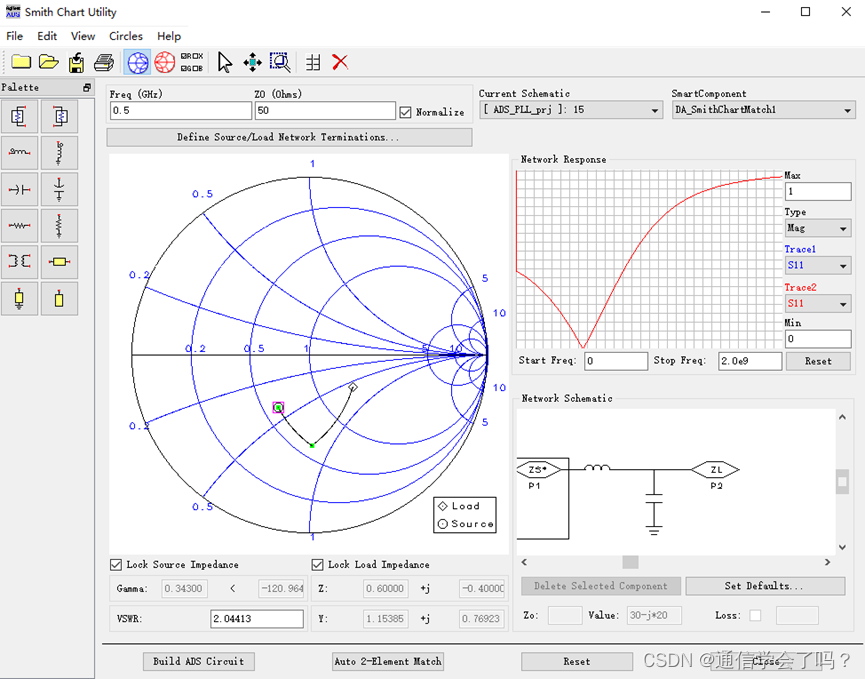

我们使用Smith圆图进行输出匹配。输出匹配可以使信号能够尽可能的作用于负载,而不是被反射回去,以减少反射系数。

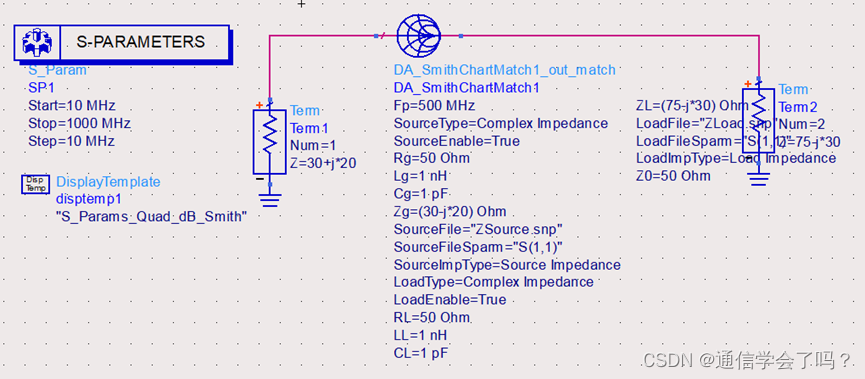

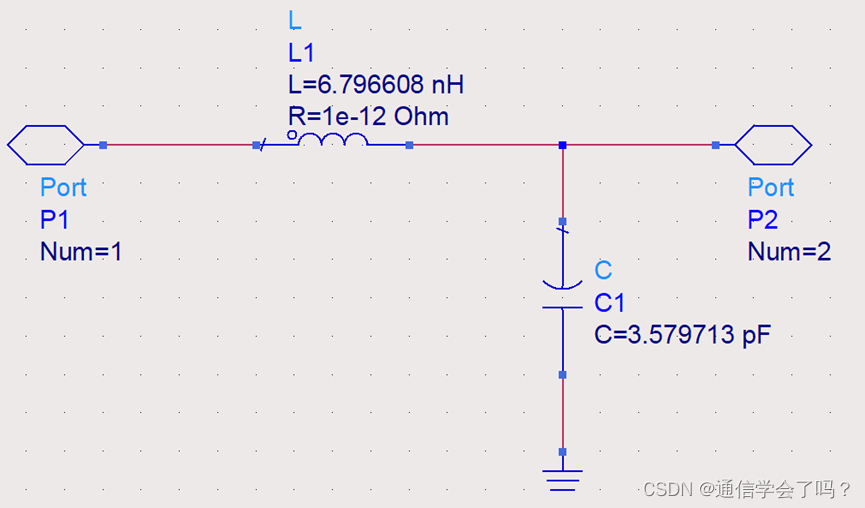

仿真电路图如下:

通过Smith圆图的设置和自动优化,可以很容易得出最佳的参数值。

通过Smith圆图的设置和自动优化,可以很容易得出最佳的参数值。

Smith圆图设置如下:

得出的最佳输出匹配电路如下图:

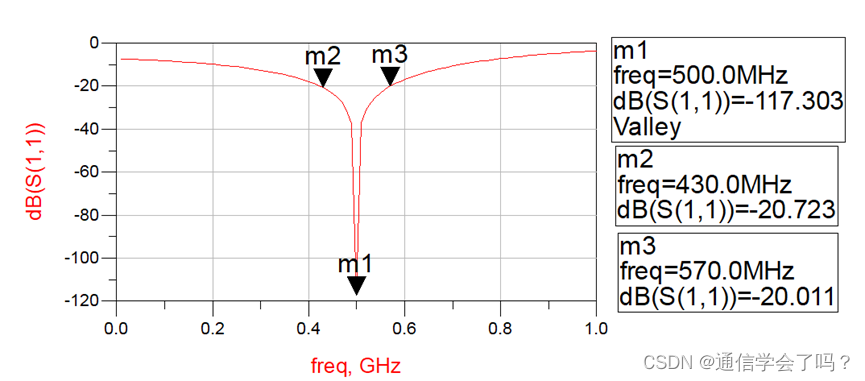

通过仿真,可以得到S11的回波损耗曲线图:

可以看出,在500MHz处,它的回波损耗为-117.303dB,且优于-20dB的频率范围为430到570MHz,性能表现良好。

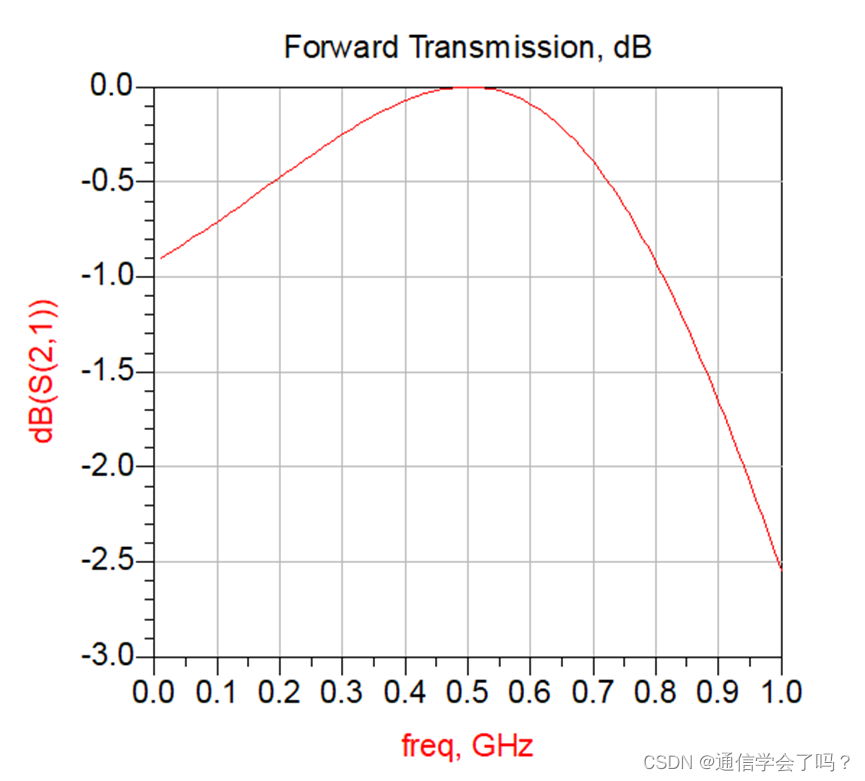

而输入端到输出端的传输系数,即匹配网络的增益曲线仿真如下图:

可以看到,在500MHz处输出匹配网络增益为0dB,由于芯片输出功率为−4dBm到5dBm(以3 dB步进编程),所以我们得到的最终输出功率为−4dBm到5dBm。满足设计要求。

至此,我们成功设计出了符合目标要求的频率源。

4. 寄存器配置

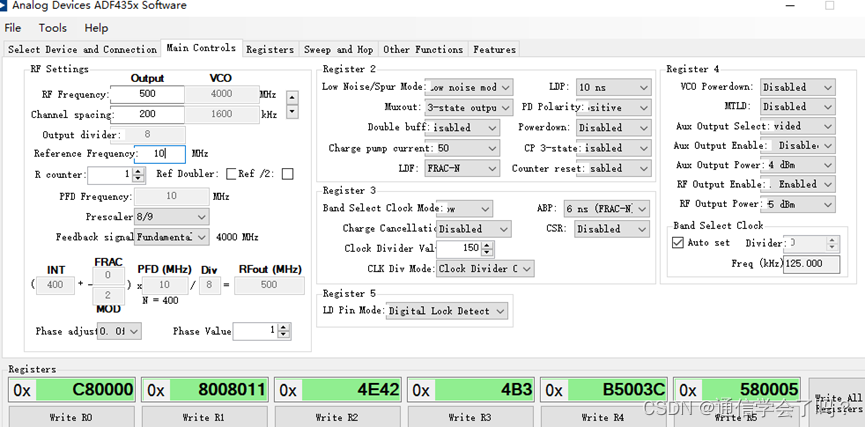

在实物设计中,需要向ADF4351芯片的寄存器中写入合适的数据,以调试芯片,并获得对应的分频。所以,我们使用其官网提供的软件计算出了寄存器的值。

可以得到,寄存器的值分别为C80000、8008011、4E42、4B3、B5003C、 580005(十六进制)。

五、心得体会

本次实验的难点在于软件的实验和资料的短缺,这使得我们一开始有点无从下手的感觉。我们走向了一个错误的方向:以为可以将ADI官网下载的IBIS模型直接导入到ADS中,从而浪费了很长时间。

后来,好在我们找到了《ADS2008射频电路设计于仿真实例》这本书,并根据书中的介绍和指导一步步搭建了实验电路,并学会了ADS仿真的基本操作知识。我们实验ADS软件Design Guide中的PLL向导简化了很多设计过程,并仔细研究了芯片手册中的有关参数,对其进行分析、仿真,从而完成了本次大作业。

从这次作业中,我们对锁相环有了更深的了解,学会了如何使用锁相环设计一个频率发生器,以及学会了ADI公司ADF4351芯片的使用方法。除此之外,我们还学会了如何使用ADS来进行参数优化、参数仿真、输出匹配。收获颇丰!

关于本文章配套的PPT、报告以及工程文件可在链接下载:https://download.csdn.net/download/yifantan/85940145

3643

3643

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?