最近对存储器单元比较好奇,学习一下。

静态随机存取存储器(Static Random Access Memory,SRAM)是一种随机存取存储器,只要保持通电,储存的数据就可以保持。而动态随机存取存储器(DRAM)所储存的数据就需要周期性地刷新。

“随机存取”意味着在 SRAM 单元阵列中,每个单元都可以按任何顺序读取或写入,无论最后访问哪个单元。

1.6T-SRAM cell

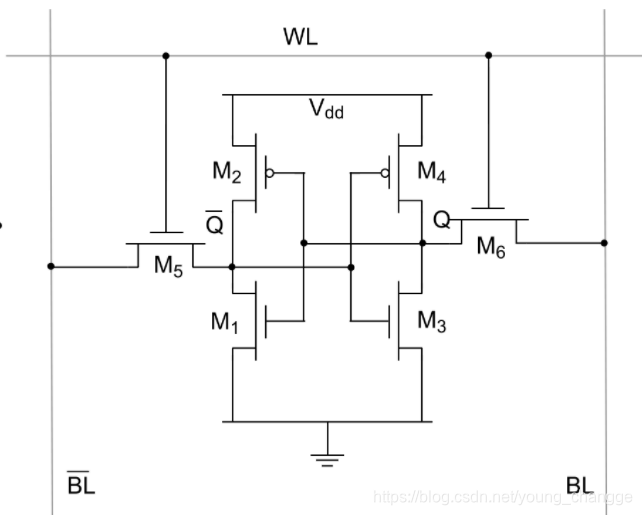

常见的SRAM的结构为6T-SRAM

其实等价于SR锁存器

6T,即由6个晶体管所组成,单元的核心由两个 CMOS 反相器(M1、M2、M3、M4)构成,其中每个反相器的输出电位作为输入馈送到另一个反相器。连接到M5、M6的gate信号是word line(缩写成WL),是用来控制SRAM bit-cell的开关信号,M5、M6一起打开或关闭。M5、M6的Drain端是读出或写入的bit line(缩写成BL)。

如图所示,由M1、M2组成一个inverter,由M3、M4组成另一个inverter,这两个inverter的output分别接到另一个inverter的input,构成一个latch,从而可以将数据锁住。从这里可以看出与SR锁存器实际是等价的。

SRAM的基本单元有3种状态:standby (电路处于空闲),reading(读)与writing(修改内容). SRAM的读或写模式必须分别具有"read

本文介绍了SRAM的基本结构和工作原理,重点解析了6T-SRAM单元,包括standby、读取和写入操作。6T-SRAM由6个晶体管构成,其核心是两个反相器形成的锁存器。读取时,通过位线的charge sharing和分压产生电压差,利用外部放大器读出数据;写入则通过改变位线状态来更新存储内容。

本文介绍了SRAM的基本结构和工作原理,重点解析了6T-SRAM单元,包括standby、读取和写入操作。6T-SRAM由6个晶体管构成,其核心是两个反相器形成的锁存器。读取时,通过位线的charge sharing和分压产生电压差,利用外部放大器读出数据;写入则通过改变位线状态来更新存储内容。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3528

3528

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?