最近从Xilinx 转型Lattice FPGA 开发,LATTICE开发环境很不习惯。研究了好长时间。把一些开发笔记分享一下。

Lattice DDR3 读写控制笔记

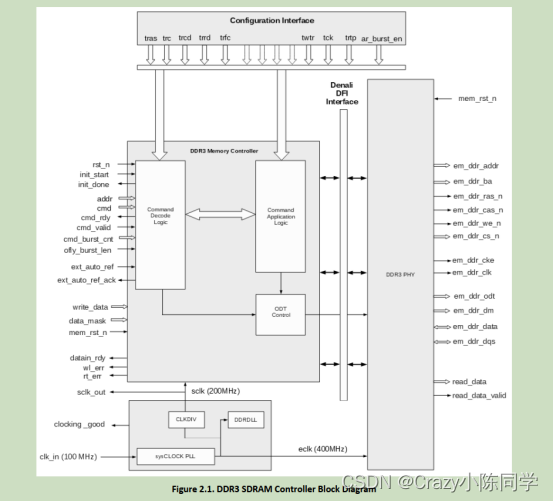

DDR3内存控制器主要由控制器核心逻辑模块和I/O逻辑模块两部分组成。

DDR3内存控制器由内存控制器(MC)、物理接口(PHY)和时钟同步模块(CSM)三个子模块组成。

DDR3 PHY模块为内存设备提供PHY接口。该块主要由LatticeECP3或

ECP5的DDR I/O原语,支持符合DDR3电气和时序要求。此外,该模块还包括内存初始化逻辑、写平衡逻辑、读逻辑和读写数据通道。

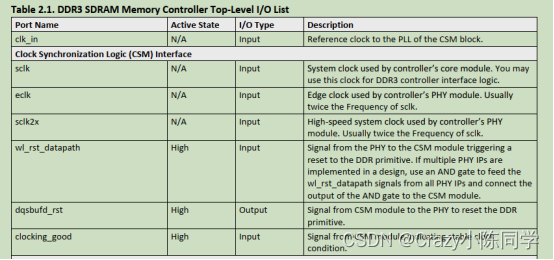

除了DDR3 SDRAM控制器IP核之外,还提供了一个单独的模块,称为时钟同步模块(CSM)。CSM为IP核生成所有的时钟信号,如系统时钟(SCLK)和边缘时钟(ECLK)

CSM逻辑确保对于产生2:1传动的IDDR和ODDR总线,ECLK到SCLK之间的域交叉边界保持相同。如果没有适当的同步,不同元素上的位顺序可能彼此不同步,整个总线被打乱。时钟同步确保所有DDR组件从完全相同的边缘时钟周期开始。

对于400 MHz的DDR3内存时钟操作,MC模块与200 MHz的系统时钟(SCLK),即I/O操作逻辑与400 MHz边缘时钟(ECLK)。这种工作时钟比和双数据速率的组合传输连接到一个用户端数据总线,其宽度是内存端数据总线的四倍。例如,32位的内存端数据宽度在用户端接口需要一个128位读数据总线和一个128位写数据总线。

User interface

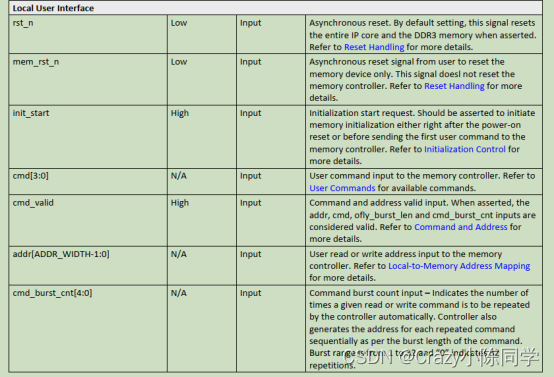

输入端口:

Rst_n

Mem_rst_n

Init_start : 初始化请求开始

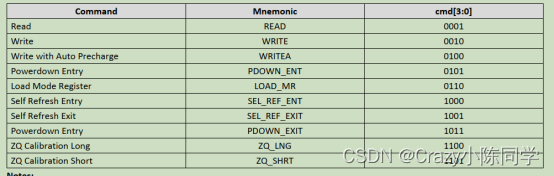

Cmd[3:0] :用户命令输入 READ:0001 WRITE:0010

Cmd_valid: 命令和地址的有效输入。当断言时,addr、cmd、ofly_burst_len和cmd_burst_cnt输入被认为有效。

Addr[addr_width-1:0]: 用户读或写地址输入到内存控制器。

Cmd_burst_cnt:命令突发计数输入-表示一个读或写命令被控制器自动重复的次数。控制器按照命令的突发长度顺序为每个重复的命令生成地址。突发范围为1 ~ 32,“0”表示32次。

Ofly_burst_len: 当前指令的即时突发长度。0 = bc4, 1 = bl8。只有当模式Reg0设置为动态模式时,此输入才有效。如果设置了该选项,则当cmd_valid和cmd_rdy值为高时,将对该输入进行采样。

Write_data[dsize-1:0]:将用户逻辑输入的数据写入内存控制器。用户端写数据的宽度是内存数据宽度的4倍.如ddr位宽32,则控制器数据为宽128

Data_mask: 数据掩码

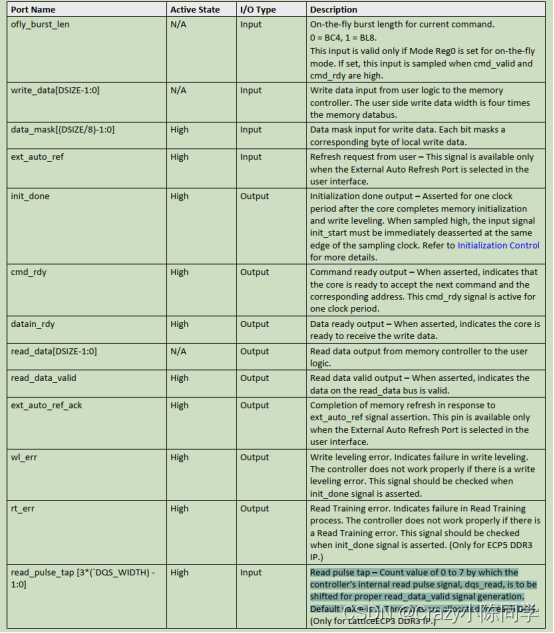

输出端口:

init_done:初始化完成输出——在核完成内存初始化和写调平之后的一个时钟周期内断言。

Cmd_rdy:Command ready输出—断言时,表示核已经准备好接受下一个命令和相应的地址。这个cmd_rdy信号在一个时钟周期内是活跃的,即脉冲信号,命令接收准备好。

Datain_rdy: 核数据接收准备好

Read_data: 核输出的用户读数据

Read_data_valid:数据输出有效标志

Wl_err:写水准测量误差。写调平失败。写均衡错误导致控制器工作异常。当断言init_done信号时,应该检查这个信号

Rt_err:读训练错误(仅用于ECP5)

Read_pulae_tap:INPUT读取脉冲点击-控制器内部读取脉冲信号dqs_read的0到7的计数值,通过该计数值进行移位以产生正确的read_data_valid信号。缺省值为2。每个DQS分配三个比特(仅用于ECP3)

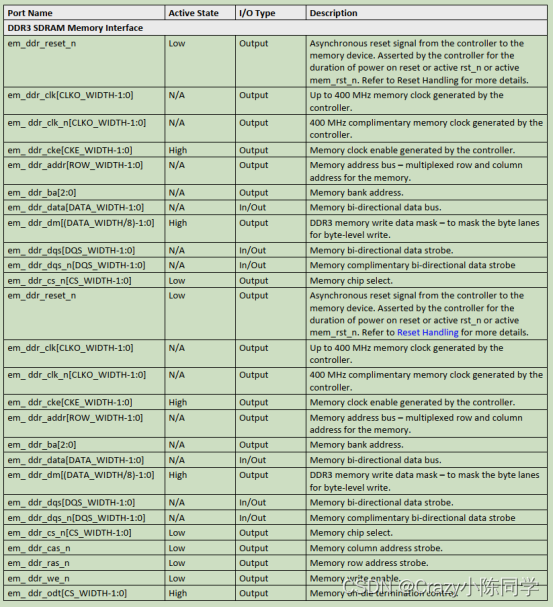

DDR3 SDRAM Memory interface

Em_ddr_reset_n:从控制器到存储设备的异步复位信号。

Em_ddr_clk:高达400mhz的内存时钟产生的控制

Em_ddr_clk_n:由控制器产生的400mhz内存时钟

Em_dde_cke:控制器产生的内存时钟使能

Em_ddr_addr:内存地址总线—用于内存的多路行和列地址

Em_ddr_ba[2:0]:bank地址

Em_ddr_data:内存双向数据总线

Em_dde_dm:DDR3内存写数据掩码——为字节级写屏蔽字节通道

Em_ddr_dqs:

Em_ddr_dqs_n:存储器双向数据频闪

Em_ddr_cs_n:存储器芯片选择

Em_ddr_reset_n:从控制器到存储设备的异步复位信号。

Em_ddr_cas_n:地址列选择

Em_ddr_ras_n:地址行选择

Em_ddr_odt:终端电压控制

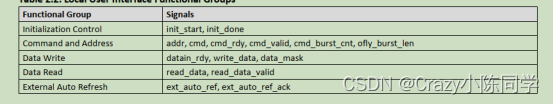

DDR3 SDRAM控制器IP核的本地用户界面由5个独立的功能组组成:

·初始化控制

·命令和地址

·数据写

·数据读

·外部自动刷新

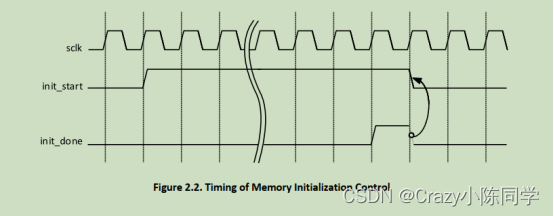

1.初始化

DDR3的内存设备需要初始化后才能被内存控制器访问。当用户界面断言init_start信号时,内存控制器启动内存初始化序列。一旦断言,init_start信号需要保持高电平,直到初始化过程完成。输出信号init_done在一个时钟周期内被断言为高,这表明核心已经完成了初始化序列,现在准备访问内存。一旦init_done在sclk的上升边缘被高采样,init_start信号必须被取消。其时序如下图所示:

2.控制命令和地址

内存初始化完成,内核将等待用户命令来设置和/或访问内存。

用户逻辑需要将命令和地址连同控制信号一起提供给核心。命令和地址通过以下过程传递到核心。

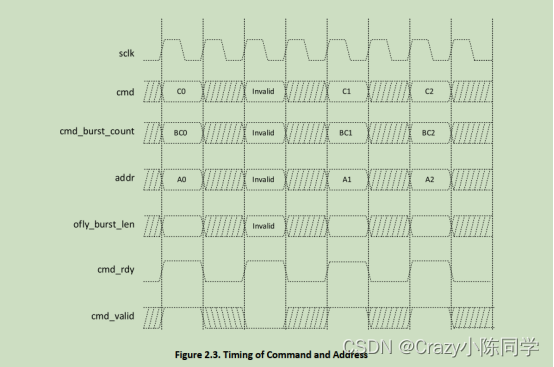

内存控制器核心通过断言cmd_rdy信号一个周期来通知用户逻辑它已经准备好接收命令。如果核心发现用户逻辑断言的cmd_valid信号,而它的cmd_rdy被断言,它将cmd输入作为有效的用户命令。通常,cmd_valid在采样cmd_rdy高的时钟上升边缘去断言。核心还接受addr输入作为有效的开始地址或模式寄存器编程数据,这取决于命令类型。除了addr输入,核心还接受cmd_burst_cnt和ofly_burst_len信号。如果cmd_valid没有断言,cmd和addr输入将无效,核心将忽略它们。cmd, addr, cmd_burst_cnt, ofly_burst_len和cmd_valid输入变得不关心cmd_rdy是去断言的。再次断言cmd_rdy信号以接受下一个命令。

核心通过每两个时钟周期断言一次cmd_rdy来确保突发长度为8的最大吞吐量,除非命令队列已满或内存接口(如AutoRefresh周期)上有干预。当核心处于命令突发操作时,大量占用数据总线。在此期间,核心防止cmd_rdy在命令突发完成之前被断言。当堆芯在命令突发模式,它可以通过内部复制命令来保持最大的吞吐量。的内存控制器最多重复指定的READ或WRITE命令32次。输入cmd_burst_cnt[4:0]用于设置给定命令的重复次数。核心允许命令爆发功能访问内存当前页面内的地址。当内核到达当前页的边界时,同时访问在命令突发模式下,内核访问的下一个地址将成为同一个地址的开始页面。它会导致重写该位置的内容或读取意外的数据。因此,您必须跟踪执行命令突发操作时,当前页面中的可访问地址范围。如果一个应用程序要求命令突发大小固定,建议使用2-、4-、8-、16-或32-突发,以保证命令的正常运行突发访问不会跨越页面边界。当cmd_burst_cnt和ofly_burst_len为0时,控制器执行32个命令(读或写)。cmd_burst_cnt输入的采样方式与cmd信号相同。时间的选择命令和地址组如图2.3所示。图2.3中的突发计数时间只显示了采样总线的时间。当cmd_burst_cnt采样值大于00001时,命令队列变为满,cmd_rdy信号不断言,内存地址由核心自动增加,直到当前命令突发周期完成。

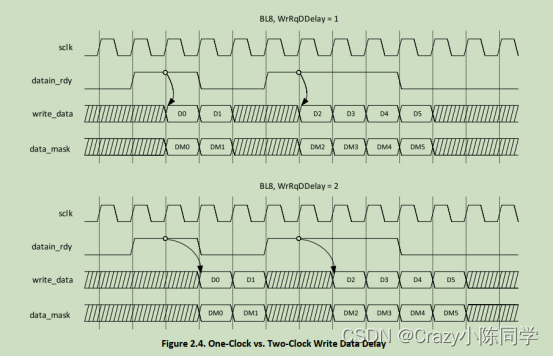

3.写数据

您可以通过断言cmd_valid以及write或WRITEA命令和地址来启动内存写操作。WRITE命令被接受后,当内存控制器核心准备接收用户逻辑写入内存的写入数据时,它会断言datain_rdy信号。由于从接受写命令到断言datain_rdy信号的时间不等,因此用户逻辑需要监视datain_rdy信号。一旦断言datain_rdy,在datain_rdy之后的一到两个时钟周期内,核心希望write_data总线上有有效的数据。断言datain_rdy信号后的周期。可以通过设置所需的值来编程写数据延迟Data_rdy在用户界面中写入数据延迟,提供灵活的后端应用支持。例如,设置取值为2可以确保当核心的本地用户界面为写时,核心在适当的时间接收写数据连接到用户逻辑内部的同步FIFO模块。图2.4显示了本地用户的两个示例接口数据写定时。两种情况都处于BL8模式。上图显示了一个时钟周期延迟的情况写数据时,下方显示两个时钟周期的延时情况。内存控制器考虑D0、DM0通过D5、DM5有效写入数据。

控制器对输入的地址进行解码,提取当前行和当前银行地址,并检查当前是否为内存设备中的行已经打开。如果当前bank中没有打开的行,则使用ACTIVE命令由控制器生成的内存先打开当前行。然后内存控制器发出WRITE指令命令到内存中。如果当前银行中已经有一个打开的行,且当前行地址为与打开行的不同,控制器会生成一个PRECHARGE命令来关闭打开的行bank。然后使用ACTIVE命令打开当前行。然后内存控制器发出WRITE指令命令到内存中。如果当前行已经打开,则只有一个WRITE命令(没有任何ACTIVE或PRECHARGE命令)被发送到内存。

需要注意的是:一次写,需要给两个用户数据

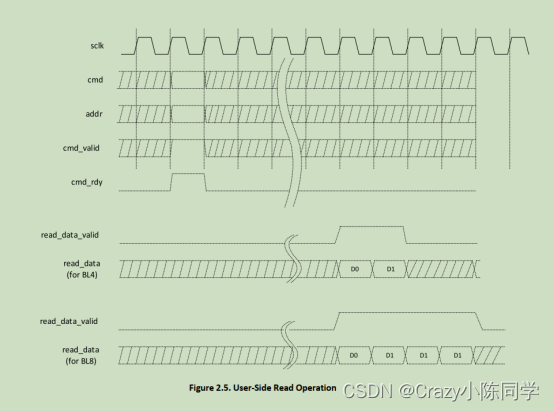

4.读数据

当READ命令被接受时,内存控制器核心访问内存以读取寻址数据,并将数据返回到本地用户界面。一旦读取数据在本地用户界面上可用,内存控制器核心就会断言read_data_valid信号,告诉用户逻辑有效的读取数据在read_data总线上。本地用户界面上的读取数据计时如图2.5所示读操作遵循写操作中提到的行状态检查方案。根据当前行状态,内存控制器生成ACTIVE

本文详细介绍了Lattice FPGA平台上的DDR3内存控制器的设计与实现,包括控制器的架构组成、时钟同步模块的作用及工作原理、用户接口与内存接口的交互流程等关键信息。

本文详细介绍了Lattice FPGA平台上的DDR3内存控制器的设计与实现,包括控制器的架构组成、时钟同步模块的作用及工作原理、用户接口与内存接口的交互流程等关键信息。

2521

2521

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?