如果想要在查询结果中展示名为‘htwj’的text字段,需要在SELECT语句中添加该字段,并在GROUP BY语句中同样添加该字段。具体的查询语句如下:

```

SELECT t1.id, t1.[requestId] AS t1_requestId, t1.[gf] AS '供方', t1.[htmc] AS '合同名称', t1.[htbh] AS '合同编号', t1.[sjbh] AS '编号', t1.[qdrq] AS '签订日期', t1.[qsrq] AS '起始日期', t1.[jzrq] AS '截止日期', t1.[zje] AS '总金额', t1.[zds] AS '总吨数', t1.[rksj] AS '入库时间', t1.[chpt] AS '撮合平台', t1.[qsfs] AS '签署方式', t1.[gfjc] AS '供方简称', t1.[cclx] AS '持仓类型', t1.[htwj] AS '合同文件', STUFF( ( SELECT ',' + CONVERT ( VARCHAR, CASE WHEN ISNUMERIC( REPLACE( t2.hsdj, ',', '' ) ) = 1 THEN CAST ( REPLACE( t2.hsdj, ',', '' ) AS FLOAT ) END ) FROM formtable_main_43_dt1 t2 WHERE t1.id = t2.mainid FOR XML PATH ( '' ) ), 1, 1, '' ) AS '采购单价' FROM formtable_main_43 t1 INNER JOIN formtable_main_43_dt1 t2 ON t1.id = t2.mainid GROUP BY t1.id, t1.[requestId] , t1.[gf] , t1.[htmc] , t1.[htbh] , t1.[sjbh] , t1.[qdrq], t1.[qsrq], t1.[jzrq] , t1.[zje] , t1.[zds] , t1.[rksj] , t1.[chpt] , t1.[qsfs], t1.[gfjc] , t1.[cclx], t1.[htwj];

```

请注意,这里假设‘htwj’字段确实存在且为text类型。如果该字段不存在或者类型不是text,查询语句需要做出相应的修改。

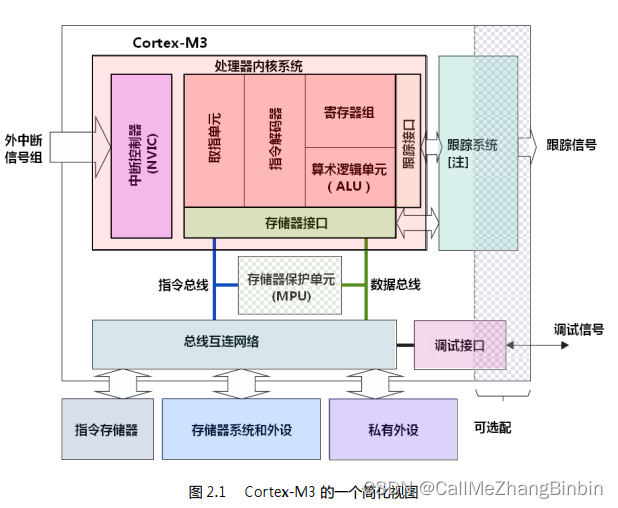

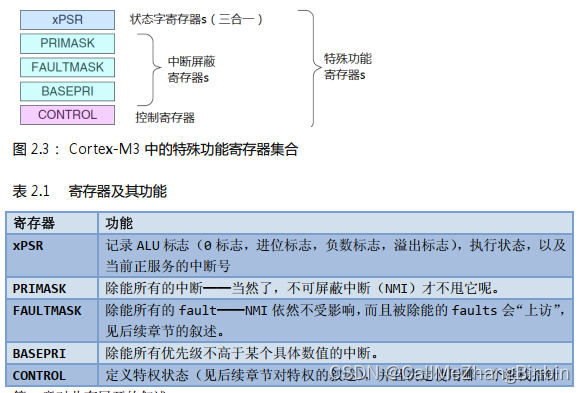

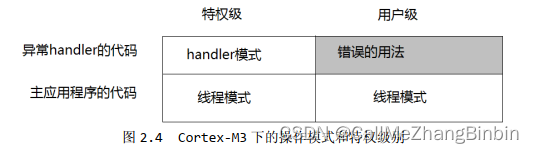

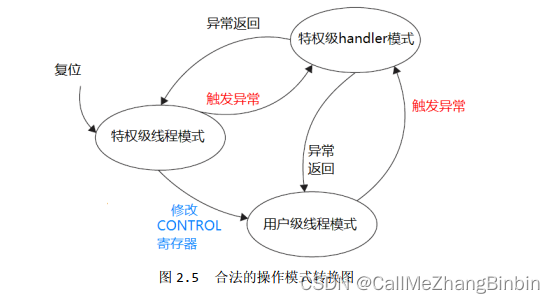

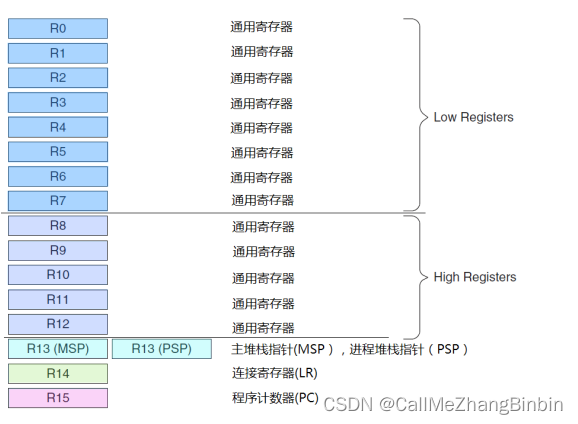

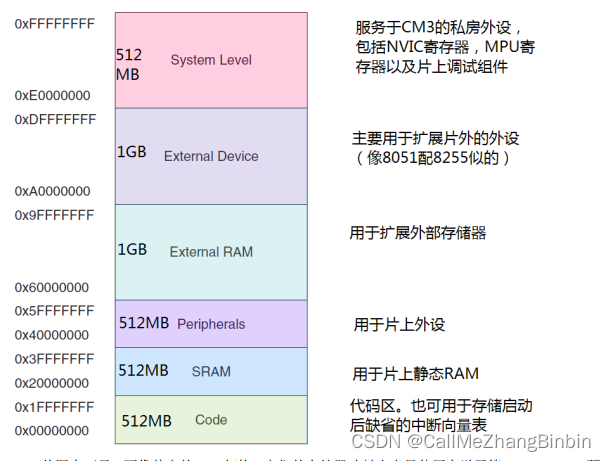

本文详细介绍了Cortex-M3处理器的寄存器组,包括通用寄存器、堆栈指针、连接寄存器等,着重讨论了嵌套向量中断控制器的特性,如中断管理、存储器映射和总线接口,以及其指令集、低功耗和调试支持。

本文详细介绍了Cortex-M3处理器的寄存器组,包括通用寄存器、堆栈指针、连接寄存器等,着重讨论了嵌套向量中断控制器的特性,如中断管理、存储器映射和总线接口,以及其指令集、低功耗和调试支持。

1314

1314

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?