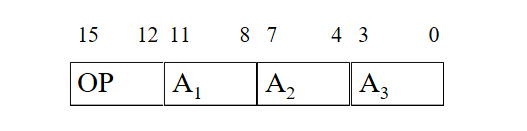

计算机是通过执行指令来处理各种数据的。为了指出数据的来源、操作结果的去向及所执行的操作,一条指令必须包含下列信息:

(1)操作码(OP),具体说明了操作的性质及功能

(2)第一操作数的地址

A

1

A_{1}

A1

(3)第二操作数的地址

A

2

A_{2}

A2

(4)操作结果存放地址

A

3

A_{3}

A3

(5)下一条将要执行指令的地址

A

4

A_{4}

A4

由上可得,一条指令包括两种信息:操作码,地址码

| 操作码 | 地址码 |

|---|

此外补充一下其他知识:

字长:计算机在单位时间内(同一时间)能一次处理一组二进制数的位数,决定了计算机的运算精度和一次处理能力。其中包含了CPU、寄存器、Data bus等能够一次传输数据的能力

字节:1Byte=8bit

地址码长度(操作数):地址码的位数,存储器可以按字长存储单元或字节存储单元编址,地址码的位数可以寻 2 N 2^{N} 2N个存储单元地址。所以地址码长度决定了指令的直接寻址能力。

指令长度:操作码长度+操作数地址码长度+操作数地址个数。指令长度和字长没有固定的联系

一、定长编码指令格式

这是最简单的一种编码方法。操作码字段的位数和位置固定,为能够表示整个指令系统中的全部指令,指令的操作码字段应当具有足够的位数。

设指令系统共有m条指令,指令中操作码字段的位数为N位,则满足

m<=

2

N

2^{N}

2N

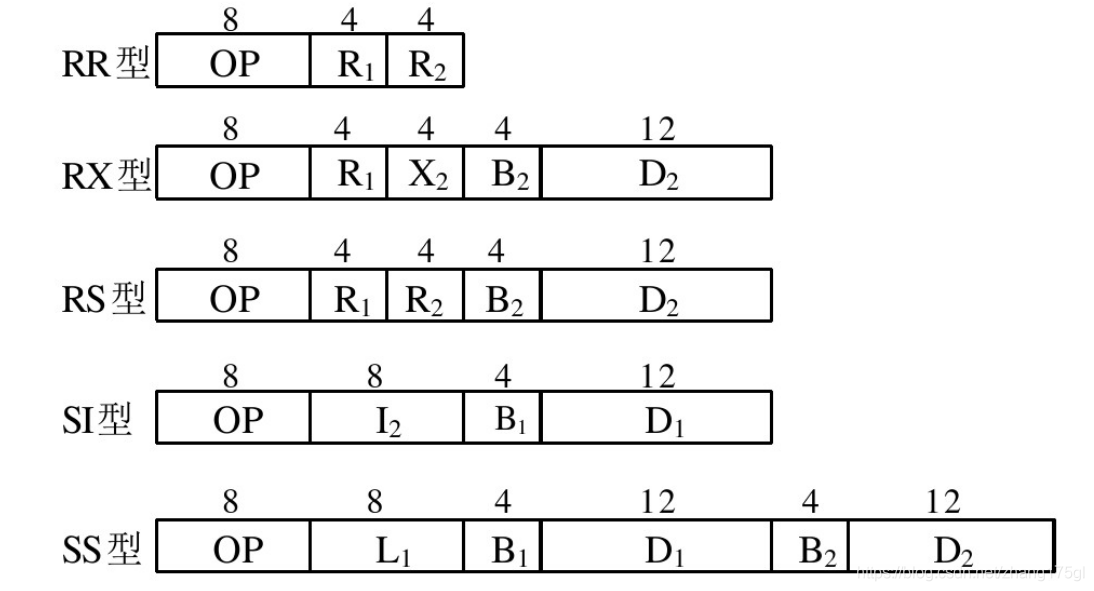

上图为IBM370机的指令格式

二、变长编码指令格式

变长编码的操作码字段位数是不固定的,且分散地放在指令字的不同位置上。

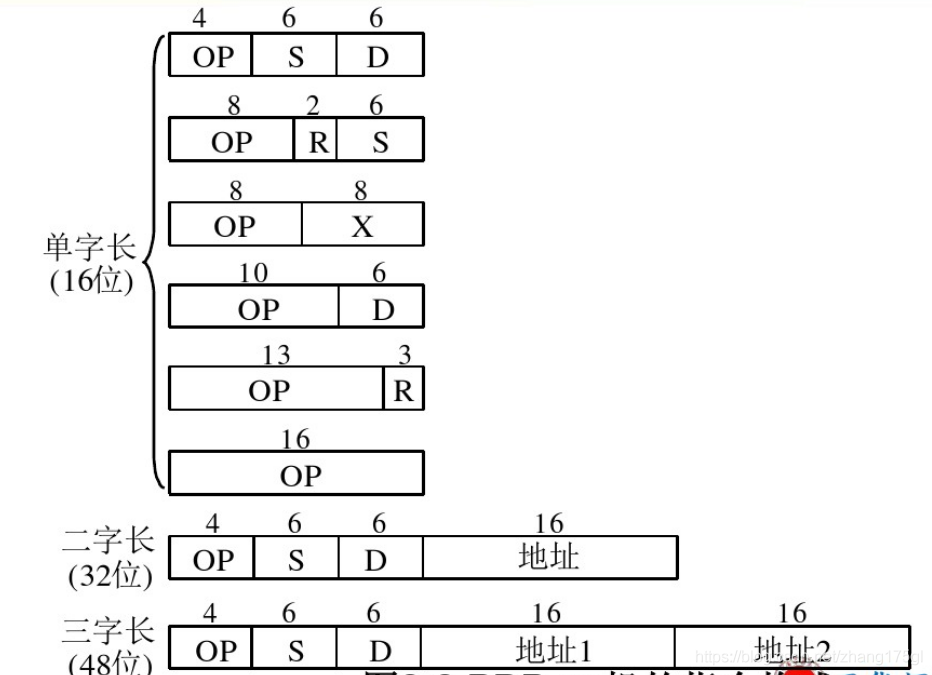

上图为PDP-11机的指令格式图(PPT里截的图)

下面放一道例题来熟悉一下这两种编码方式的应用

例:设某计算机字长16位,欲使设计的指令系统有零地址指令16条,一地址指令有15条,二地址指令有15条,三地址指令有15条,设每个地址码字段为4位,应如何设计?

解法一、定长操作码解法

共需要满足15+15+15+16=61条指令

由 2 6 2^{6} 26=64>61

所以操作码长度为6位

零地址指令长度6位

一地址指令长度10位

二地址指令长度14位

三地址指令长度18位

若要求指令字长为字节的整数倍,则

零地址指令长度8位

一地址指令长度16位

二地址指令长度16位

三地址指令长度24位

解法二、操作码扩展技术解法

2 4 2^{4} 24=16>15

指令格式为

各个字段均为4位,指令长度16位。

(1)把4位操作码的编码0000~1110作为15条三地址指令的操作码,1111作为扩展窗口把操作码扩展到

A

1

A_{1}

A1。

(2)8位操作码编码1111 0000~1111 1110作为15条二地址指令,1111 1111作为扩展窗口把操作码扩展到 A 2 A_{2} A2。

(3)12位操作码编码1111 1111 0000~1111 1111 1110作为15条一地址指令,1111 1111 1111作为扩展窗口把操作码扩展到 A 3 A_{3} A3。

(4)最后16位操作码编码1111 1111 1111 0000~1111 1111 1111 1111作为16条零地址指令。

PS:操作码扩展法即在4位二进制表示的16个码点中,用前15个(0000开始到1110)来表示最常用指令的操作码,剩余的一个码字(1111)作为扩展窗口把操作码扩展到下一个4位。下一个4位表示的16个码字按照同样的原则处理和扩展。

6973

6973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?