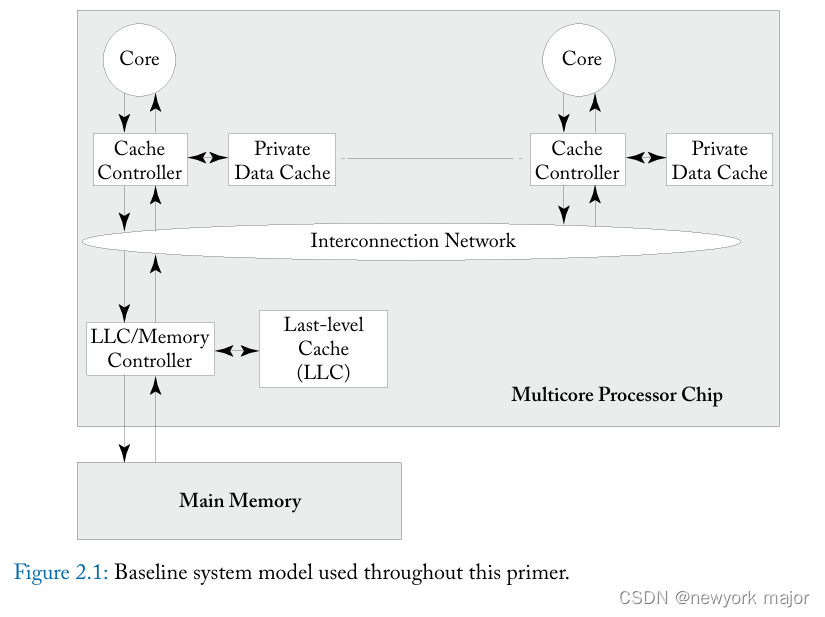

考虑上面这个比较简化的系统:

- 多核,每个核有多个线程;

- 多核间存在share memory;

- 每个核的多个线程,都可以同时对share momory进行load & store;

- 每个核有自己私有的data cache;

- 多核间有share的LLC;

1. incoherent是怎么产生的?

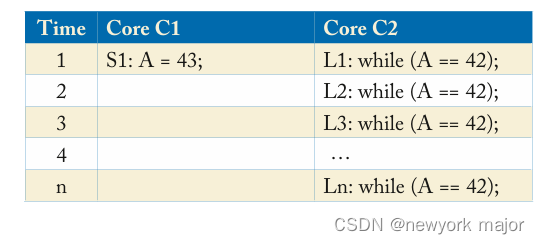

- 初始状态下, A地址的值为42,该值被load到了各个cores的cache中;

- time1时刻点,core1 修改了该地址的值,42->43;

- 而time1~n, 因为之前已经load到本地的cache, Core1的修改,core2不知道,所以core2仍然使用旧的值在运行;

- => 所以需要cache coherence protocal来保证不同核之间,访问相同地址的同步性;

2. 如何解决incoherent的问题?

- 核心解决思路:coherence protocol必须使得,write对于所有的processor是可见的;

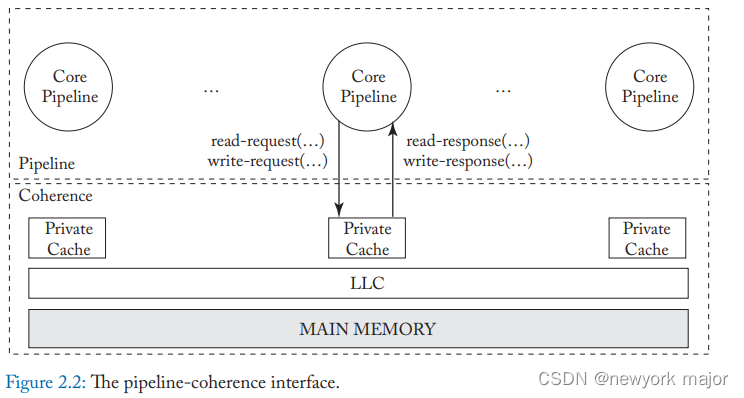

- 为了更好的理解,我们抽象出coherence-interface来说明:

core通过cohenrence接口与coherence协议进行交互,该交互方式提供两种接口:

- read-request: 传递一个地址信息,返回数据;

- write-request:传递一个地址信息和value, 返回响应;

目前主流的coherence protocal可以分为两类,主要的依据为:consistency model和coherence是否可以清晰的分离开;

- Consistency-agnostic coherence:

- write可以在还没有返回响应之前,就被其他的core观察到;

- 相当于,这种设计,每个core感觉不到cache的存在,每个人都觉得是在跟一个原子内存系统交互;

- Cache coherence 协议将缓存完全抽象出来并呈现出原子内存的错觉,就好像缓存被移除一样,只有内存包含在 coherence 框内;

- 此时orderings完全通过core中pipeline按照consistency model的规范来进行order;

- Consistency-directed coherence

- write的传播是异步的,在响应返回之后的一段时间内,才让别的core可以观察到这个写;

- 也就是说,其他core可以观察到老的value;

- 但是,此种coherence,必须保证,最终其他的core可以观察到最新值,并且观察到的顺序,必须与consistency规定的顺序一致;

- 这种coherence, 一般用在GP-GPU;

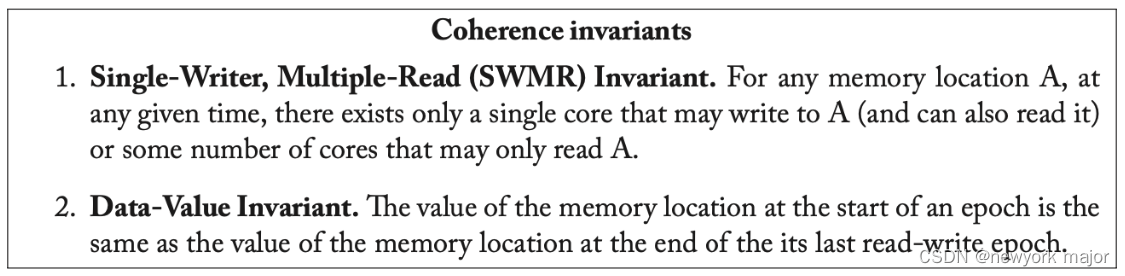

3. 什么是coherence invariants?

Coherence 协议必须满足哪些不变量 (invariants) 才能使缓存不可见并呈现原子内存系统的抽象?

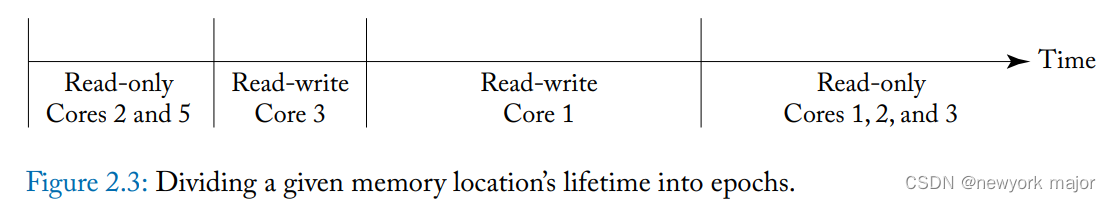

- SWMR invariant (single-writer–multiple-reader)

- 对于任意给定的地址,在任何一个时刻点, 要么有一个core可以写入它(也可以读取它),要么有一些core可以读取它;

- 也可以理解为,每个地址的lifetime, 被分成了多个时间片段,在某个时间片段上:

- 要么有某个核有read-write的access;

- 要么其他core有read-only access;

- data value invariant

- 考虑上面的例子,虽然上面的例子满足SWMR,但是可能出现如下场景;

- epoch1, core 2/5同时读取,但是每个core读到的数据不同;

- epoch3, core1读到的数据,不是epoch2刚刚写入的数据;

- 同理,epoch4, 读到的数据,不是epoch3刚刚写入的数据;

- 这些都是不符合coherence的;

- 因此,coherence的定义,还需要增加data value invariant, 该不变量表明,一个时期开始时的内存位置值与其最后一个读写时期结束时的内存位置值相同。

- 考虑上面的例子,虽然上面的例子满足SWMR,但是可能出现如下场景;

4. coherence协议是如何来维护上述的两个invariants的?

- 绝大多数的coherence协议,都是invalidate protocols,都是设计来保证上述的两个invariant的;

- 读操作流程如下:

- core x 要读取内存中某一个地址;

- 往其他core发送消息,获取该地址的数据,确保没有其他的core有这个地址的read-write state cache copy;

- 上述操作之后,相当于在figure 2.3中,结束了一个read-write epochs, 开始了一个read-only epochs;

- 写操作流程如下:

- core x要写某一个地址;

- 发送消息给其他核,如果当前core x没有该地址的read-only cache copy, 则获取该地址的最新值,同时确保其他的核,没有read-only/read-write的cache-copy;

- 上述操作之后,相当于在figure 2.3中,结束了一个read-only/read-write的epochs, 开始一个read-write epochs;

5. coherence的粒度

- 理论上来讲,coherence的粒度可以是任意值;

- 实际上是以cacheline为粒度;

6. Coherence 在哪些场景下适用?

Coherence 的定义,无论我们选择哪种定义,仅在某些情况下相关,架构师必须意识到它何时适用,何时不适用。我们现在讨论两个重要问题。

- Coherence 适用于持有共享地址空间中的块的所有存储结构。这些结构包括 L1 数据缓存、L2 缓存、共享的最后一级缓存 (LLC) 和主存。这些结构还包括 L1 指令缓存和转换后备缓冲区 (TLB)

- 程序员不能直接看到 coherence。相反,处理器流水线和 coherence 协议共同强制实施 consistency model,并且只有 consistency model 对程序员可见。

1355

1355

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?