伪随机码的介绍:

伪随机数有一部分遵守一定的规律;另一部分不遵守任何规律。比如“世上没有两片形状完全相同的树叶”,这正是点到了事物的特性,即随机性,但是每种树的叶子都有近似的形状,这正是事物的共性,即规律性。从这个角度讲,你大概就会接受这样的事实了:计算机只能产生伪随机数而不能产生绝对随机的随机数。

关于伪随机码的详细介绍课件附件的资料《伪随机序列的FPGA设计与应用》

详细文档见:http://wenku.baidu.com/view/d2f2a482ec3a87c24128c402.html

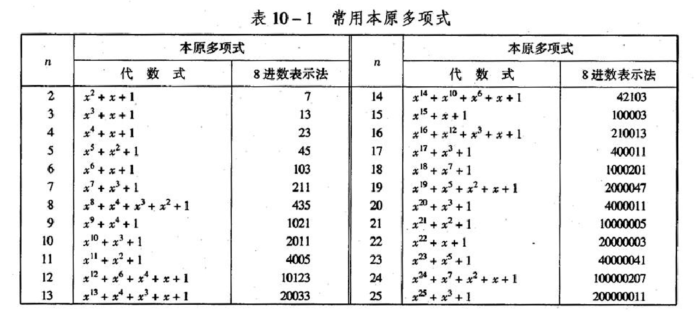

在设计伪随机码前要确定码长,从而确定本原多项式,常用的本原多项式见下表所示:

2 、开发环境说明

Xp操作系统下

编译环境:ISE13.2/SP3, ISE(XST)/Synplify 9.0 pro均综合实现通

本文档介绍了如何基于FPGA设计一个生成2^5-1(31位)周期的2Mbps伪随机码。首先解释了伪随机数的概念,然后详细阐述了设计过程,包括确定本原多项式和选择合适的开发环境。提供的Verilog代码展示了如何利用5级移位寄存器实现伪随机序列生成器,并提供了仿真输入代码和ISE simulator的仿真结果。

本文档介绍了如何基于FPGA设计一个生成2^5-1(31位)周期的2Mbps伪随机码。首先解释了伪随机数的概念,然后详细阐述了设计过程,包括确定本原多项式和选择合适的开发环境。提供的Verilog代码展示了如何利用5级移位寄存器实现伪随机序列生成器,并提供了仿真输入代码和ISE simulator的仿真结果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

229

229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?