1、调试组件简介

在 CM3 中有很多调试组件,使用它们可以执行各种调试功能:断点、数据观察点、闪存地址重载以及各种跟踪等。软件开发人员也许永远无需了解调试组 的细节,因为它们通常只是由调试器及其周边工具使用的。

本文对每种调试组件做一个基本的介绍,如果需要了解它们的更详细信息,如编程模型,则请参阅《Cortex-M3 Technical Reference Manual(Ref1)》。 所有的调试及跟踪组件, 以及 FPB,都可以经由 CM3 的私有外设总线来编程。在大多数情况下,只有调试主机才会编程这些组件。强烈反对应用程序尝试访问调试组件(除了对 ITM 中 stimulus端口寄存器的访问),这样做很容易与调试器发生冲突。

Cortex-M3 的跟踪系统

CM3 的跟踪系统是基于 CoreSight 架构的,跟踪数据被打成数据包,并且它们的长度可变。跟踪组件使用高级跟踪总线(ATB)来发送这些数据包给 TPIU, TPIU 则把它们格式化,转换成符合“跟踪总线接口协议”的数据包。格式化后的数据包发到片外, 可以使用跟踪端口分析仪(TPA)之类的设备捕获它们。整个数据流动的路线如图所示。

Cortex-M3 的消化系统模式图

2、跟踪组件:数据观察点与跟踪(DWT)

提供的调试功能包括:

1、它包含了 4 个比较器,可以配置成在发生比较匹配时,执行如下动作:

a) 硬件观察点(产生一个观察点调试事件,并且用它来调用调试模式,包括停机模式和 调试监视器模式

b) ETM 触发,可以触发 ETM 发出一个数据包,并汇入指令跟踪数据流中

c) 程序计数器(PC)采样器事件触发

d) 数据地址采样器触发

e) 第一个比较器还能用于比较时钟周期计数器(CYCCNT),用于取代对数据地址的比较

2、作为计数器, DWT 可以对下列项目进行计数:

a) 时钟周期(CYCCNT)

b) 被折叠(Folded) 的指令

c) 对加载/存储单元(LSU)的操作

d) 睡眠的时钟周期

e) 每指令周期数(CPI)

f) 中断的额外开销(overhead)

3、以固定的周期采样 PC 的值

4、中断事件跟踪

当用于硬件观察点或 ETM 触发时,比较器既可以比较数据地址,也可以比较程序计数器 PC。当用于其它功能时,比较器则只能比较数据地址。 每一个比较器都有 3 个寄存器:COMP 寄存器、MASK 寄存器、FUNCTION 控制寄存器。

其中, COMP 寄存器是一个 32 位寄存器,用于存储要比较的值。 MASK 寄存器可以用于掩蔽数据地址的一些位,被掩蔽的位不参与比较。

比较器的 FUNCTION 寄存器用于决定该比较器的功能。为了避免潜在的不可预料的行为,必须先编程 MASK 和 COMP,最后再编程 RUNCTION。如果要更改某个比较器的功能,必须先把 FUNCTION清零——除能该比较器,再重新配置一回,依然是最后配置 FUNCTION。

DWT 中有剩余的计数器,它们典型地用于程序代码的“性能速写”(profiling)。通过编程它们,就可以让它们在计数器溢出时发出事件(以跟踪数据包的形式)。最典型地,就是使用 CYCCNT寄存器来测量执行某个任务所花的周期数,这也可以用作时间基准相关的目的(操作系统中统计 CPU使用率可以用到它)。

3、跟踪组件: 仪器化跟踪宏单元( ITM)

ITM 有如下的功能:

软件可以直接把控制台消息写到 ITM stimulus 端口,从而把它们输出成跟踪数据。

DWT 可以产生跟踪数据包,并通过 ITM 把它们输出。

ITM 可以产生时间戳数据包并插入到跟踪数据流中,用于帮助调试器求出各事件的发生时 间。

因为 ITM 要使用跟踪端口来输出数据,所以芯片上必须有 TPIU 单元,否则无法输出——在使用 ITM 前要确认此事。如果不幸地没有 TPIU,也还可以使用 NVIC 调试寄存器,或者使用最后一招——求助于 UART 来输出控制台消息。

欲使用 ITM,必须把 DEMCR.TRCENA 位置位,否则 ITM 处于除能状态,无法使用。另外,在 ITM 寄存器中还有一个锁。在编程 ITM 之前,必须写入一个访问钥匙值 0xC5AC_CE55(CoreSight 的 ACCESS)到这个解锁寄存器。否则,所有对 ITM 寄存器的写操作都被忽略。 最后, ITM 自己也是另一个控制寄存器(可能是说控制寄存器的名字也是“ITM”吧),用于控制对各功能的独立使能。

控制寄存器中含了 ATID 位段,作为 ITM 在 ATB 中的 ID 值。这个 ID 必须是唯一的——每个跟踪源都必须有唯一的 ID 值,从而使调试主机能从接收到的跟踪数据包中分离出各跟踪源的数据。

3.1 基于 ITM 的软件跟踪

ITM 的一个主要用途,就是支持调试消息的输出(例如, printf 格式的输出) ITM 包含了 32个刺激(stimulus)端口,允许不同的软件把数据输出到不同的端口,从而让调试主机可以把它们的消息分离开。通过编程“跟踪使能寄存器”,每个端口都可以独立地使能/除能,还可以允许或禁止用户进程对它执行写操作。

与基于 UART 的文字输出不同,使用 ITM 输出不会对应用程序造成很大的延迟。在 ITM 内部有一个 FIFO,它使写入的输出消息得到缓冲。不过,为了安全起见,最好还是在写入前检查该 FIFO被填满的程度。

输出的消息被送往 TPIU,然后可以通过“跟踪端口接口”或者“串行线接口”来收集它们。在最终的代码中也无需移除产生调试消息的代码,而是可以把 TRCENA 位清零,这样 ITM 就被除能,调试消息也不会输出,你也可以在一个“live”系统中开启消息输出。另外,通过设置跟踪使能寄存器,可以限定允许使用的端口。

3.2 基于 ITM 和 DWT 的硬件跟踪

ITM 也能用于输出硬件跟踪数据,这些数据由 DWT 产生, ITM 则担任跟踪数据包的归并单元,如图 16.2 所示。欲使用 DWT 跟踪,需要在 ITM 控制寄存器中置位 DWTEN 位,剩下的 DWT 跟踪设置在 DWT 中完成。

3.3 ITM 时间戳

ITM 还附带了一个时间戳的功能:当一个新的跟踪数据包进入了 ITM 的 FIFO 时, ITM 就会把一个差分的时间戳数据包插入到跟踪数据流中。跟踪捕获设备在得到了这些时间戳后,就可以找出各跟踪数据之间的时间相关信息。另外,在时间戳计数器溢出时也会发生时间戳数据包。

4、跟踪组件:嵌入式跟踪宏单元

ETM 功能块用于提供指令跟踪(即指令执行的历史记录),它是个选配件,不一定出现在所有的CM3 产品上。当它使能后,并且在跟踪操作开始后,它会产生指令跟踪数据包。 ETM 中也有一个 FIFO缓冲区,为跟踪数据流的捕捉提供够用的时间。

为了减少产生的数据量, ETM 并不会一直忙不迭地输出处理器当前正在执行的地址。通常它只输出有关程序执行流的信息,并且只有在需要时才输出完整的地址(例如,当一个跳转发生时)。因为调试主机也有一份二进制映像的拷贝,它可以使用此拷贝来重建指令的执行序列。 ETM 也与其它的调试组件互相交互。例如,它与 DWT 的比较器就有关系: DWT 的比较器可用于产生 ETM 的触发信号,或者控制跟踪的启动与停止。

与传统 ARM 处理器的 ETM 不同的是, CM3 的 ETM 没有自己的地址比较器,而是由 DWT 的比较器代为完成。事实上, CM3 的 ETM 与传统 ARM 的 ETM 有很大的区别。

欲使用 ETM,必须执行下述的建立步骤(由调试器及其周边工具完成)

1、把 DEMCR.TRCENA 位置位(DEMCR 寄存器的定义参见表 15.2 或 D.37)。

2、解锁 ETM 以编程它的寄存器:往 ETMLOCK_ACCESS 寄存器中写 0xC5AC_CE55。

3、编程 ATBID 寄存器(ATID),赋 予 ETM 一个唯一的标识,以便把它的跟踪数据包与其它跟踪源的跟踪数据包分开。

4、ETM 的 NIDEN 输入信号必须为高电平。该信号的实现是取决于具体的器件的,还需要参考 该器件的数据手册。

5、编程 ETM 控制寄存器组以产生跟踪数据。

5、跟踪组件:跟踪端口接口单元( TPIU)

ITM, DWT 和 ETM 的跟踪数据都在 TPIU 处汇聚。 TPIU 用于把这些跟踪数据格式化并输出到片外,以供跟踪端口分析仪之类的设备接收使用。 CM3 的 TPIU 支持两种输出模式:

带时钟模式(Clocked mode), 使用最多4位的并行数据输出端口

串行线观察器(SWV)模式,使用单一位的SWV输出

在带时钟模式下,数据输出端口实际使用的位数是可编程的。这取决于两点。其一,是芯片的封装;其二,是在应用中,提供了多少个信号引脚给跟踪输出使用。在具体的芯片中,通过检查TPIU的寄存器,可以判断跟踪端口的最大尺寸。此外,跟踪数据输出的速度也是可编程的。

在SWV模式下,则使用SWV协议。它减少了所需的输出信号数,但是跟踪输出的最大的带宽也减少了。

欲使用TPIU,需要先把DECMR.TRCENA置位,还要编程“协议选择寄存器”和“跟踪端口尺寸“寄存器”,这个工作由跟踪捕捉软件完成。

6 闪存地址重载及断点单元( FPB)

FPB有两项功能:

硬件断点支持。产生一个断点事件,从而使处理器进入调试模式(停机或调试监视器异常) 把代码地址空间中对指令或字面值(literal data)的加载,重载到SRAM的地址空间中。 FPB有8个比较器,分别是: 6个指令比较器、2个字面值比较器

在FPB中有一个闪存地址重载控制寄存器,它包含了FPB的使能位。此外,每个比较器在它自己的控制寄存器中,都还有各自的使能位——前者是总开关。两种使能位必须都为1时才能启用比较器。

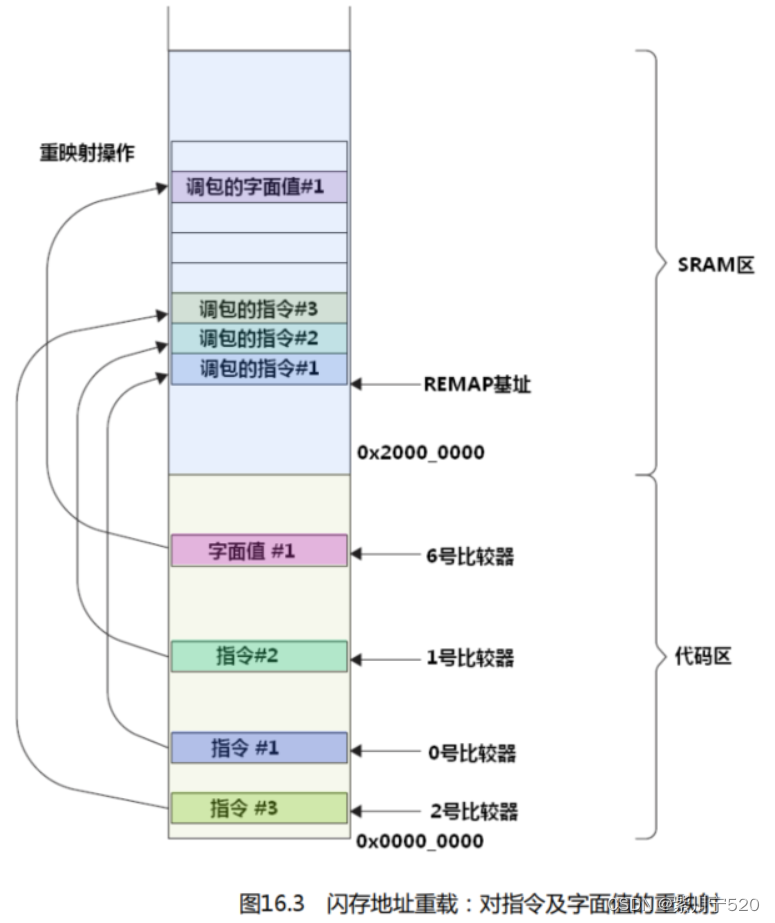

可以通过编程比较器,把指令空间的地址重载(重映射)到SRAM地址空间中。当使用此功能时,需要编程REMAP寄存器,以提供需要重映射内容的基址。 REMAP寄存器的最高3位[31:29]被硬线连接成0b001,因此限定了重映射后的地址范围在0x2000_0000-0x3FFF_FF80之间,这段地址正好落在SRAM地址空间中。

当指令地址或字面值地址与比较器中的数值发生匹配命中时,读访问就会根据REMAP的设置被重映射。

使用这个重映射功能,可以创建一些“如果...将会…”(what if)形式的测试——通过把原始指令或字面值取代成另一个来实现。并且即使是在ROM或flash中运行的代码,也能够参与此种测试。另一种用法在本质上与这种用法相同,但被取代的是跳转指令,因此行为很像“狸猫换太子”:对于某个位于flash中的子程序,在SRAM中提供一个冒充它的。通过闪存地址重载,使得在执行到调用该子程序的指令(BL)时,实际上执行的是被“调包”过的,位于SRAM中的BL,后者则跳转到“狸猫”中。这种机制使得基于ROM的设备也可以调试(修改过的子程序暂时放到SRAM中)。下图演示了重映射的效果。

除了地址重载,指令地址比较器的另一项功能,就是用于产生硬件断点(共6个),当地址匹配时使处理器进入调试模式。

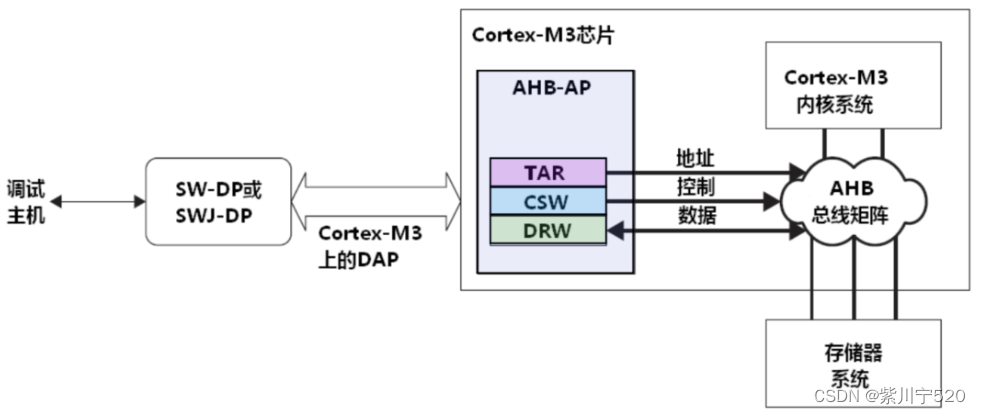

7、AHB 访问端口

AHB-AP位于CM3的存储器系统和调试接口模块(SWJ-DP/SW_DP)之间,充当一个总线桥的角色。对于大多数基本的在调试主机和CM3系统之间的数据传输,只需要使用AHB-AP中的3个寄存器,它们是: 控制及状态字(CSW)、传输地址寄存器(TAR)、数据读/写(DRW)。

AHB-AP的连接方法如图所示:

在Cortex-M3中AHB-AP的连接

CSW寄存器可以控制传送方向(读/写)、传送大小以及传送类型等。 TAR寄存器则指令传送地址,而DRW寄存器则容纳了被传送的数据(在访问该寄存器时就启动了传送)。 DRW中的数据与总线上实际显示的是一致的,所以对于半字和字节传送,必须由调试硬件把得到的数据适当移位,以对齐到LSB。例如,若欲在地址0x1002上执行一次半字传送,则需要把数据放到DRW的[31:16]上。 AHB-AP可以产生非对齐传送,但是它不会根据地址偏移来自动对目标数据做圆圈移位,必须由调试软件堵上这个窟窿:要么手工圆圈移位,要么把未对齐访问分解为若干个对齐的访问。

在AHB-AP中还有其它的寄存器,它们提供附加的功能。例如, AHB-AP中提供了4个bannked寄存器和地址自动增量的功能,用于加快在小范围连续地址中数据访问的速度。

在CSW寄存器中,还有一个名为MasterType的位。通常需要把它置1,以此告知参与AHB-AP数据传送的硬件:该数据传送是调试器发起的。但是,调试器也可以清零此位来伪装成处理器内核。这样, 在AHB上接收数据的硬件就会以为是内核发起的数据传送,从而正常地动作。这个功能可以用于测试目的,尤其是对于带有FIFO的外设,用于获知当它被调试器访问时,行为有什么不同。

8、ROM 表

CM3的调试系统还包含了ROM表,用于自动检测在某CM3芯片中包含了哪些调试组件。尽管作为v7-M的第一个践行者, CM3拥有一个预定义的存储器映射并且包含了标准的调试组件,但是新的Cortex-M器件可以包含不同的调试组件,并且芯片厂商在实现CM3时也可以对调试组件加以修改。为使调试工具能检测到调试系统中具体包含的组件,就提供了这张ROM表,它记录了NVIC和各个调试功能块的地址。

ROM表位于0xE00F_F000。通过分析ROM表中的内容,可以计算出系统和调试组件在存储器系统中的位置。在检测到了调试组件后,调试器可以接下来查看它们的ID寄存器,从而判定系统中哪些组件是可用的。在CM3的ROM表中,第一条目的内容应当是: NVIC的入口地址相对于ROM表入口地址的偏移量。ROM表首条目的缺省值是0xFFF0F003,其中位段[1:0]的作用比较特殊:它指示本条目对应的设备是存在的,并且在本条目的后面还有后续的条目(也就是说本条目不是最后一个条目)。这样,通过第一个条目,我们就知道系统中有NVIC,并且还有第2个条目,而且还能计算出NVIC的地址为0xE00F_F000+0xFFF0_F000=0xE000_E000。

缺省的ROM表如图16.2所示。但是因为芯片厂商可以添加、移除以及把某些可选的组件替换成其它的CoreSigth调试组件,这时该芯片的ROM表就会与缺省的有所不同,以反映出相应的变化。表是 Cortex-M3缺省的ROM表 。

数值的最低两个位用于指示该设备是否存在(bit[1])以及后面还有没有其它的表项(bit[0])。在正常情况下, NVIC, DWT和FPB总是必须存在的,因此最后两位永远是1。然而, TPIU和ETM则可以被裁掉,并且可能被CoreSight家庭中其它的调试组件所取代。

数值的高位部分用给出对应组件的入口地址相对于ROM表入口地址的偏移量。例如,NVIC入口地址= 0xE00F_F000 + 0xFFF0_F000 = 0xE000_E000(进位位被忽略)

在开发调试工具时,有必要从ROM表中一一查兑各调试组件,因为难免会有些另类的CM3芯片会自定义调试组件,并且修改ROM表,而通过计算ROM表得到的地址是可以拿去拍板的。

本文介绍了Cortex-M3微控制器中的调试组件,包括数据观察点与跟踪组件DWT、仪器化跟踪宏单元ITM、嵌入式跟踪宏单元ETM、跟踪端口接口单元TPIU以及闪存地址重载及断点单元FPB。这些组件支持断点设置、数据采样、指令跟踪、硬件和软件调试消息输出等功能,为软件开发和性能分析提供强大的工具。

本文介绍了Cortex-M3微控制器中的调试组件,包括数据观察点与跟踪组件DWT、仪器化跟踪宏单元ITM、嵌入式跟踪宏单元ETM、跟踪端口接口单元TPIU以及闪存地址重载及断点单元FPB。这些组件支持断点设置、数据采样、指令跟踪、硬件和软件调试消息输出等功能,为软件开发和性能分析提供强大的工具。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?