1 DRAM和SRAM

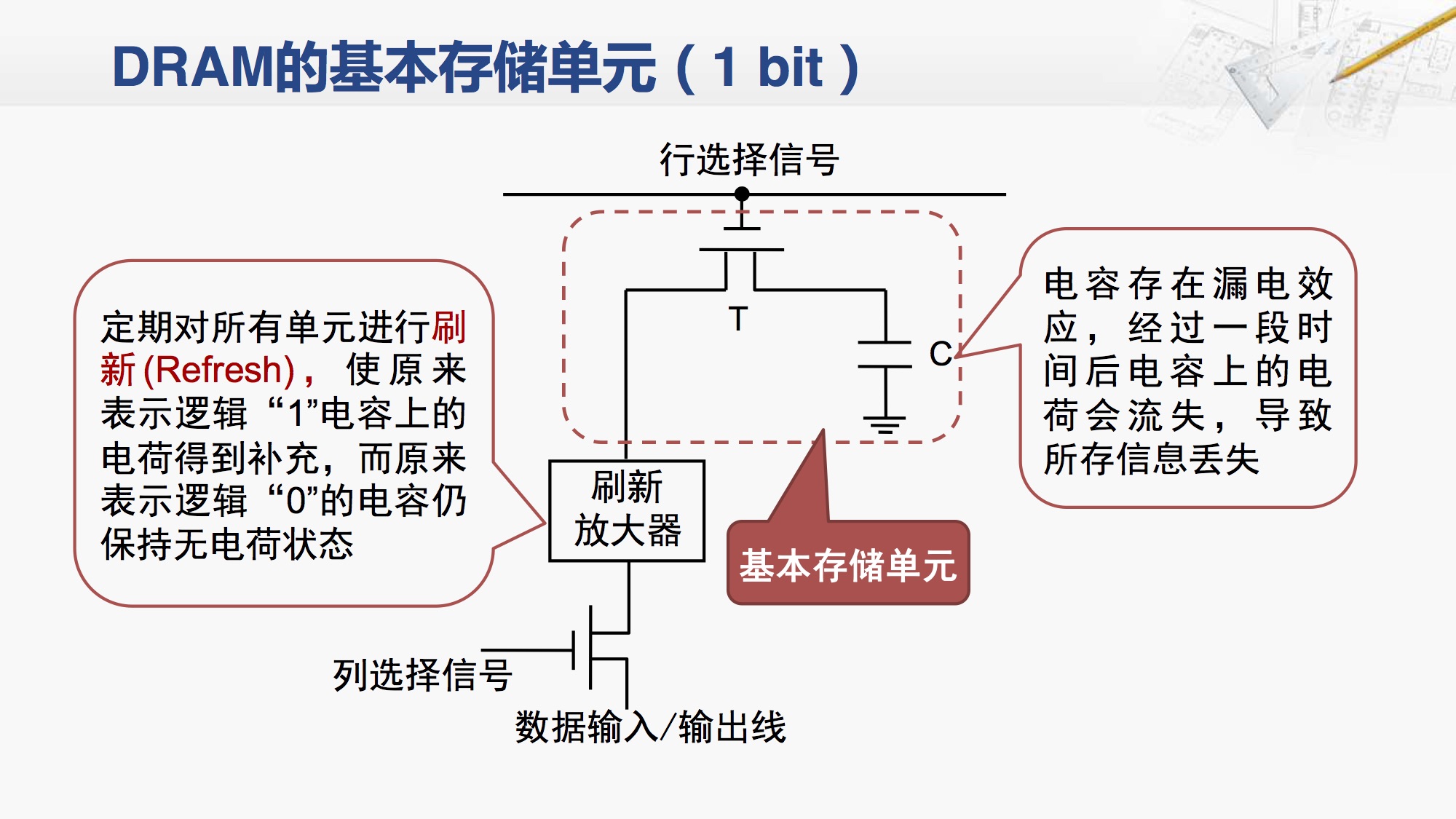

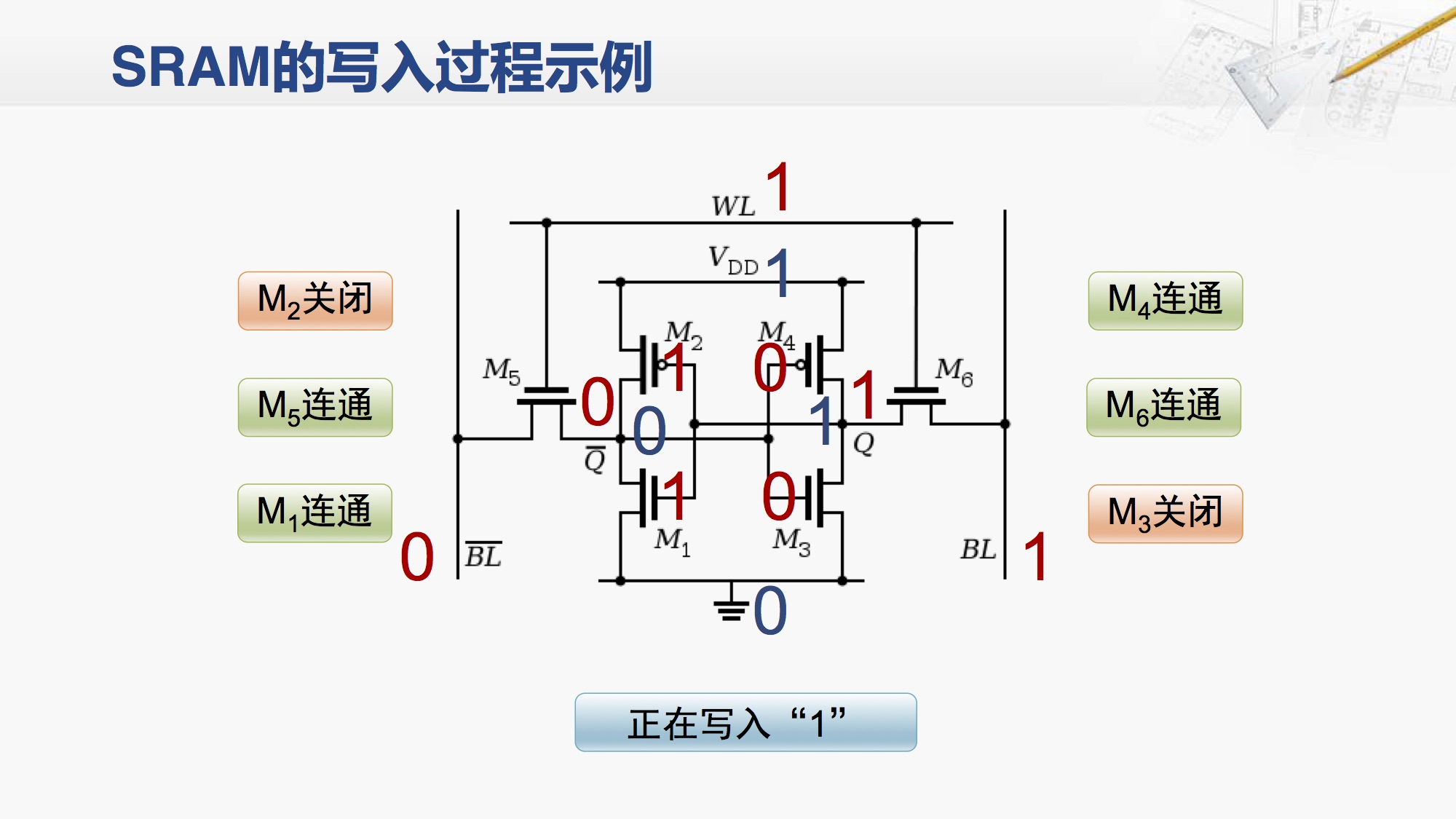

| 比较 | DRAM | SRAM |

|---|---|---|

| 存储单元 | 电容 | 双稳态触发器 |

| 集成度 | 高 | 低 |

| 功耗 | 低 | 高 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 有 | 无 |

2 主存

2.1 主存的工作原理

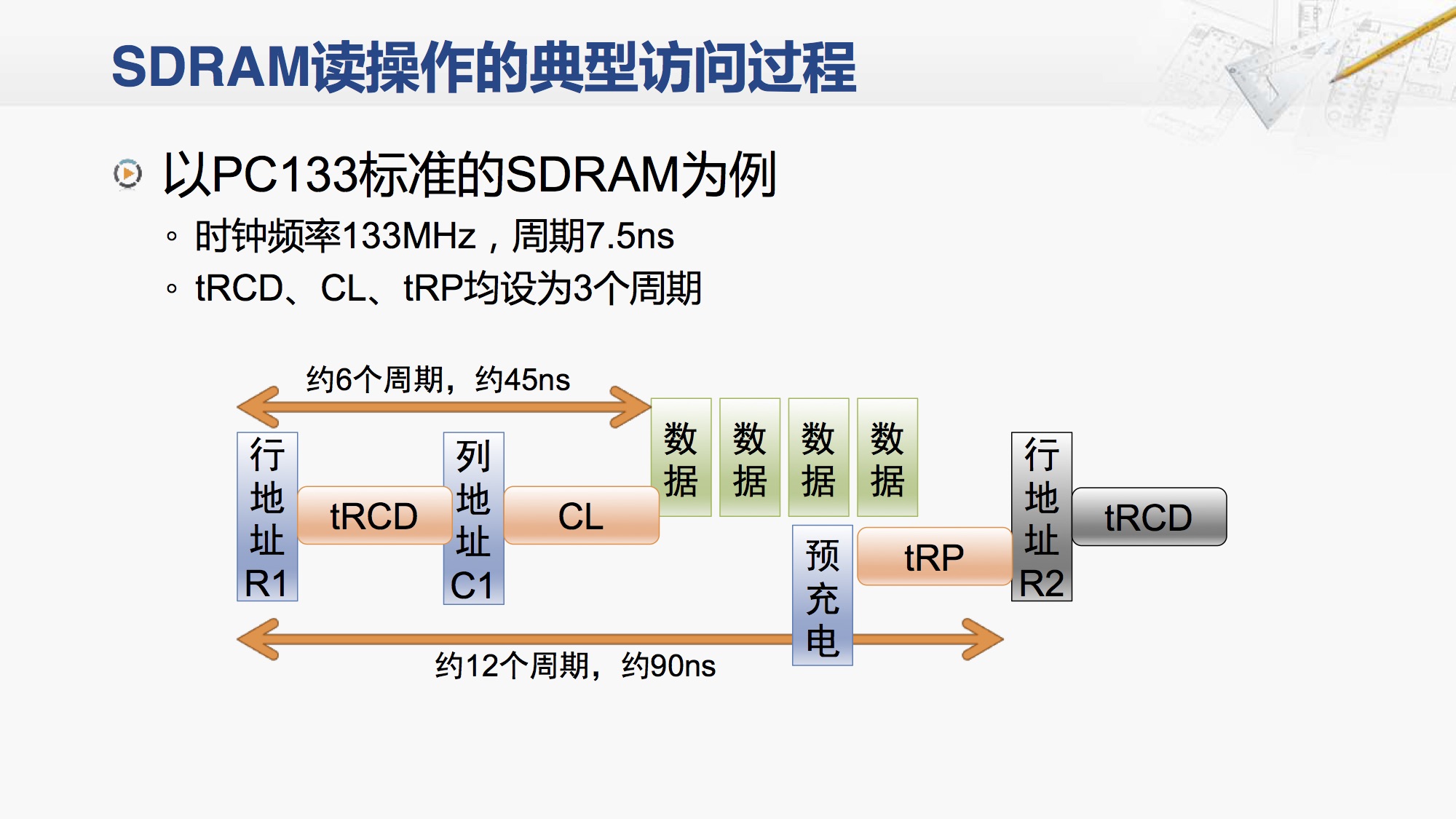

SDRAM的关键性能参数:

-

tRCD:Row to Column Delay,从行选到列选的延迟时间

- PC133标准:2-3个时钟周期,约15-23ns CL:CAS Latency,从行选到数据输出的延迟周期数

- PC133标准:2-3个时钟周期,约15-23ns tRP:RAS Precharge,行预充电(关闭行)的延迟时间

- PC133标准:2-3个时钟周期,约15-23ns

2.2 主存技术的发展

30年来,处理器与存储器性能差距日益加大

- 处理器性能增长超过10000倍

- 存储器(DRAM)性能增长不到10倍

SDRAM系列的频宽和带宽:

| 芯片标准 | 模组标准 | 核心频率 | I/O频率 | 等效频率 | 带宽GB/s |

|---|---|---|---|---|---|

| PC66(SDR) | PC-66 | 66MHz | 66MHz | 66MHz | 0.53 |

| PC100(SDR) | PC-100 | 100MHz | 100MHz | 100MHz | 0.80 |

| PC133(SDR) | PC-133 | 133MHz | 133MHz | 133MHz | 1.06 |

| DDR-200 | PC-2100 | 100MHz | 100MHz | 200MHz | 1.6 |

| DDR-266 | PC-2100 | 133MHz | 133MHz | 266MHz | 2.1 |

| DDR-333 | PC-2700 | 166MHz | 166MHz | 333MHz | 2.7 |

| DDR-400 | PC-3200 | 200MHz | 200MHz | 400MHz | 3.2 |

| DDR2-533 | PC-4200 | 133MHz | 266MHz | 533MHz | 4.2 |

| DDR2-667 | PC-5300 | 166MHz | 333MHz | 667MHz | 5.3 |

| DDR2-800 | PC-6400 | 200MHz | 400MHz | 800MHz | 6.4 |

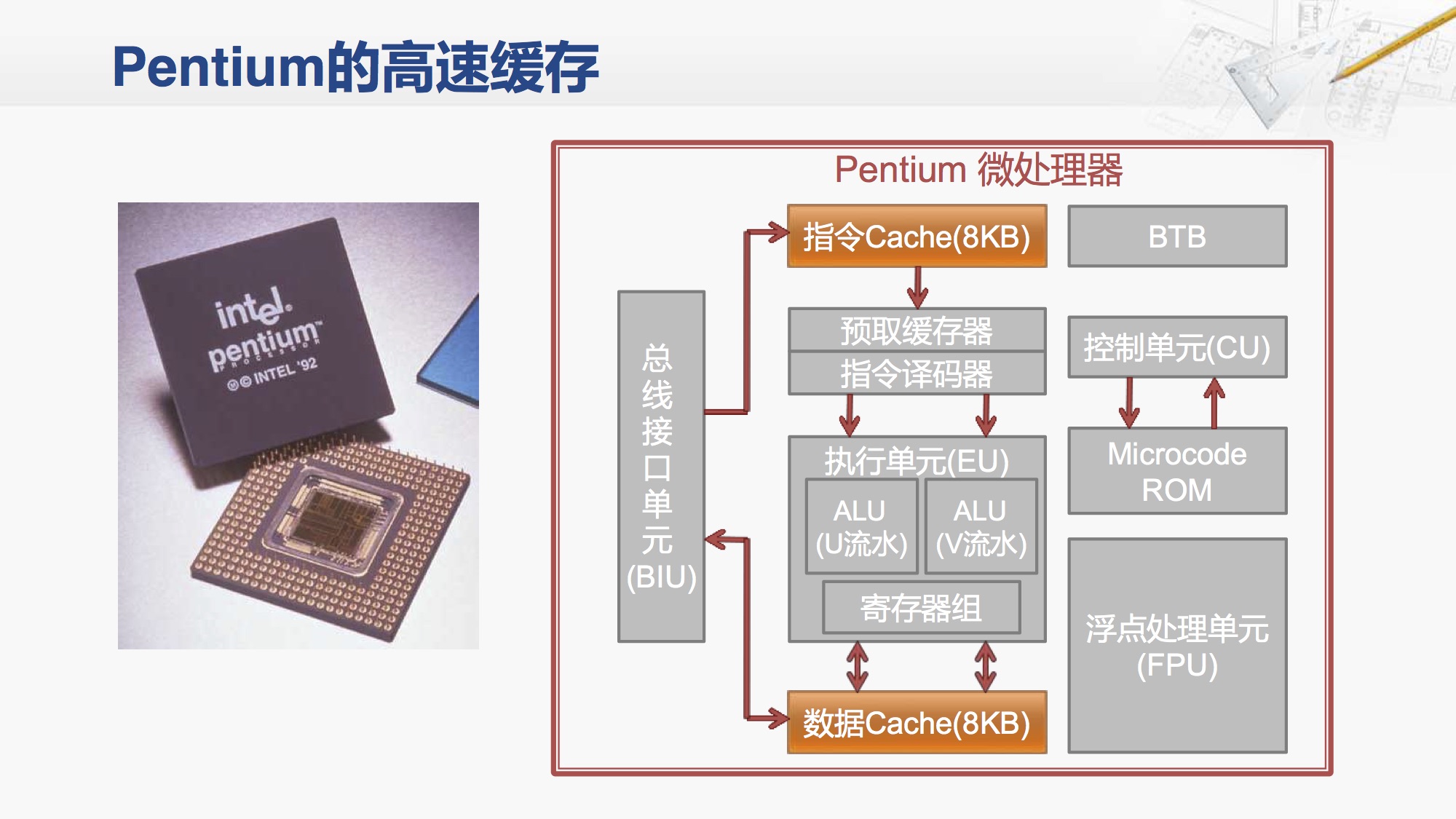

3 高速缓存

3.1 工作原理

程序的局部性

- 时间局部性:最近被访问的存储器单元(指令或数据)很快还会被访问

- 空间局部性:正在被访问的存储器单元附近的单元很快会被访问

典型实例:

for (i = 0; i < 1000; i++)

for (j = 0; j < 200; j++)

sum += a[i][j];- sum:时间局部性

- a:空间局部性

cache如何利用局部性原理?

- 从主存中取回待访问数据时,会同时取回与位置相邻的主存单元的数据

- 以数据块(Block)为单位和主存进行数据交换

- 保存近期频繁被访问的主存单元的数据

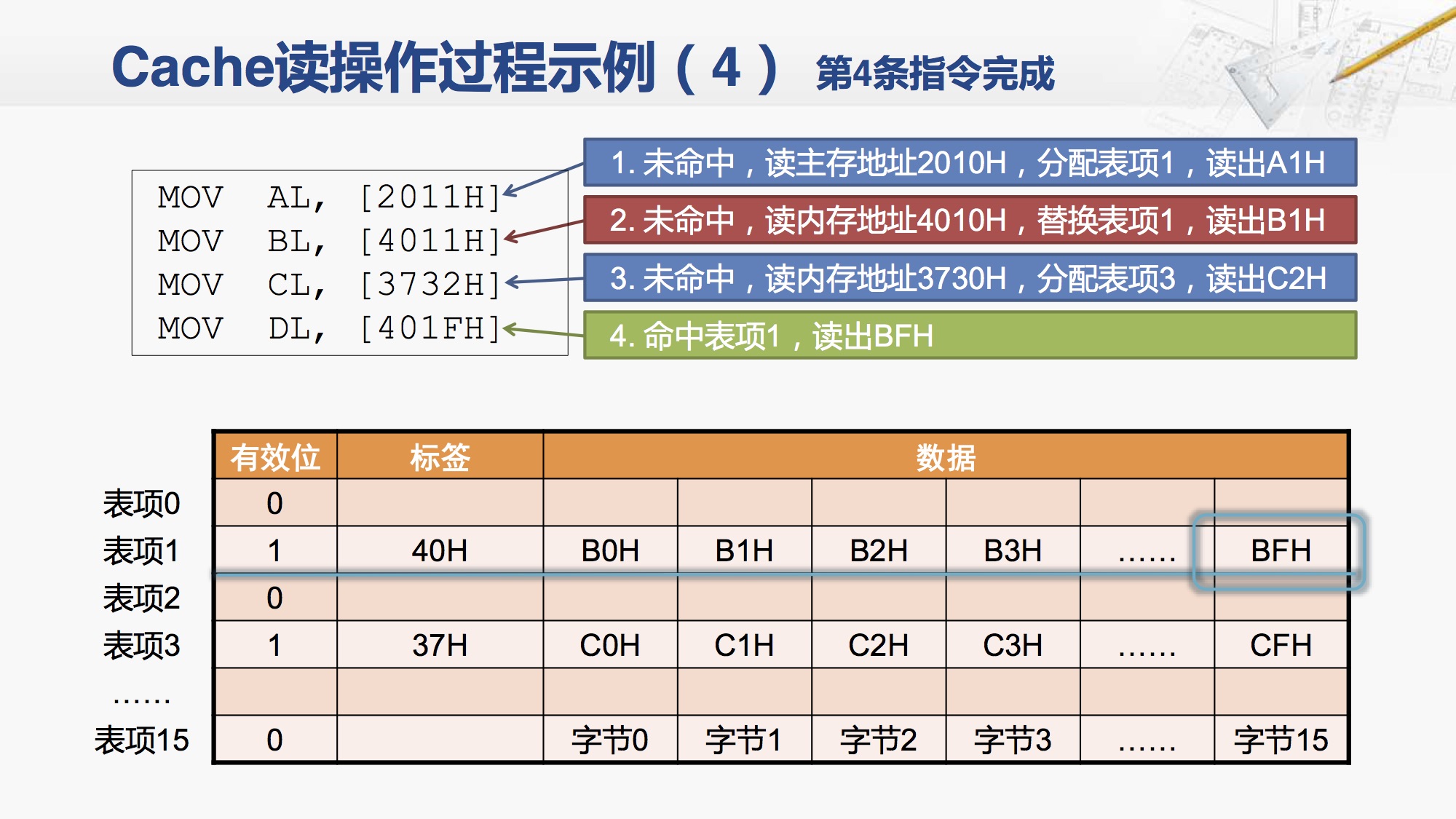

3.2 组织结构

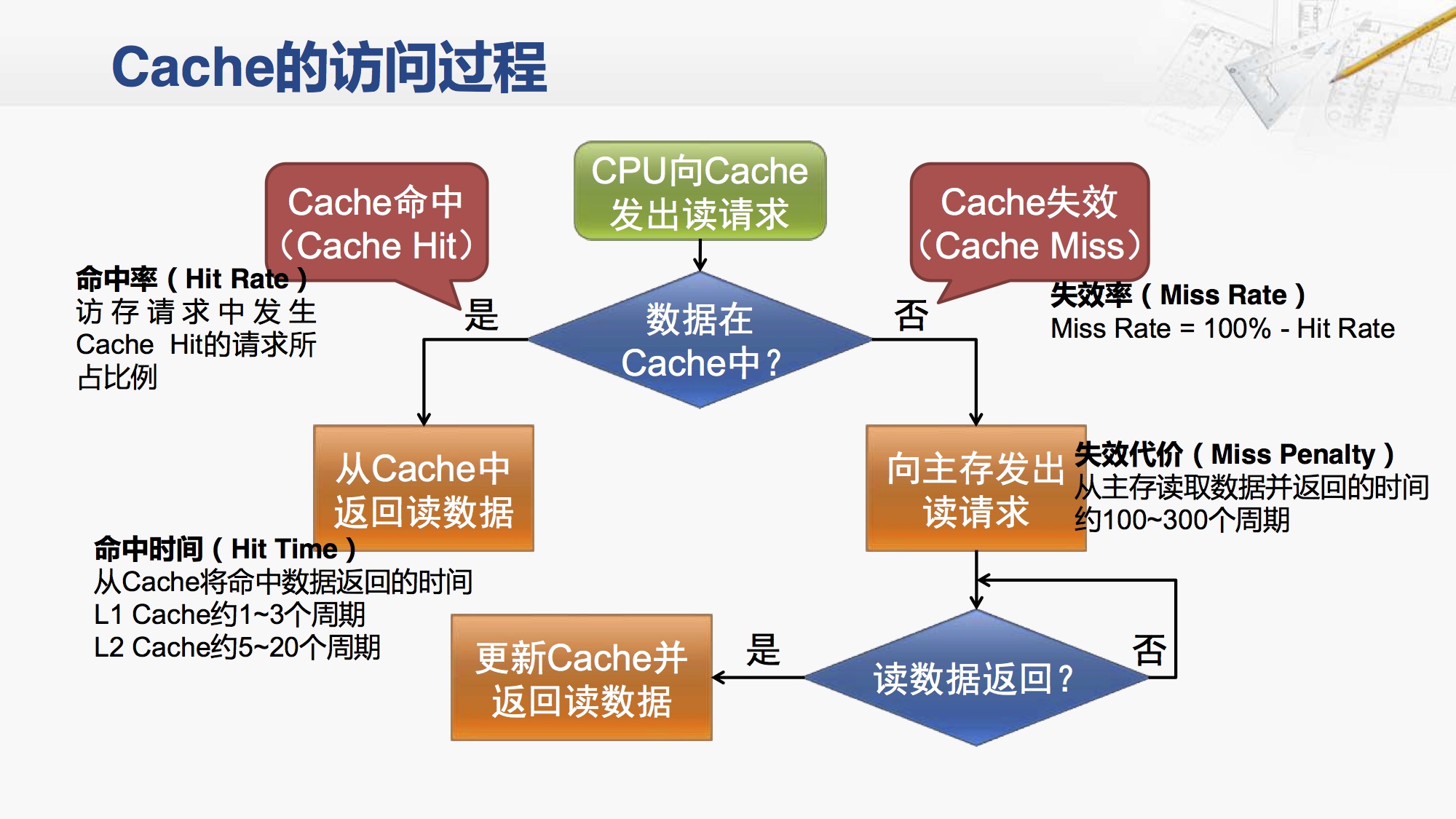

平均访存时间 = Hit Time + Miss Penalty * Miss Rate

cache失效原因

- 义务失效:第一次访问某一数据块(无法避免)

- 容量失效:cache无法保存程序访问所需的所有数据块(增加容量)

- 冲突失效:多个存储器位置映射到同一cache位置(映射策略)

映射策略:直接映射,二路组相联,四路组相联

cache替换算法

- 随机:硬件随机选择一个cache块替换

- 轮转:按照预先设定的顺序依次选择cache块替换

- 最近最少使用(LRU):硬件记录访问历史信息,选择距离现在最长时间未被访问的cache块替换

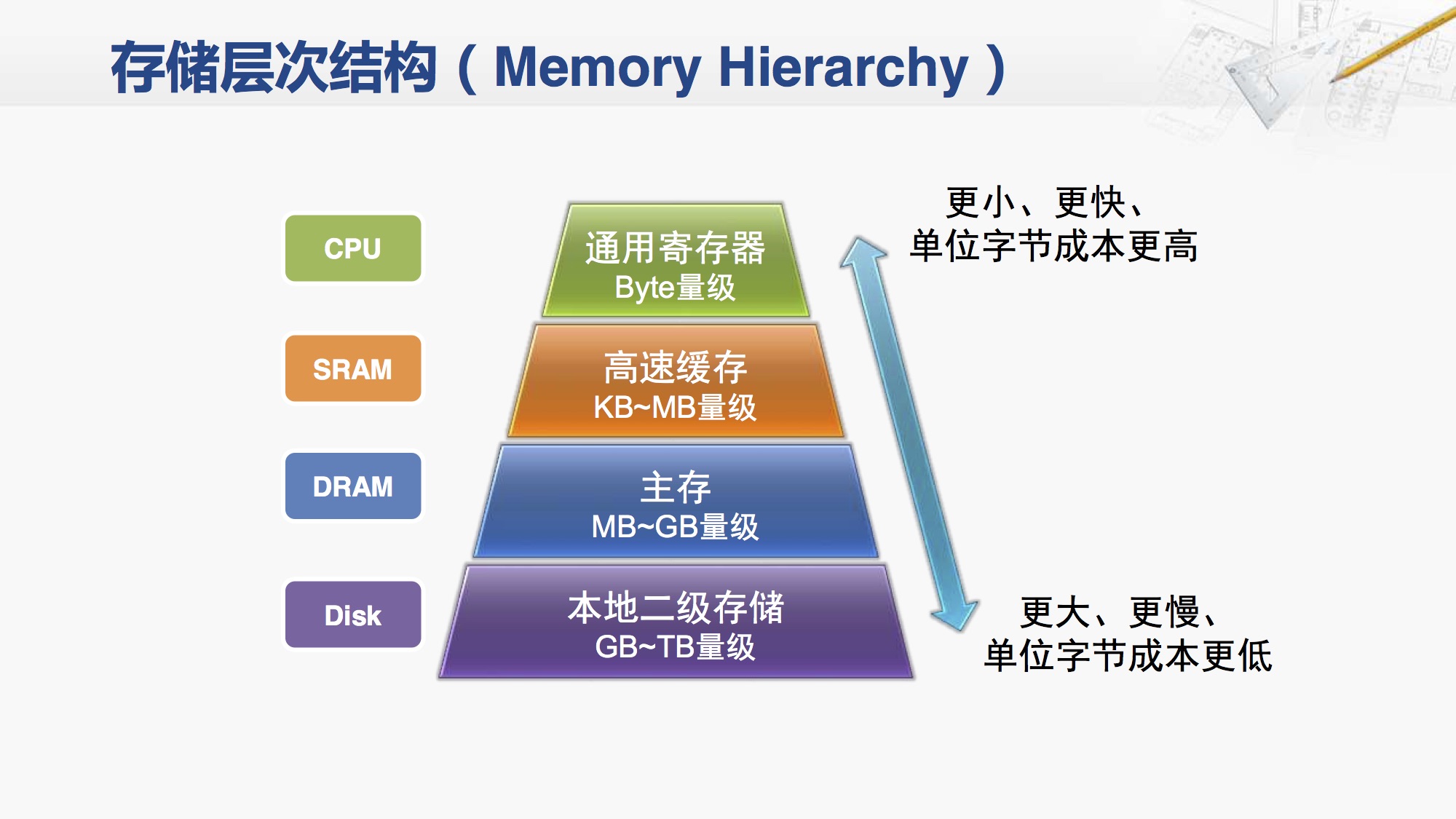

本文深入探讨了计算机存储层次结构,包括DRAM和SRAM的区别,主存的工作原理及其技术发展,重点讲解了高速缓存的局部性原理和组织结构,如hit time、miss penalty及替换算法。并介绍了存储容量的计算方法,涉及不同存储设备的容量单位和数据传输率。

本文深入探讨了计算机存储层次结构,包括DRAM和SRAM的区别,主存的工作原理及其技术发展,重点讲解了高速缓存的局部性原理和组织结构,如hit time、miss penalty及替换算法。并介绍了存储容量的计算方法,涉及不同存储设备的容量单位和数据传输率。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?