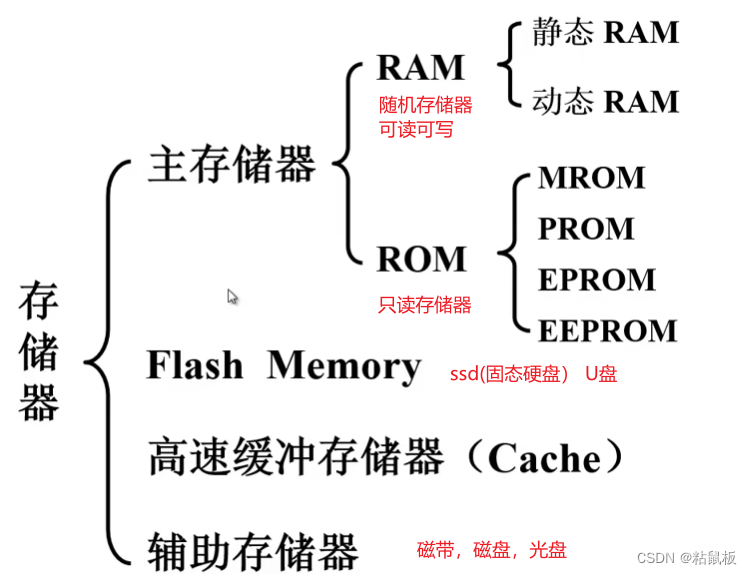

存储器

存储器分类

一、按存储介质分类

1、半导体存储器 TTL、MOS

2、磁表面存储器 磁头、载磁体

3、磁芯存储器 硬磁材料、环状元件

4、光盘存储器 激光、磁光材料

二、按存取方式与物理地址无关(随机访问)

1、存取时间与物理地址无关

- 随机存储器 在程序执行过程中可读可写

- 只读存储器 在程序执行过程中只读

2、存取地址和物理地址有关

- 顺序存取存储器 磁带

- 直接存取存储器 磁盘

三、按在计算机中的作用分类

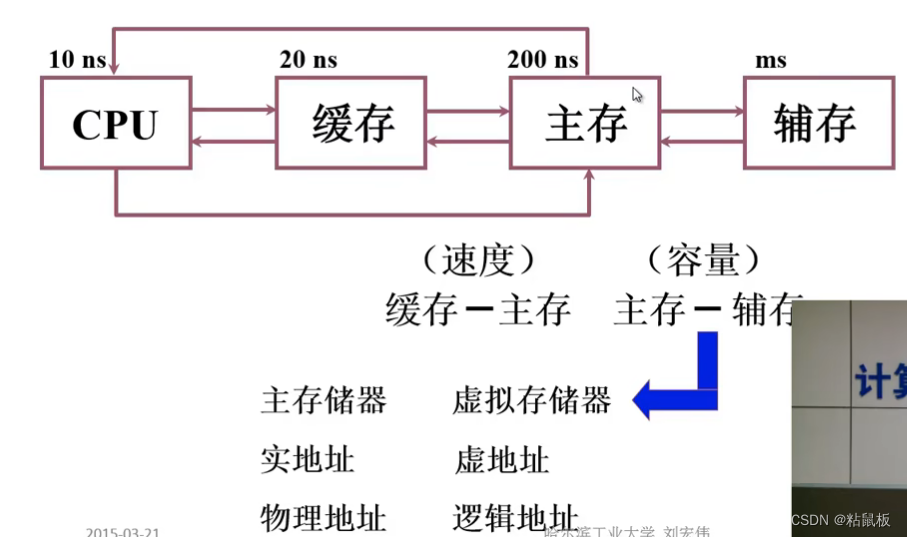

存储器的层次结构

一、存储器三个主要特性的关系

二、缓存-主存层次和主存-辅存层次

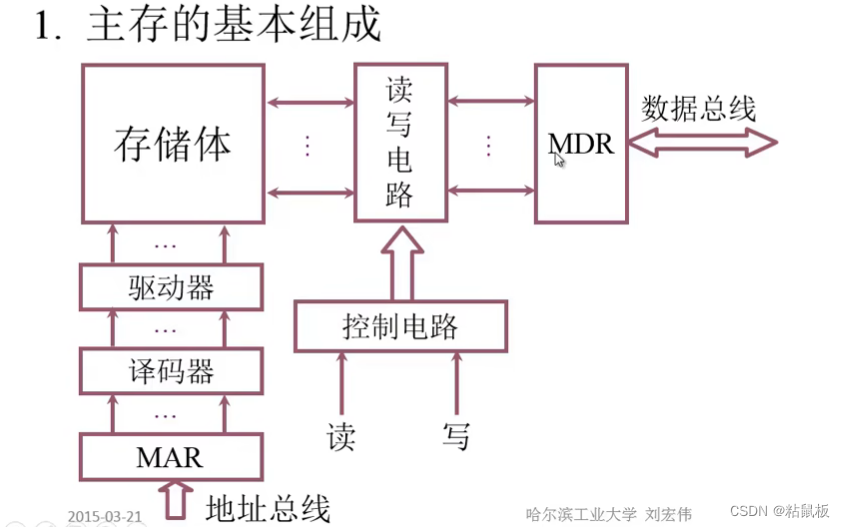

主存储器

概述

一个字长32位的机器(人为设定),已知一个字节是8位,那么这个机器的一个字是4个字节。一行是一个字,有4个格子,每个格子都有地址,但是用哪个格子的地址(即字节地址)作为字地址呢?这出现大端小端的命名

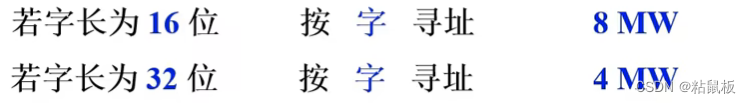

字长为16位:8(bit)位为一个(Byte)字节,两个(Byte)字节为一个(Word)字

字长为32位:8(bit)位为一个(Byte)字节,四个(Byte)字节为一个(Word)字

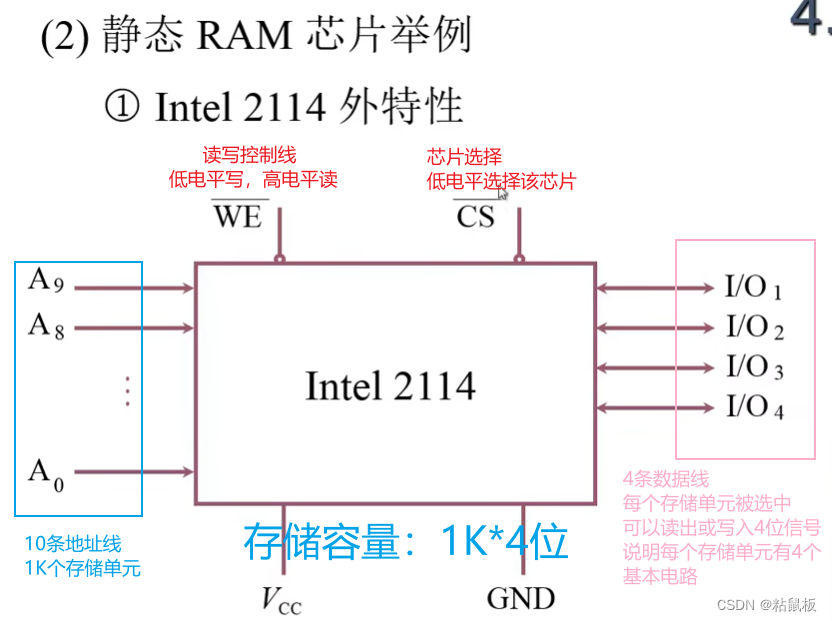

半导体芯片

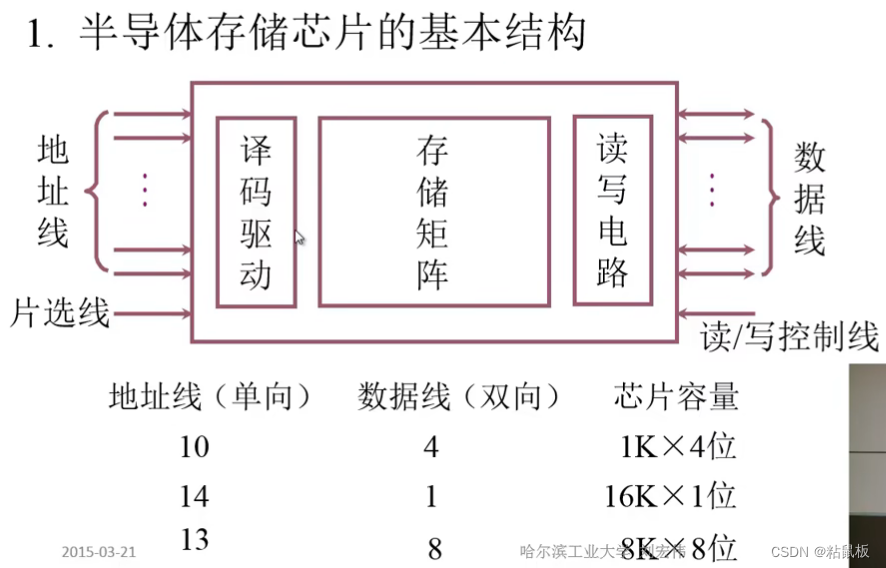

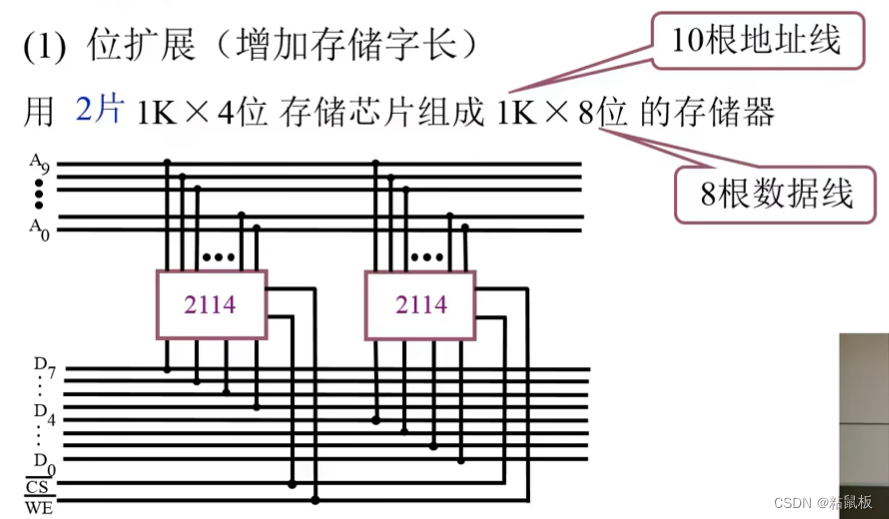

这里的地址线应该是体现按字寻址,数据线表示字长,故10根地址线表示2E10个字,4根数据线表示每个字长为4位,故容量为2E10*4

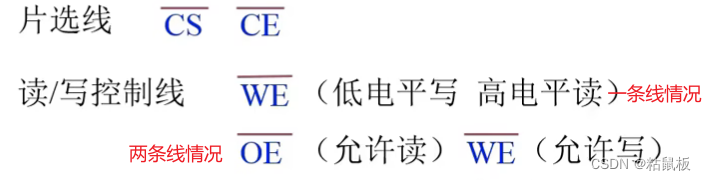

chip select(芯片选择:选哪个芯片)低电平该芯片才会被选中/chip enable(芯片使能:该设备是否能正常工作)

当地址为65535时,片选信号选48~64K的这一组芯片,其他三组芯片的CS,CE都是高电平,最后一组芯片是低电平。8个芯片同时进行访问,在8个芯片地址的统一位置分别读出一(bit)位构成一个字节,满足CPU对8位的要求

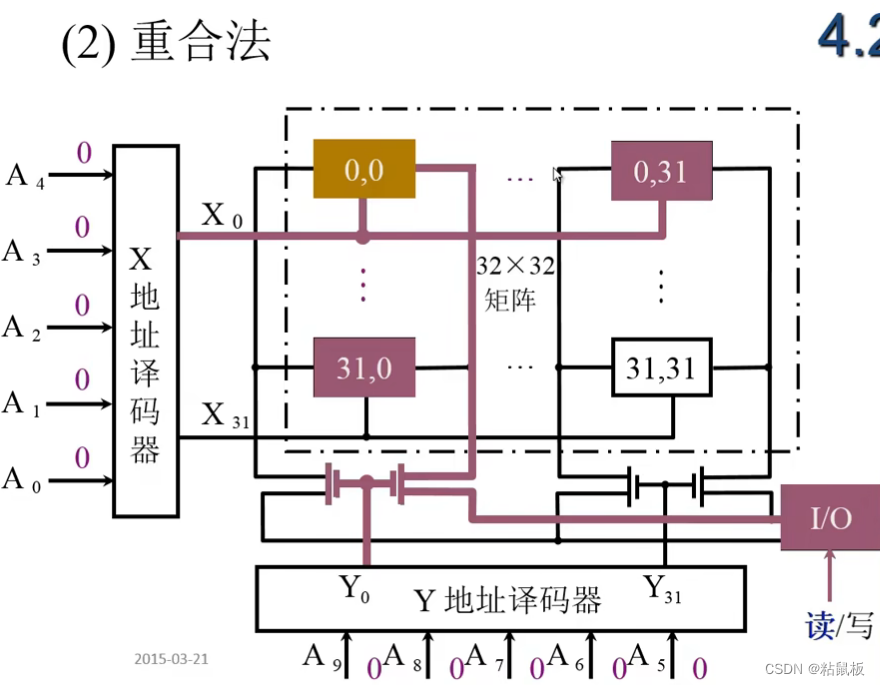

假设有20条地址线,每一条地址线在地址译码器之前有4根分线,输出有16根分线,经过地址译码器之后会译出1M条线(每给出一个地址,1M条线中只有一条是有效的,其他都是无效的)—1M条线做在芯片中会非常密集,导致芯片集成度不是很高,只适合小容量芯片

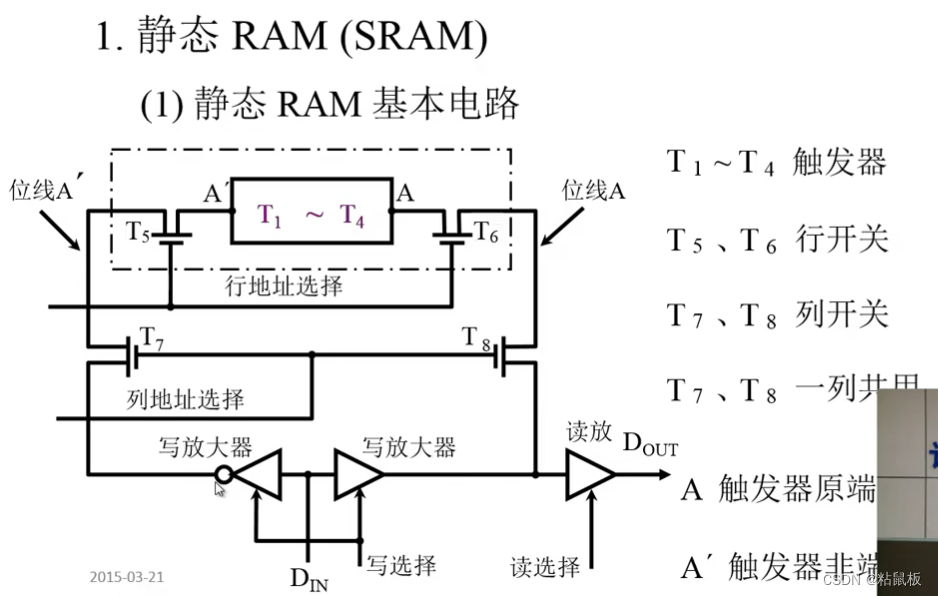

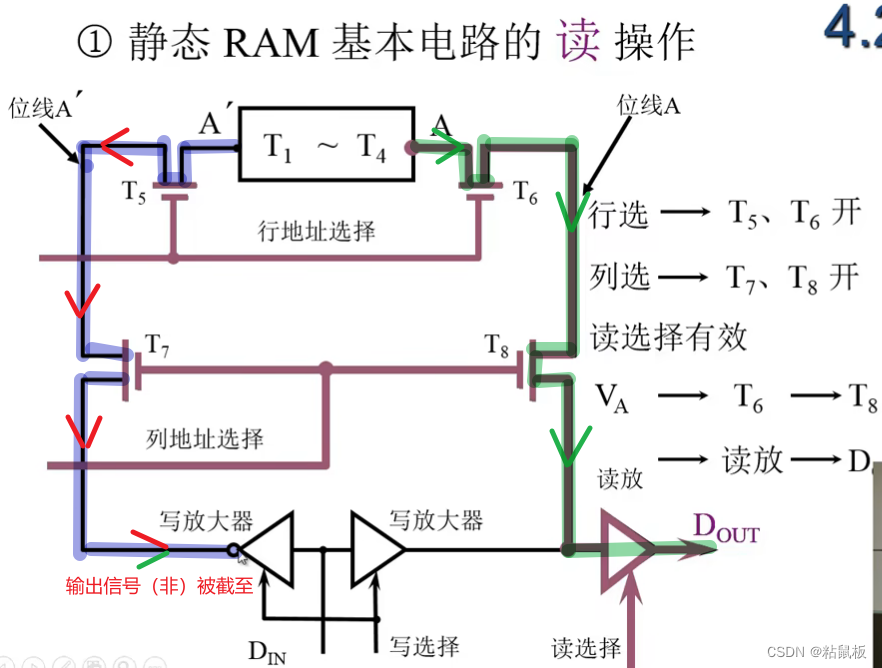

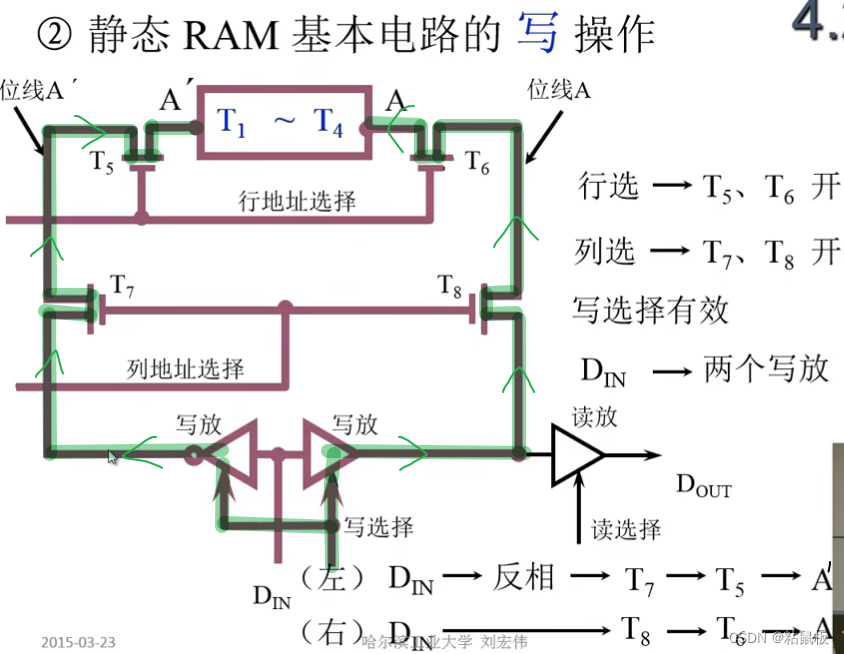

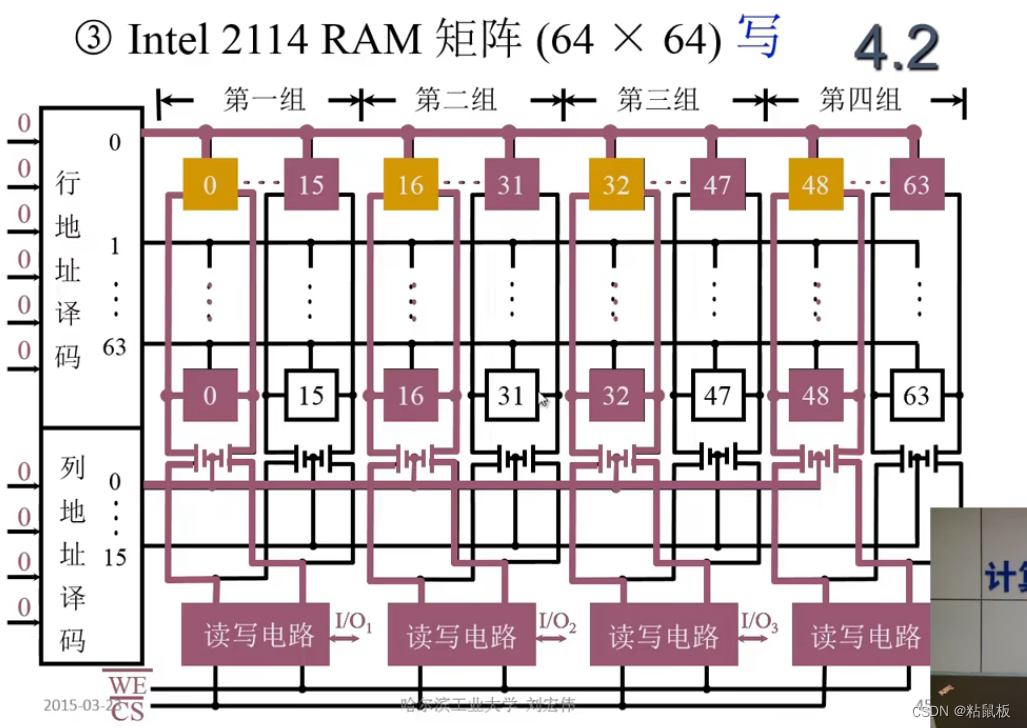

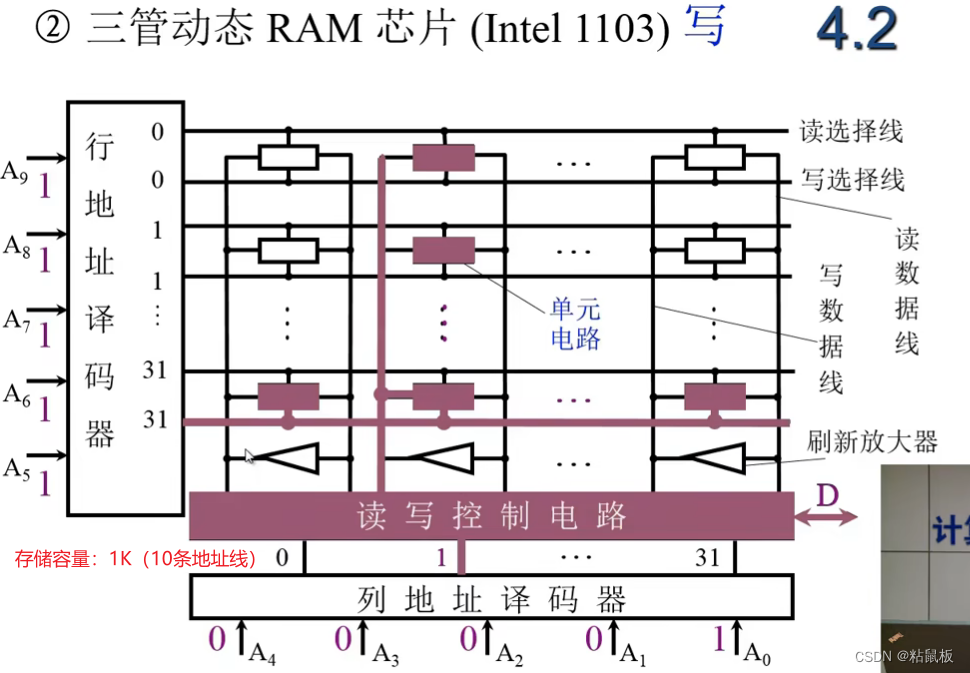

读选通是矩阵向外输出,写选通是从外向内输入

假设还是输出1M条线,重合法则可以把20位地址分为两部分(x方向和y方向)x地址译码器译出1K条线,y地址译码器译出1K条线,总计译出2K条线,相较于线选法条数减少很多,可以增加芯片集成度

随机存取存储器(RAM)

静态RAM

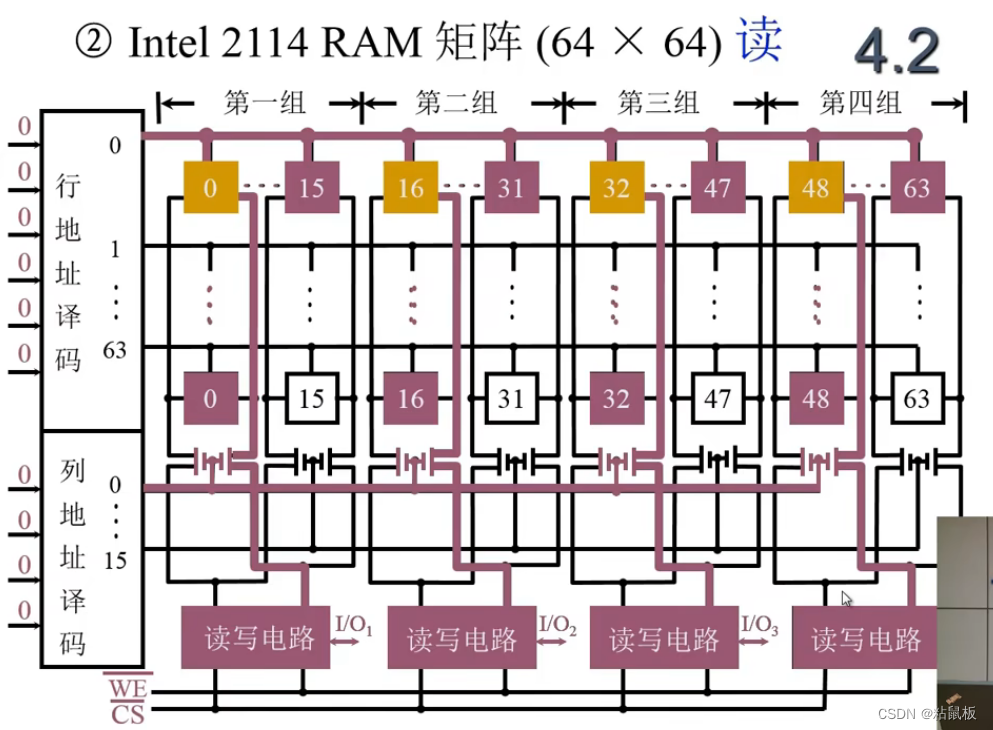

64列分成4组,每组64行16列为一个整体,每组连接一个i/o端口

每一个列选信号控制了每一组当中的一列(列选信号0控制了第一组当中的第0列,第二组当中的第0列…)

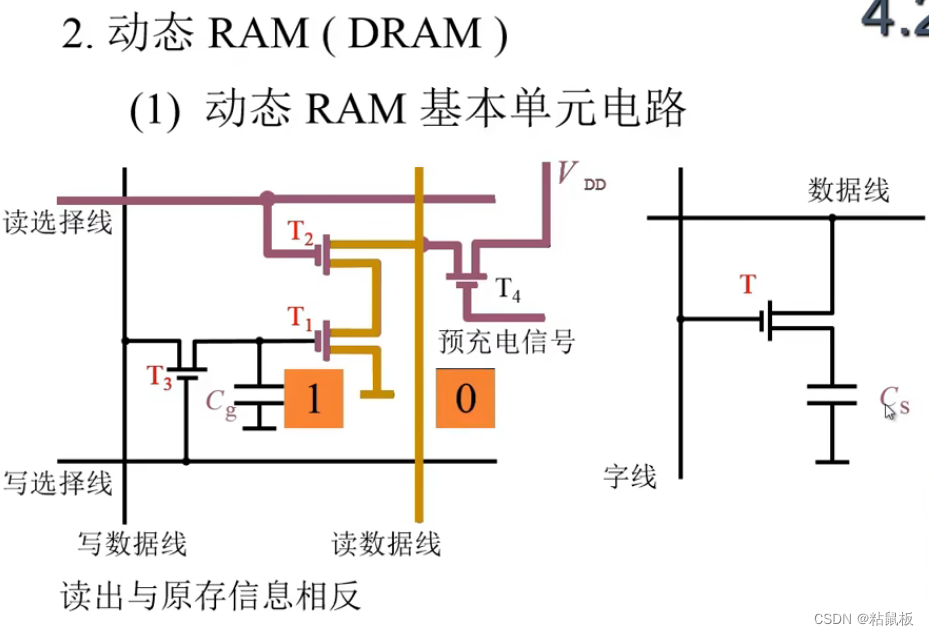

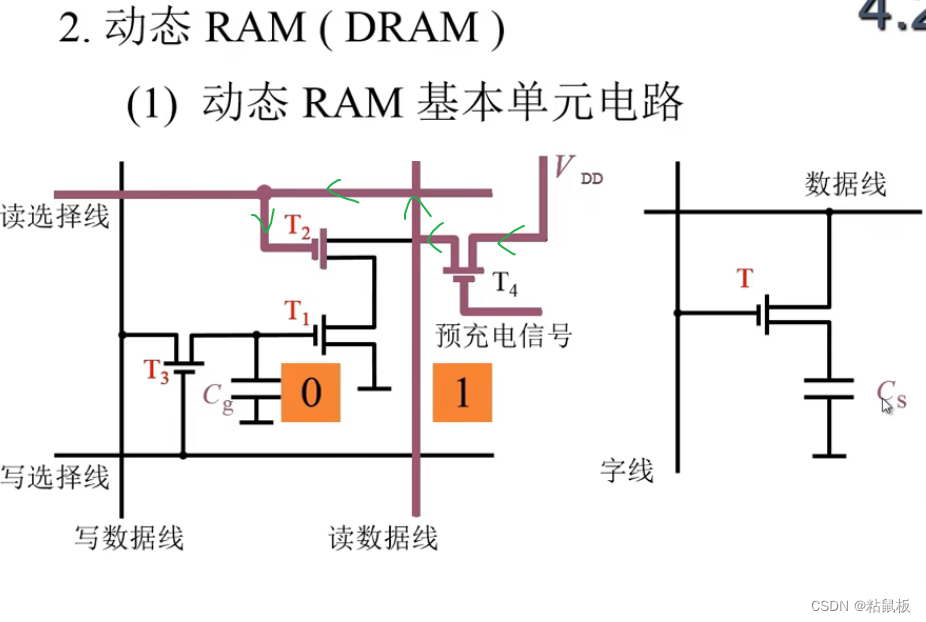

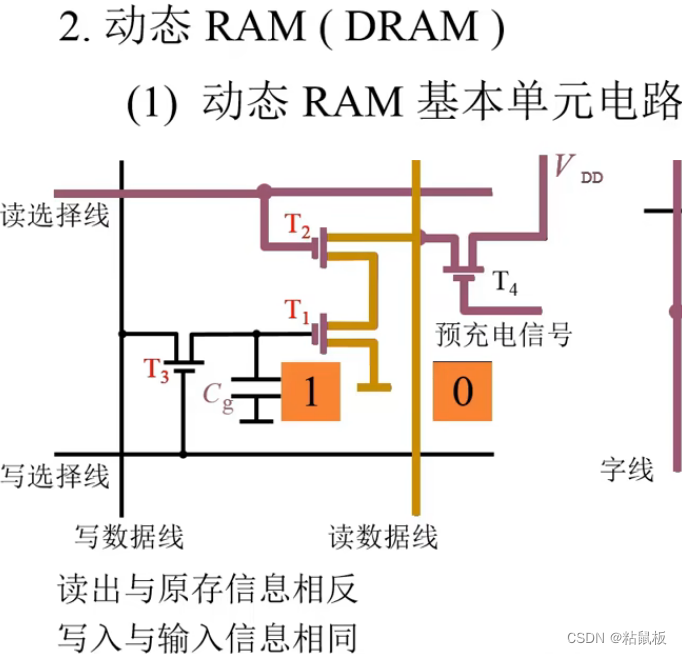

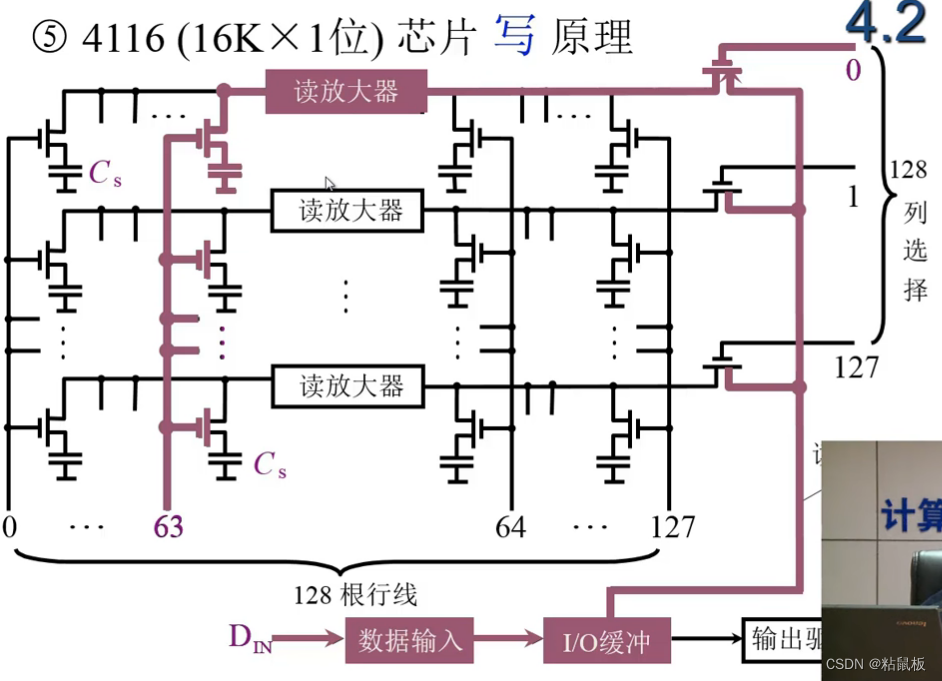

动态RAM

两根竖线中较短的那根代表栅极(那有一块绝缘层。三极管中栅极那边有电流的时候,相当于形成通路,右边的两条线可以通电,但是电不会通过绝缘板到栅极)

例如,T4通电,VDD的电流可以通过T4代表的三极管,此时电流分为两条(读数据线上有电流,通向T2的数据线也有电流),若T2通电,电流继续流通到T1处,此时,Cg如果是高电平,T1通路打开,电流流向T1右下侧的线路,到达地线,被大量放电,所以此前电流的另一条分支,读数据线上没有了电流,信号变为0;

相反,如果Cg为低电平,读数据线上信号为1

写入数据时,当写数据线为高电平时,T3连通,Cg充电变为高电平,存储信息为1;当写数据线为低电平时,Cg相当于接地放电,存储信息为0

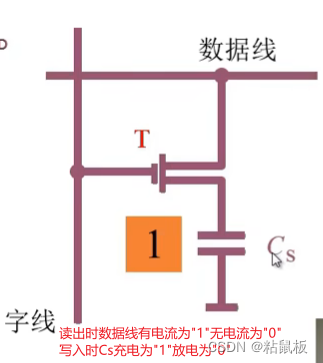

如果相应的行被选中,该行所在的字线控制T打开

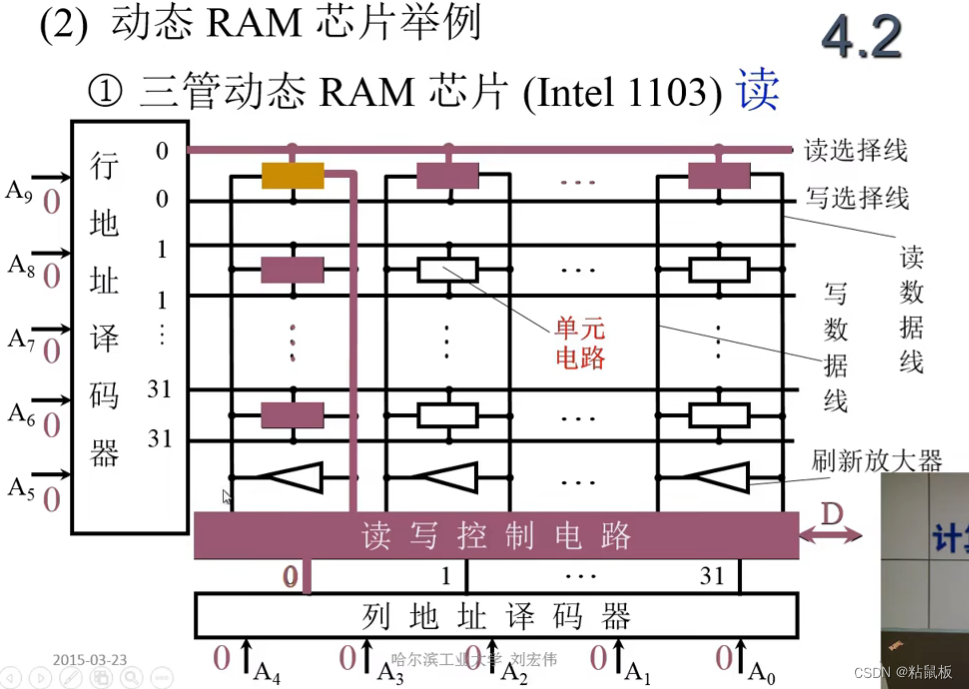

1K×1位

刷新放大器:读一次之后电容中电荷减少(电容漏电),需要刷新充电补电荷

读放大器:跷跷板电路,左右两段电平相反作用是保持一致:因为读操作的时候,只有0~63那边存的是0,IO读出才为1;所以写操作的时候,要是IO写入为1,实际上0~63那边会存储0。

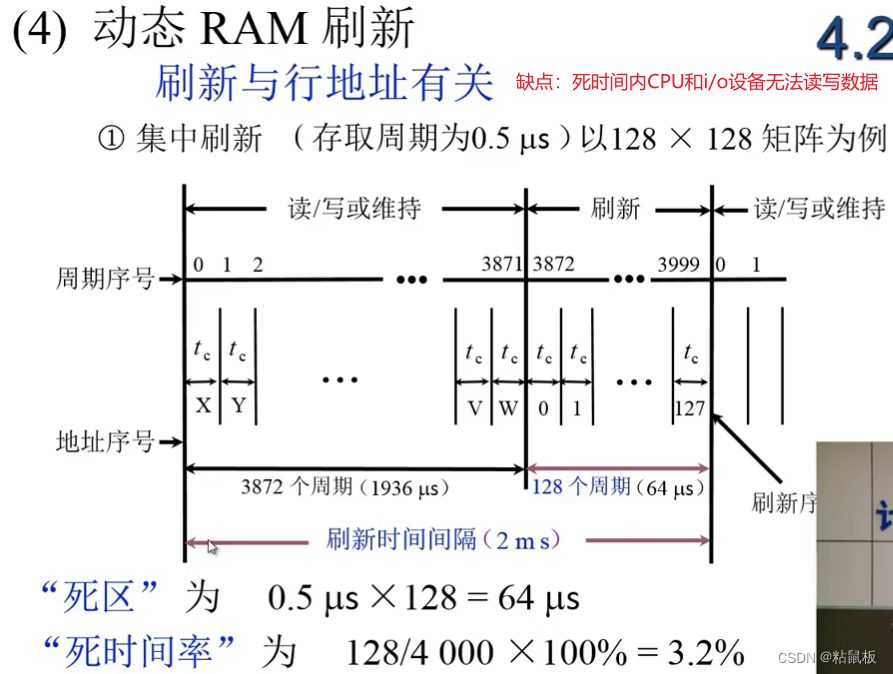

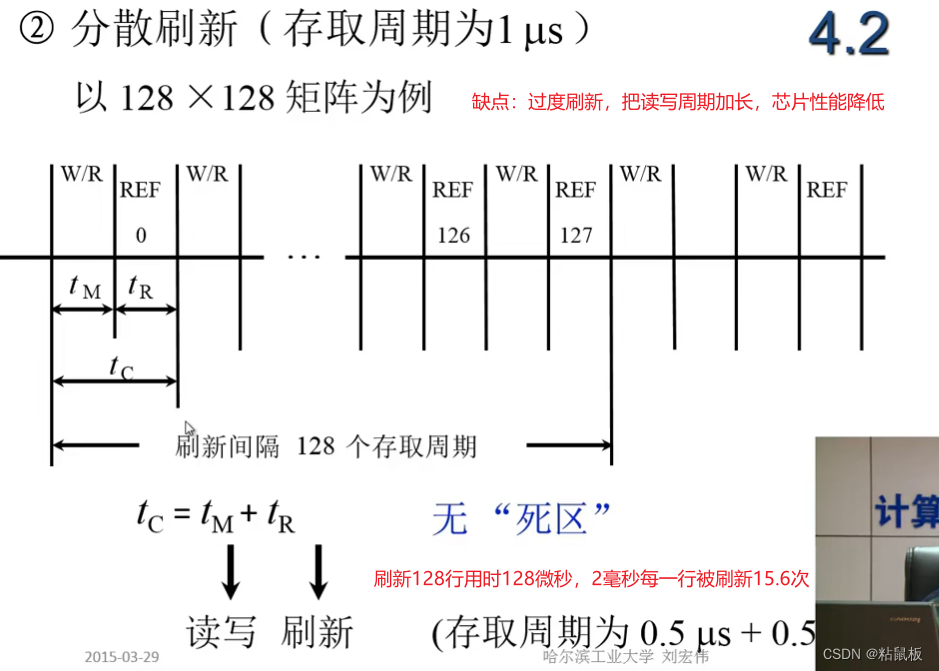

动态ram刷新的原因是因为电容会漏电,原来的1会慢慢变成0。且只和行地址有关(刷新一整行),与列地址没有关系。

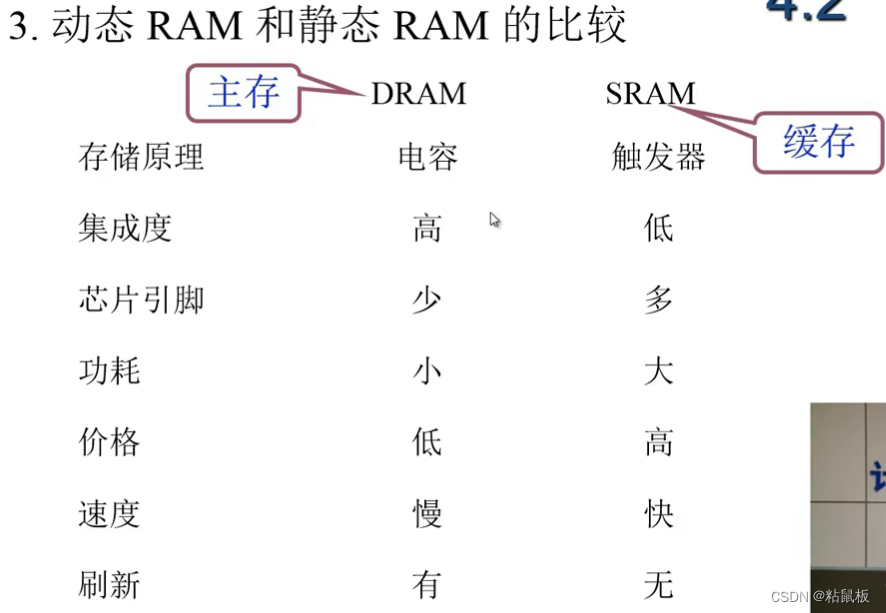

动静态RAM比较

引脚这里就是行地址和列地址线的多少,静态需要同时存放行列地址的消息,而动态行列用的是同一组地址线,只是不同时间传入不同消息,先传行再传列

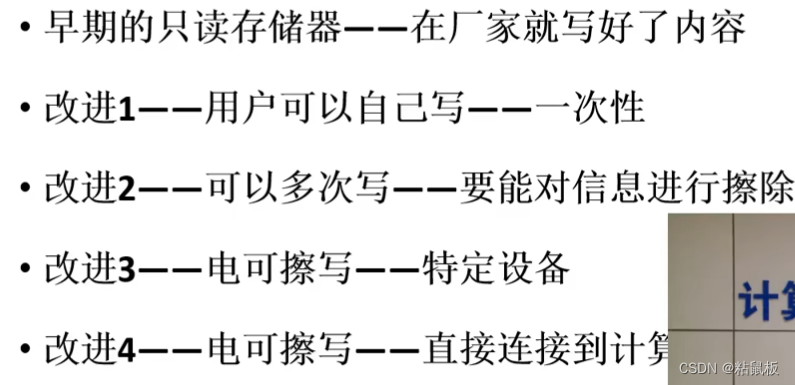

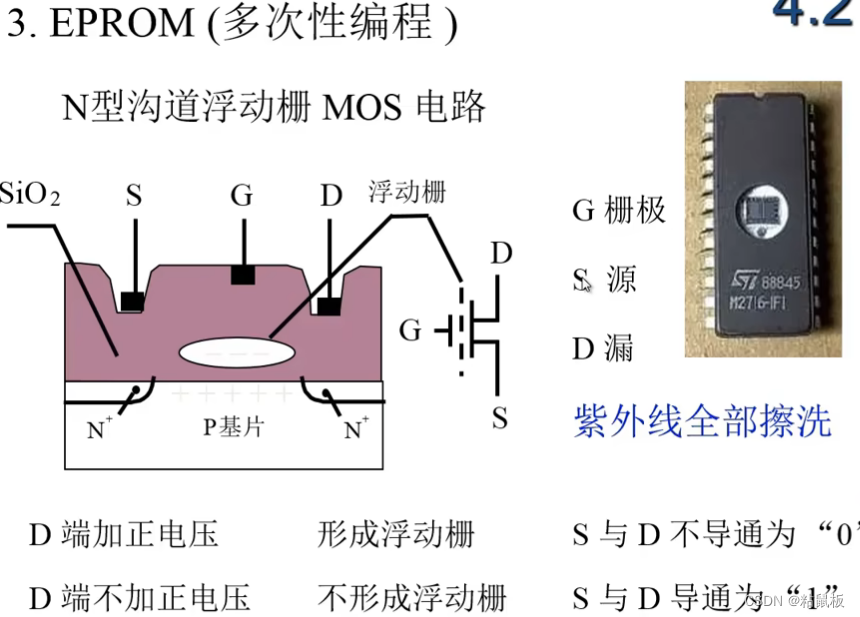

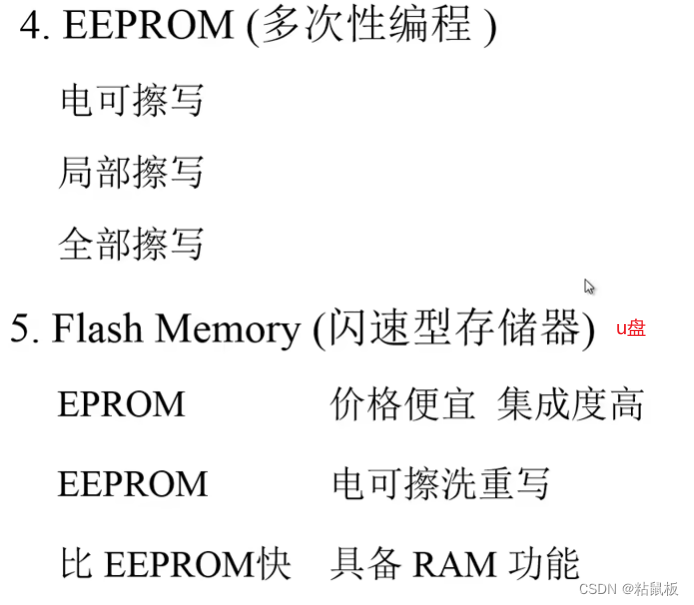

只读存储器(ROM)

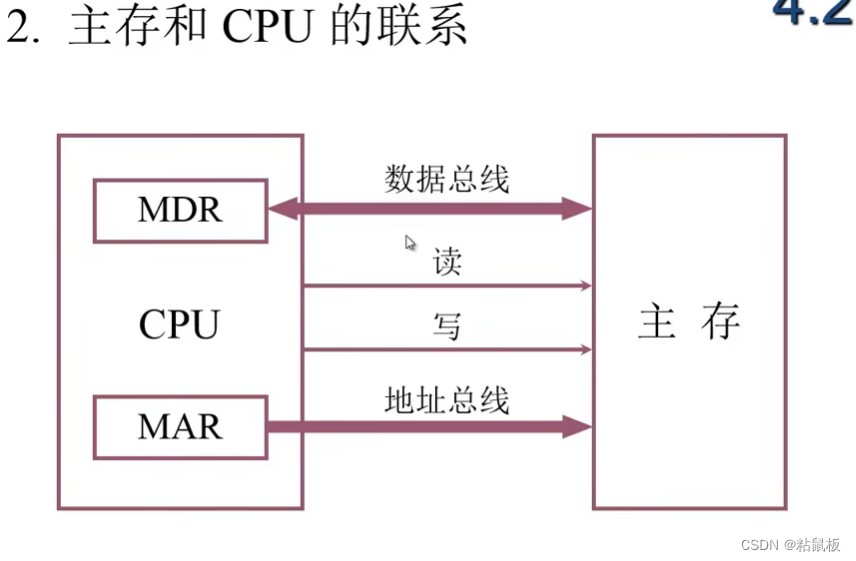

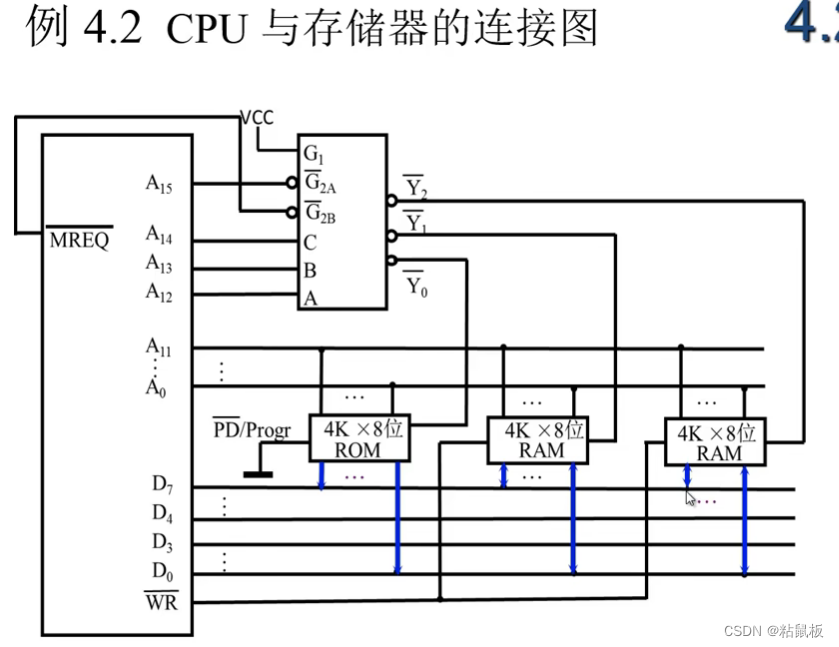

CPU和存储器的连接

存储器容量的扩展

两个芯片看成一个同时工作

两个芯片不能同时工作会输出16位数据

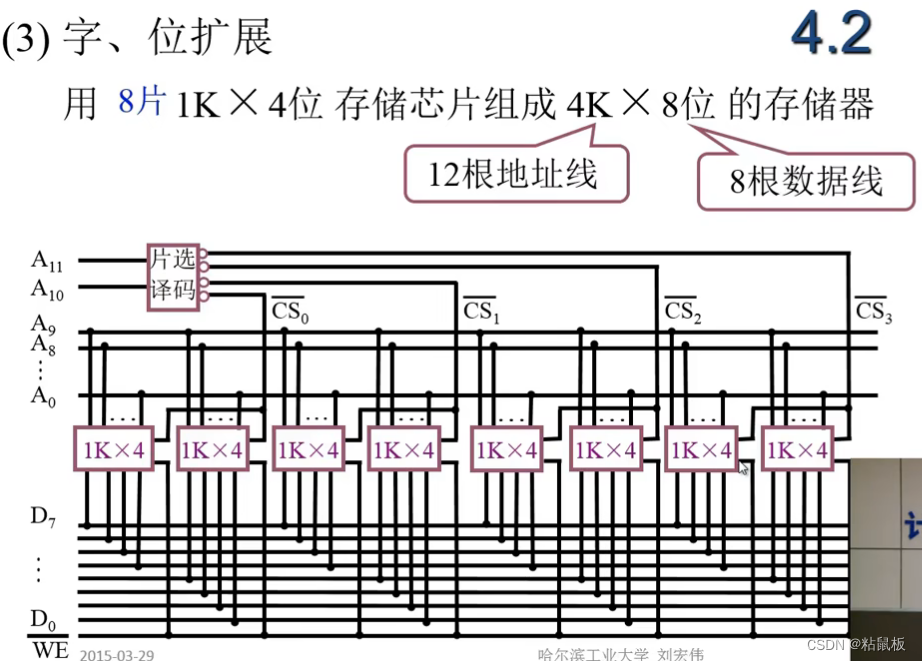

那么10根地址线如何解决2K的存储呢?只需要多一根A10地址线.

当A10为0,A0~A9为1/0,存储在第一个芯片中

当A10为1,A0~A9为1/0,存储在第二个芯片中

4K存储容量也就是4210=2*12需要12根地址线具体原理和字扩展一样,00代表第一组芯片;01代表第二组芯片;10代表第三组芯片;11代表第四组芯片

8位需要8根数据线

存储器与CPU的连接

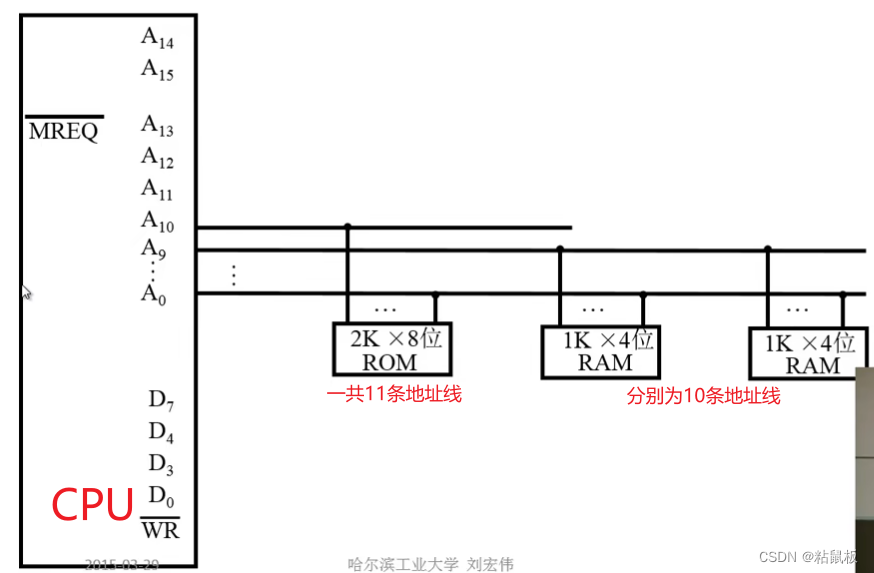

书例1:

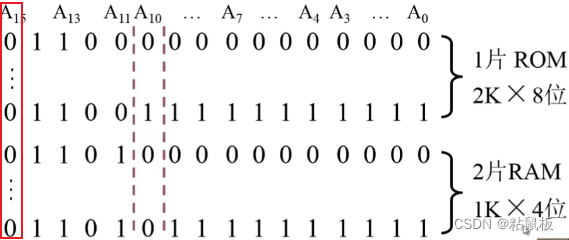

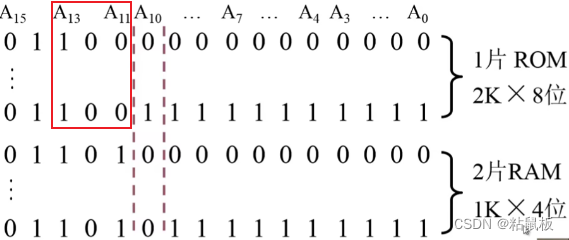

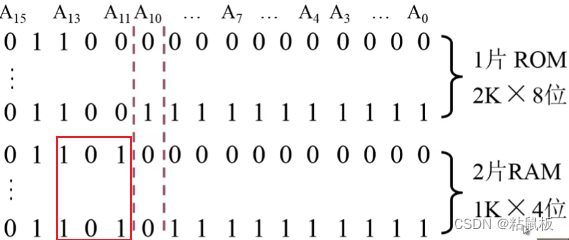

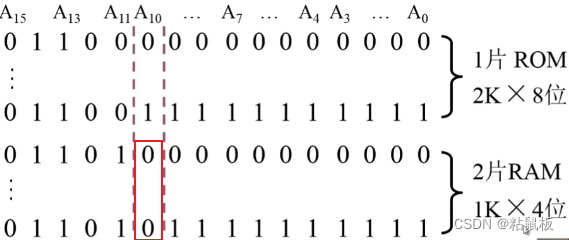

主存地址空间分配:

6000H~67FFH为系统程序区

6800H~6BFFH为用户程序区

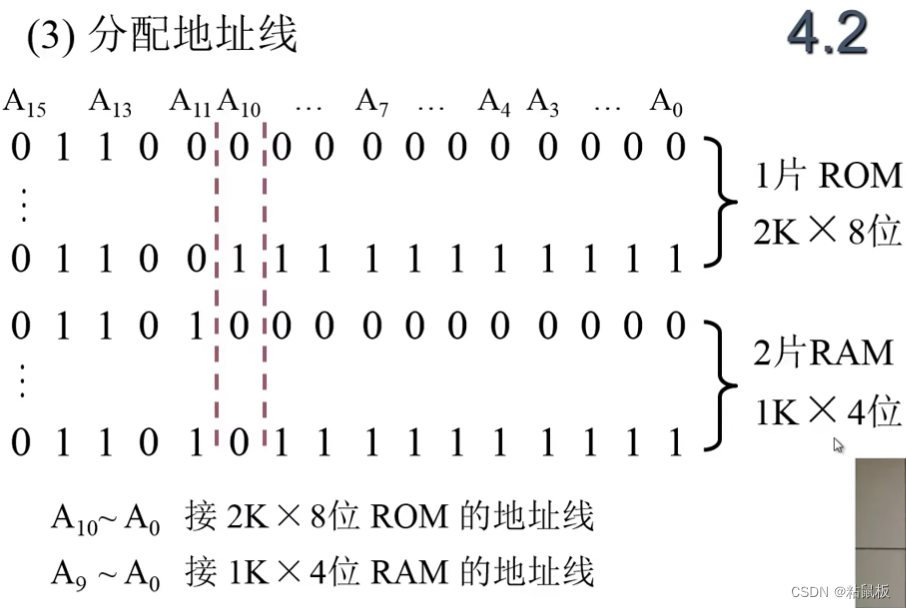

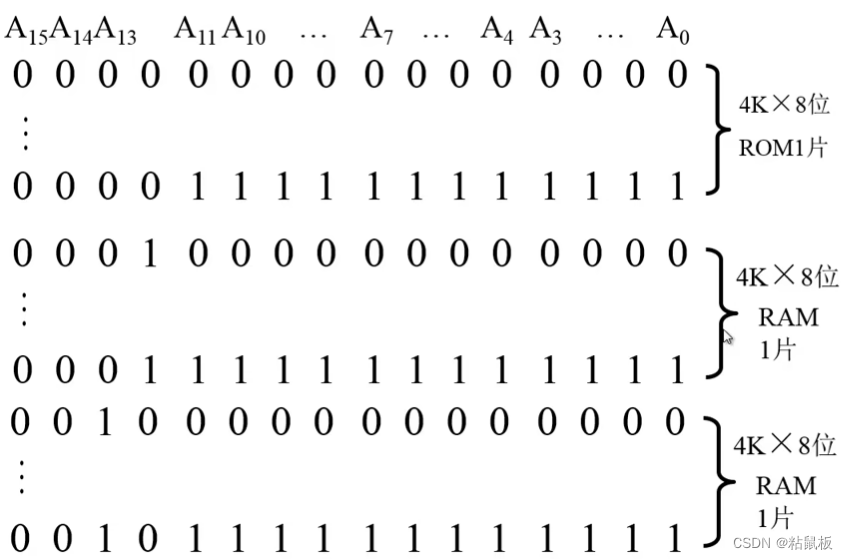

第一步:先将十六进制地址范围写成二进制地址码,并确定其容量

6000H=[0110][0000][0000][0000]B=0110 000000000000B

67ffH=[0110][0111][1111][1111]B=0110 011111111111B

6800H=[0110][1000][0000][0000]B=0110 100000000000B

6BFFH=[0110][1011][1111][1111]B=0110 101111111111

一共是16位,所以总容量为64K

第二步: 根据地址范围的容量以及该范围在计算机系统中的作用,选择存储芯片

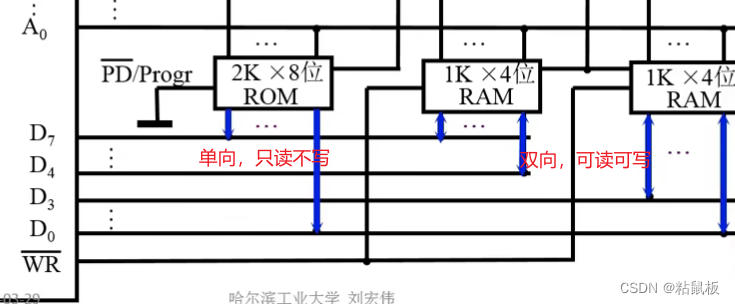

根据系统程序区的范围,应该选择2K8位的ROM

根据用户程序区的范围,选2片1K4位的RAM–1K*8位

第三步: 分配地址线

第四步:片选信号的形成

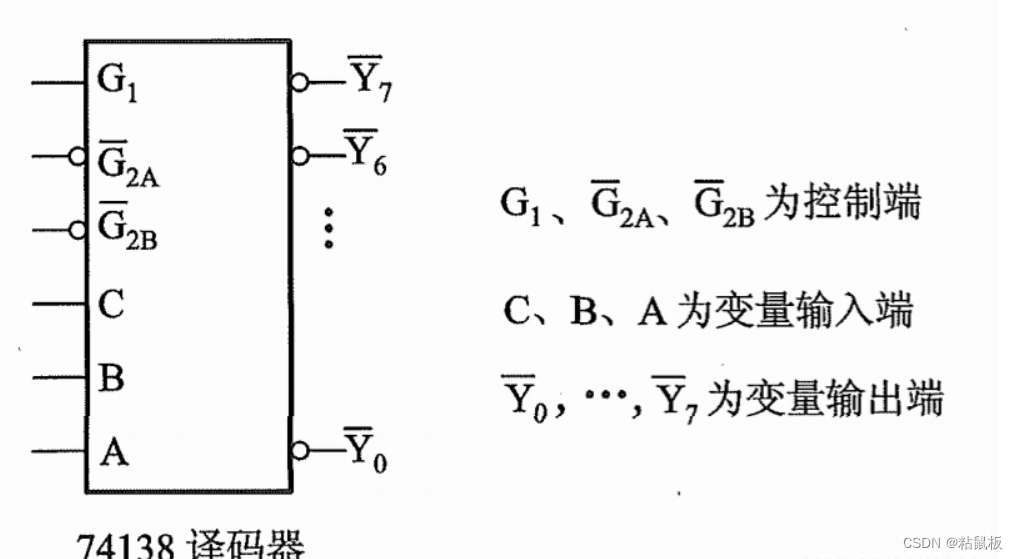

74138译码器原理:

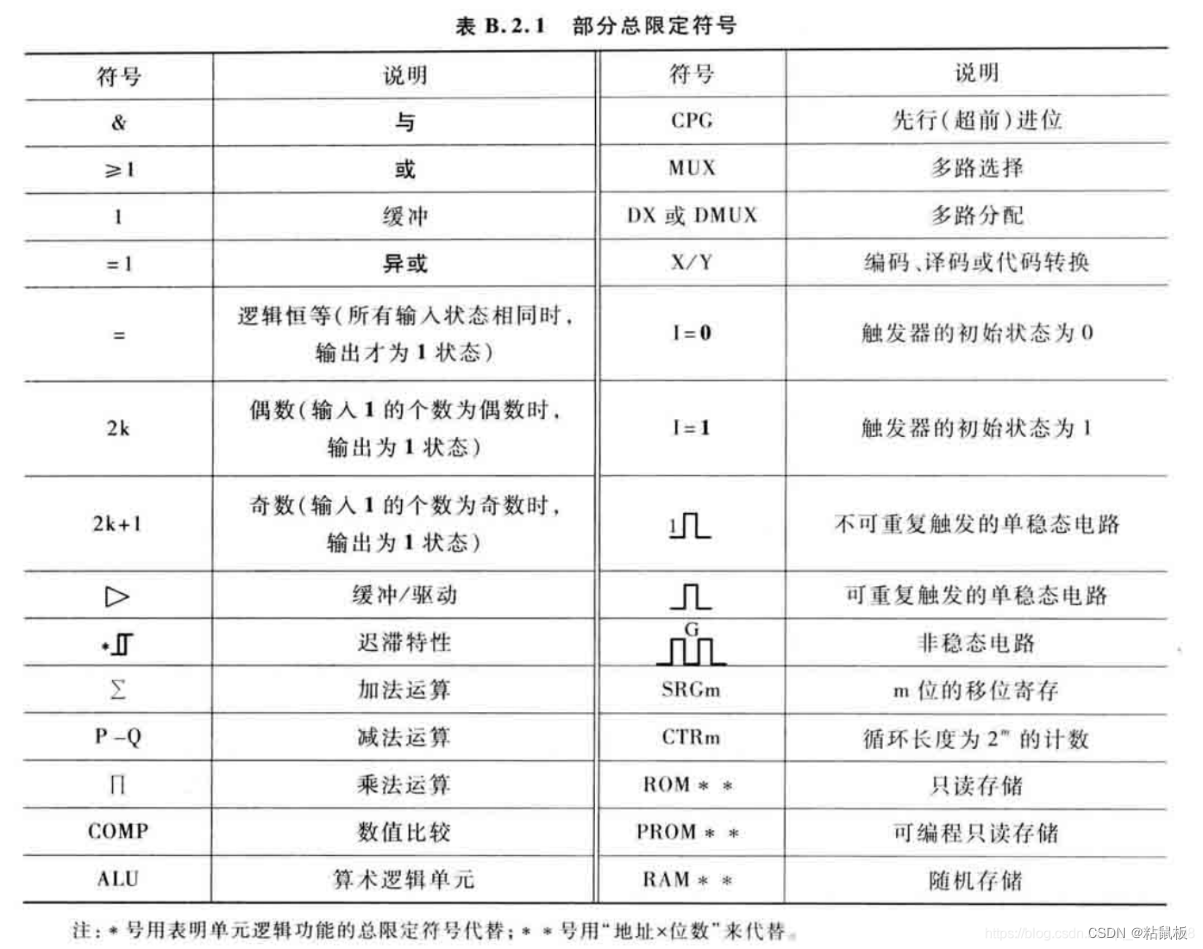

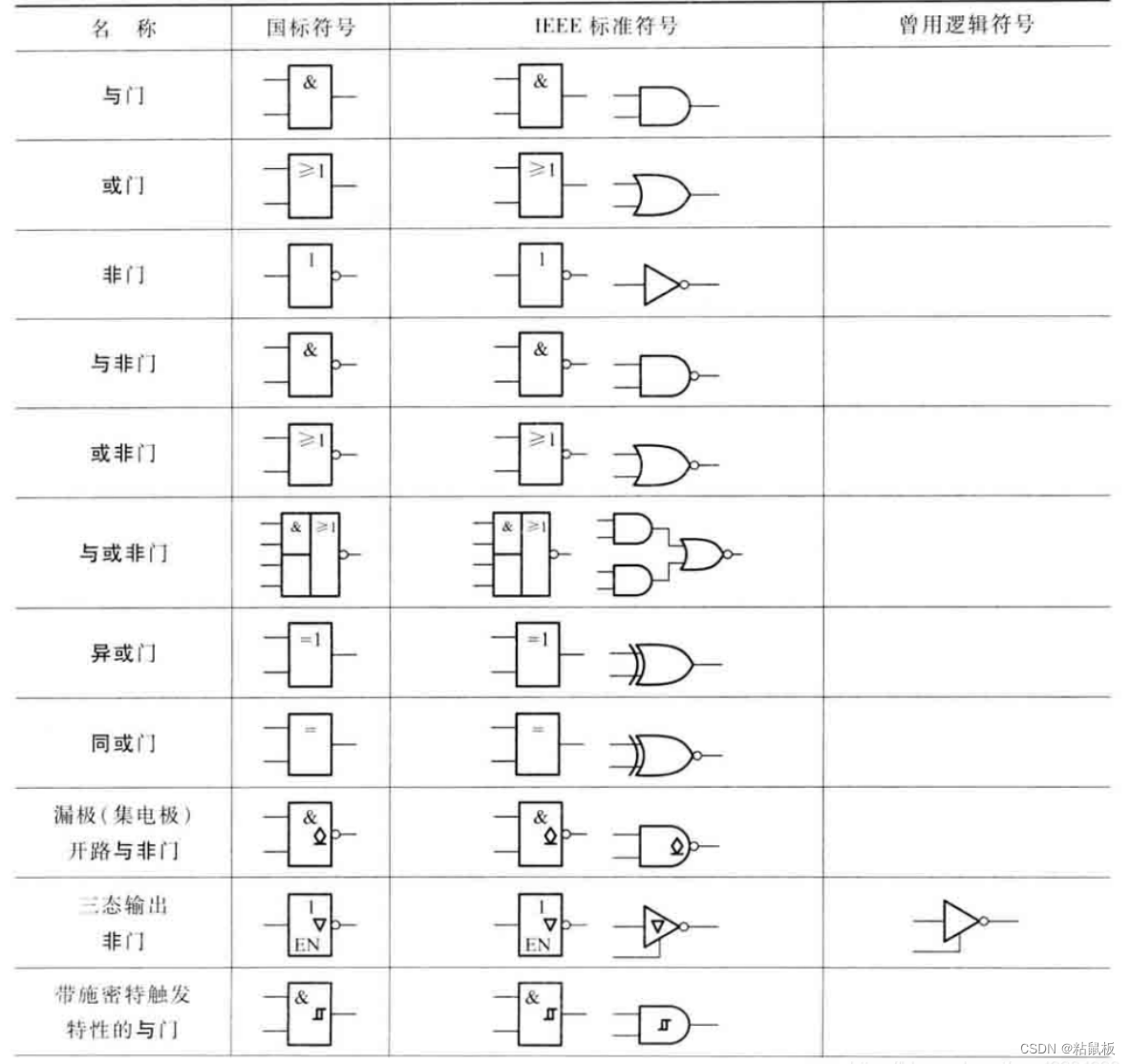

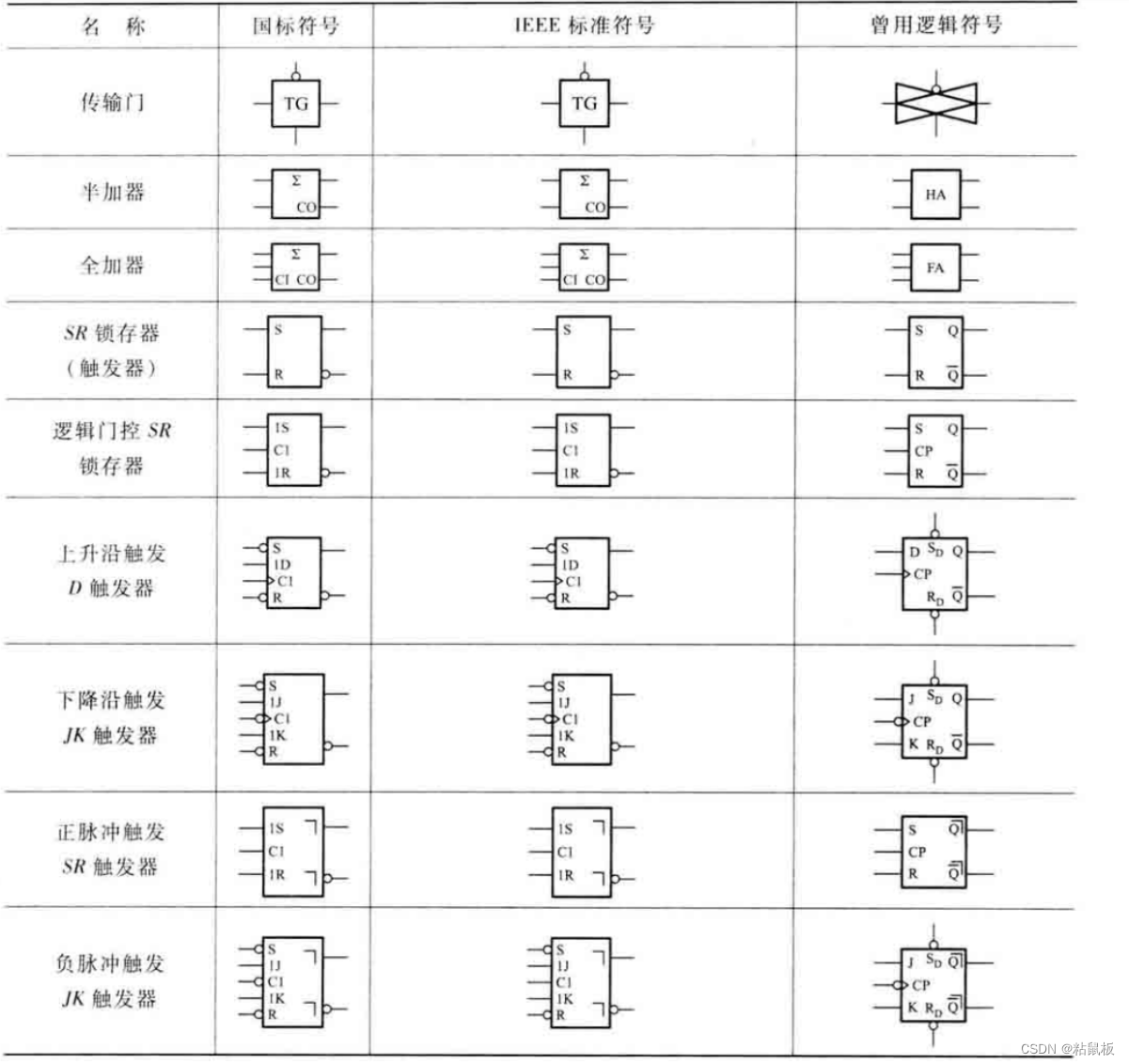

1. 快速理解基本的电路符号

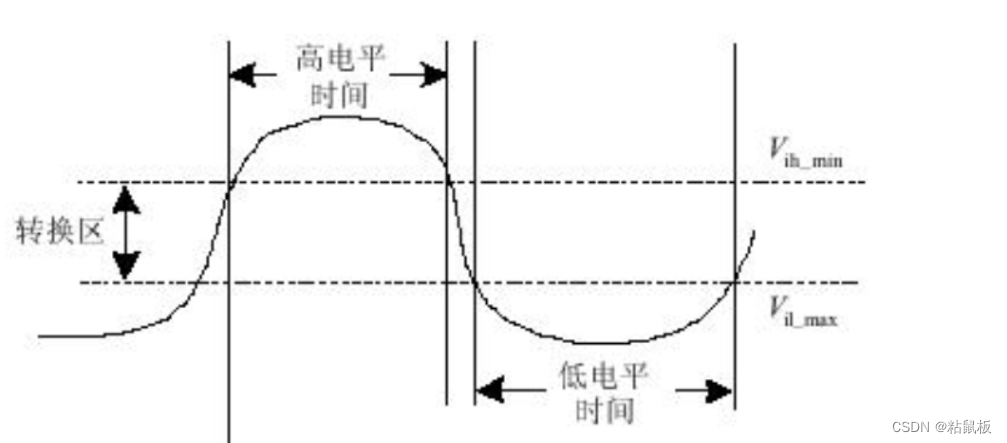

a.高低电平

我们总说,计算机只读得懂0和1,那么如何用电路实现0和1呢,是通过分辨电路信号是高电平还是低电平,这里电平指的是电压。因此高低电平是我们分辨0和1的信号。下文我们用0表示低电平,1表示高电平。

b. 高电平有效和低电平有效的理解及表示

高电平有效的意思是,当电路的电信号为高电平的时候,触发下级电路(也就是触发后面的电路),低电平理解同理。

另外,如何看哪些电路是高电平有效,哪些是低电路有效,我们可以看字母符号,如果符号上方没有横线,那么是高电平有效,如果符号上方有横线,则是低电平有效(低电平可以触发后面的电路)。

还可以看电路上的电线有没有圆圈,圆圈代表取非(信号取反)的意思,也就是说如果传入的信号是高电平,则转换成低电平,低电平则转换成高电平。如果电路上接线上有圆圈,则低电平有效,若没有则高电平有效

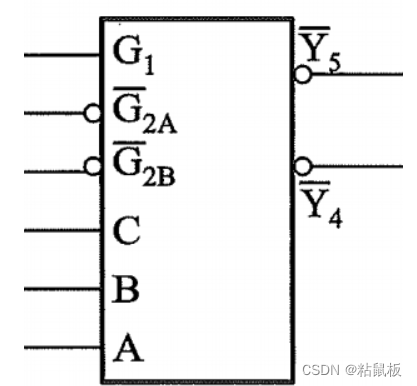

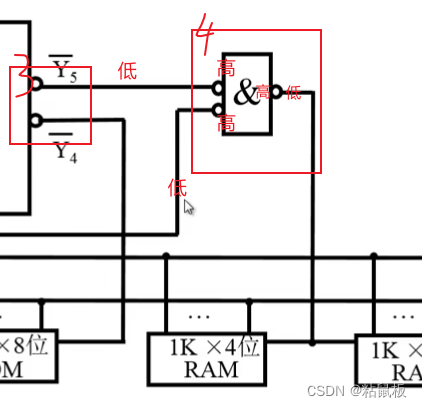

例如,上图为74138译码器的电路简图(用的是唐书例4.1中的图),可以很明显的看到,G2A和G2B是低电平有效(也就是要传入低电平,才能触发下面的电路),而且输出的Y4和Y5,也都是低电平有效(如果是输出,则输出的是低电平),我们首先搞懂了74138译码器的输入输出哪些是低电平哪些是高电平的问题。

c.基本的门元件

2. 数电小白也能看得懂的74138译码器

a.译码

首先,译码的意思是将二进制串转换为特定的对象(或逻辑电平)。比如将二进制串转换为十进制数就是译码的过程,将 0100 二进制转换为十进制 4 就是译码的过程。

b. 74138译码器原理

74138译码器实质是3-8译码器,意思是将3位二进制转换为1位八进制数(0~7的数字),因此叫3-8译码器,这是74138译码器的主要目的,记住这个!!!

c. 74138译码器结构功能

这是74138译码器的结构,我们首先来关注Y0~ Y7,C,B,A这输出和输入端

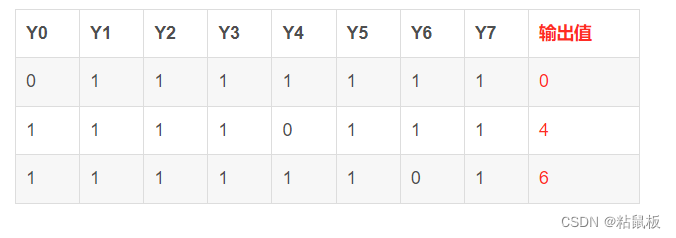

Y0 - Y7是8个输出端,输出这个八进制数。我们刚才知道74138译码器是要将二进制串转化为八进制数,那么该如何用电路模拟这八进制数呢? 聪明的你应该能猜到,如果是Y0输出了信号,那么就相当于输出0,如果是Y3输出了信号,那么相当于是输出了3,其他同理。 而且这些输出都是低电平有效,当Y0为低电平的时候,其他为高电平,就表示输出了0。详情如下表

C、B和A是3个输入端,作用是输入二进制数的,而且高电平表示1,低电平表示0,这样我们就可以完成二进制输入。例如A为第一位,C为第三位,A输入0,B输入1,C输入0,那么输入的二进制串应该是010。

而G1,G2A和G2B是控制端,相当于译码器的开关。只有控制端都有效时,译码器打开,才可以进行译码,否则不能译码。结合高电平和低电平有效,只有G1是高电平有效,而G2A和G2B是低电平有效,也就是说,只有当G1为高电平,G2A,G2B都为低电平的时候,译码器才能正常工作,其他情况均不能。

信号对应如下

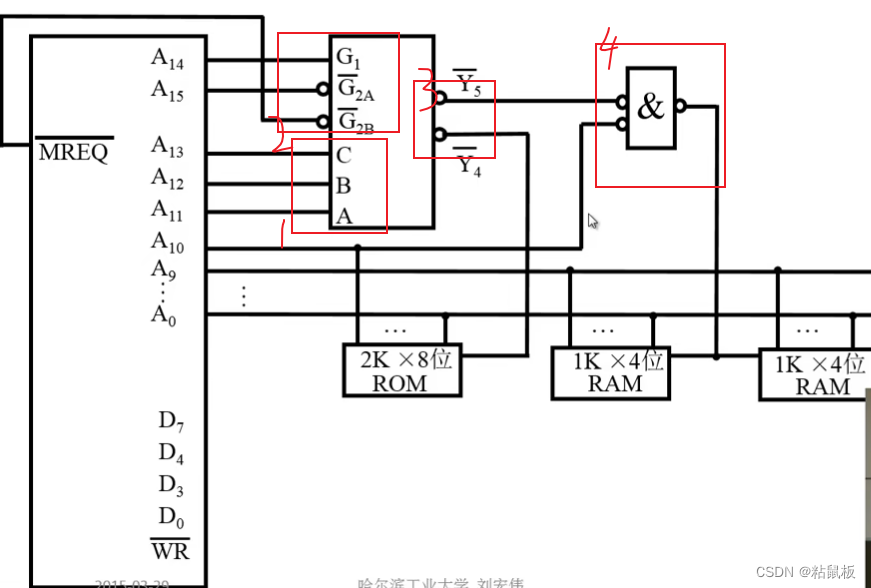

地址线连接

片选信号连接(最重要的也是最难的一步)

-

A,B,C对应三个二进制数,所以连A11, A12, A13

-

G1为高电平有效,连A14;G2A 和 G2B为低电平有效,选其中一条连 A15为什么呢?

我们需要结合之前的地址线分配,发现A15这列全为0,也就是低电平,A14这列全为1,都是高电平;

最后G2B连接MREQ要让MREQ通过译码器控制启动ROM和RAM -

当Y4有效时,选择ROM;当Y5有效时,选择RAM

Y4对应的二进制编码为100,也就是A13 ,A12 ,A11 的信号为 100,所以选ROM

Y5对应的二进制编码为101,也就是A13 ,A12 ,A11 的信号为 100,所以选RAM

-

结合之前的地址分配,我们发现当选择RAM时,A10为低电平,同时Y5输出端也为低电平,为了能使选择有效,需要安装一个与非门

数据线连接(ROM不连读写线)

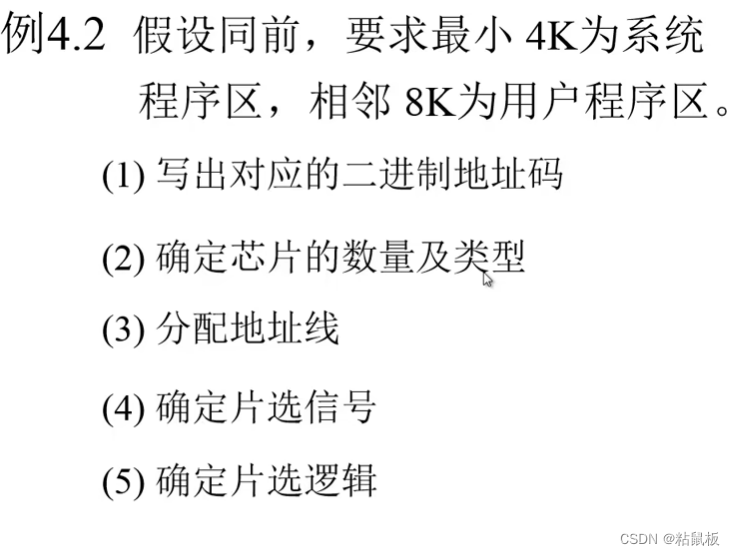

因为是相邻的,所以必须从加一的下一个地址位开始,但是下一个地址位全一到全0只能提供一半,所以再加一从下下个地址位找到另一半。

存储器的校验

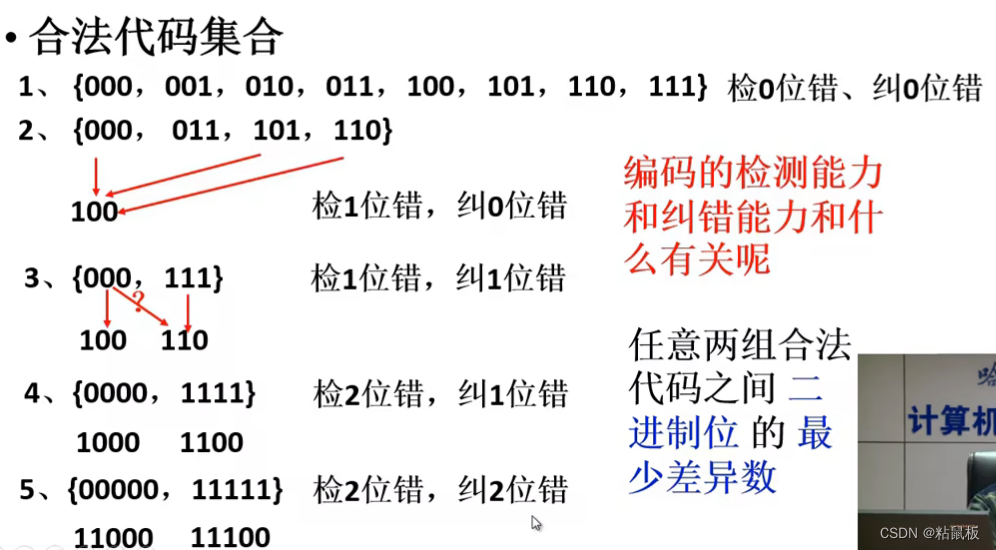

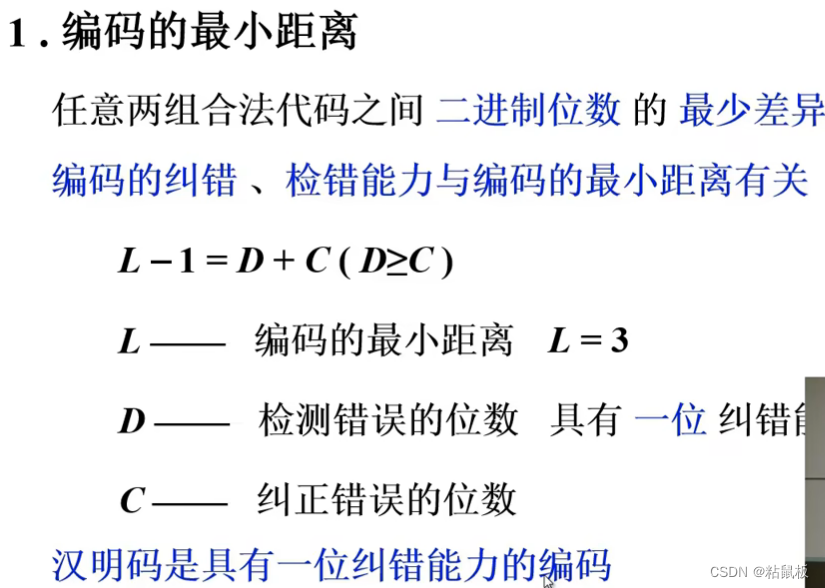

以第4个为例,检错就是知道代码不在合法代码集合里,纠错就是可以将与合法代码相差位数个数最小的判定为该合法代码

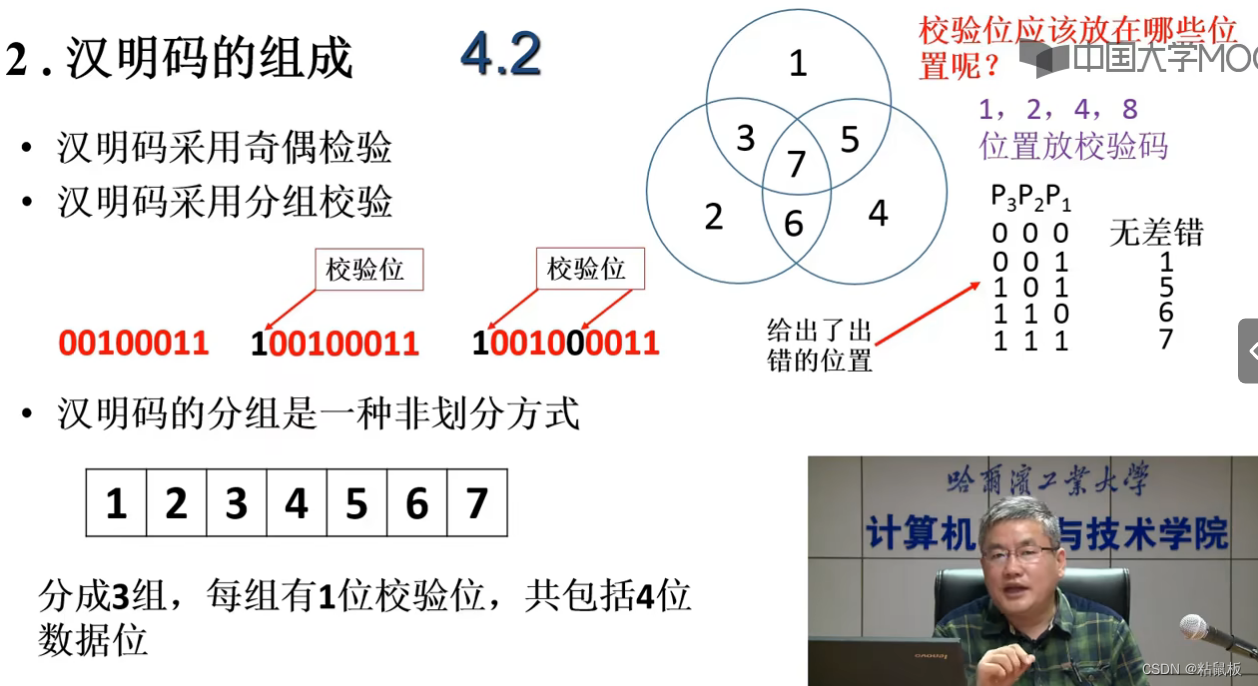

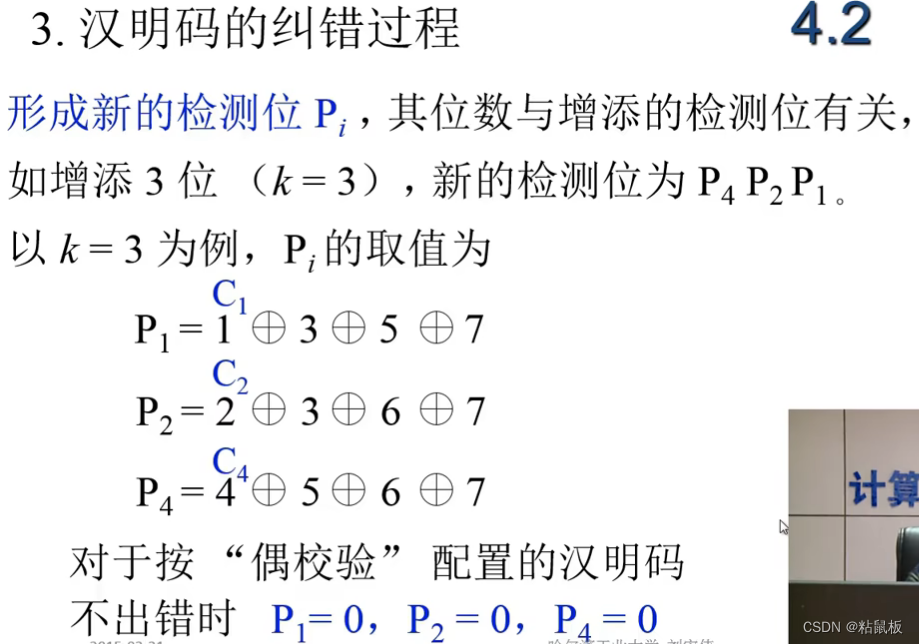

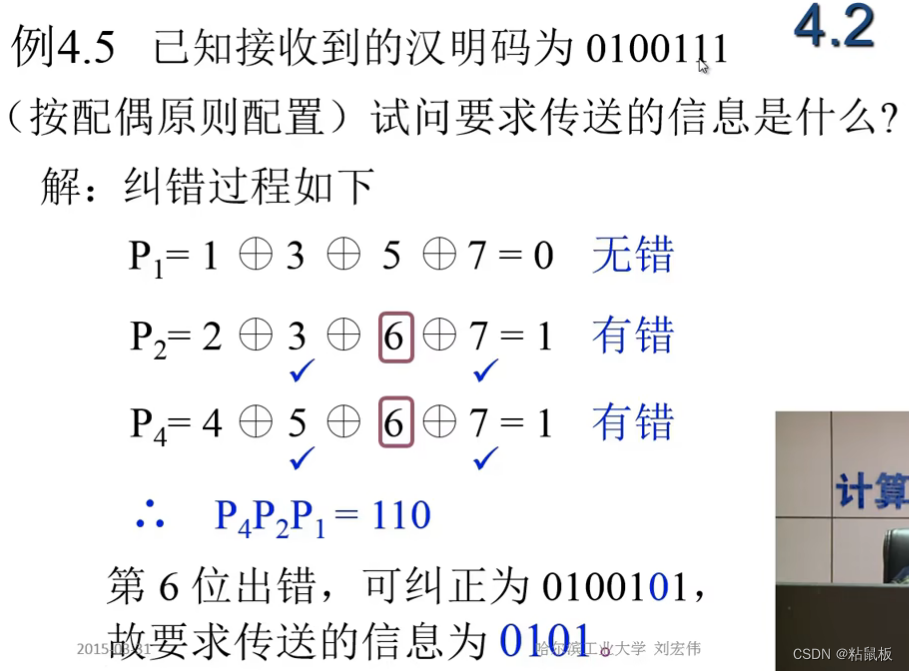

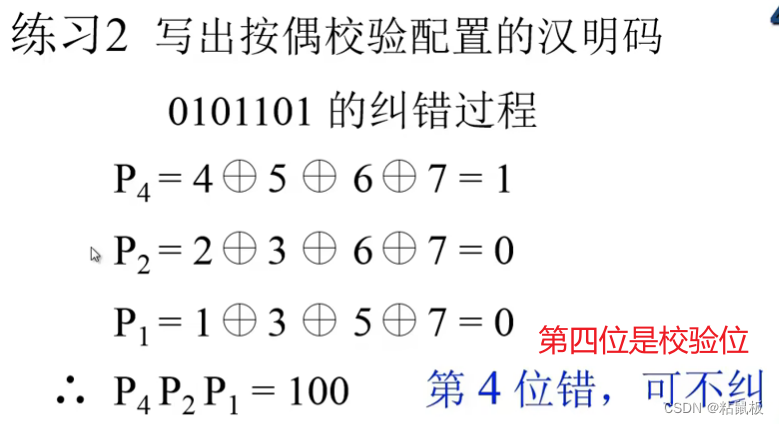

汉明码:得到一个二进制的值换算成十进制就是出错代码的位置

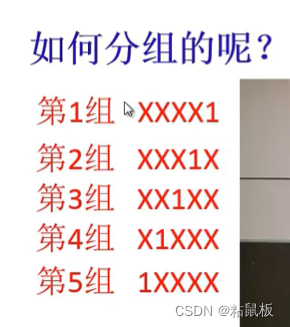

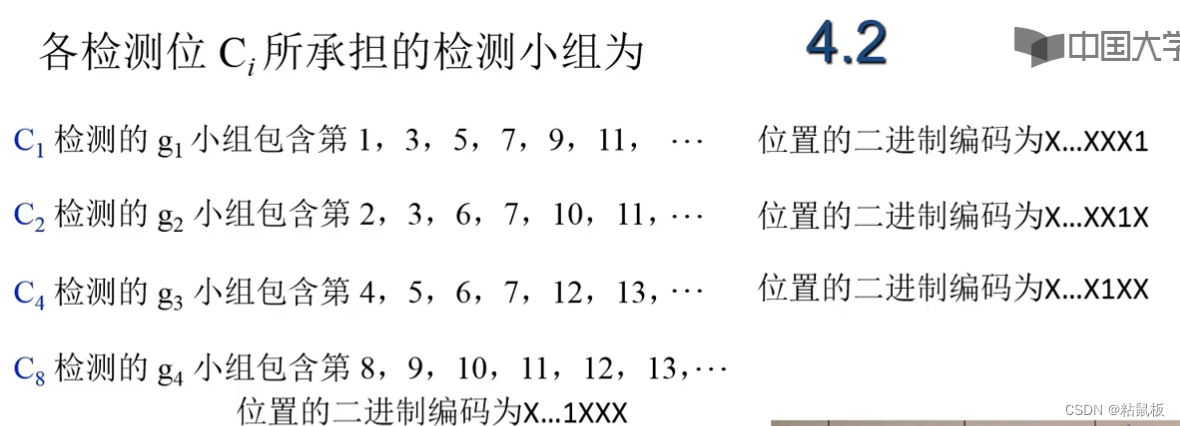

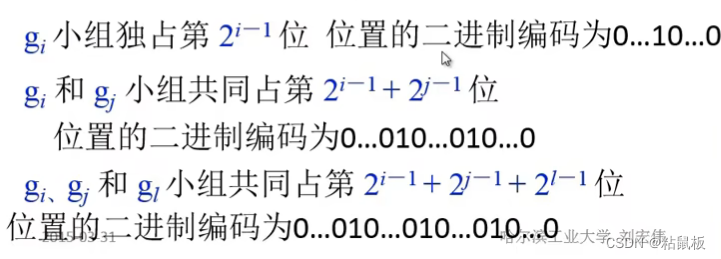

第一组:1、3、5、7,用二进制代码表示为01、11、101、111,最右侧都为1

第二组:2、3、6、7,用二进制代码表示为10、11、110、111,从右往左第二位都为1

第三组:4、5、6、7,用二进制代码表示为100、101、110、111,从右往左第三位都为1

如果第一组和第三组出错,按照偶校验的规则,第一组从右往左第一位为校验位,值为1;第二组从右往左第二位为校验位,没有出错,所以值为0;同理,第三组值为1.三组得到的二进制编码为101——对应的十进制数为5,也就是第5个位置出错了

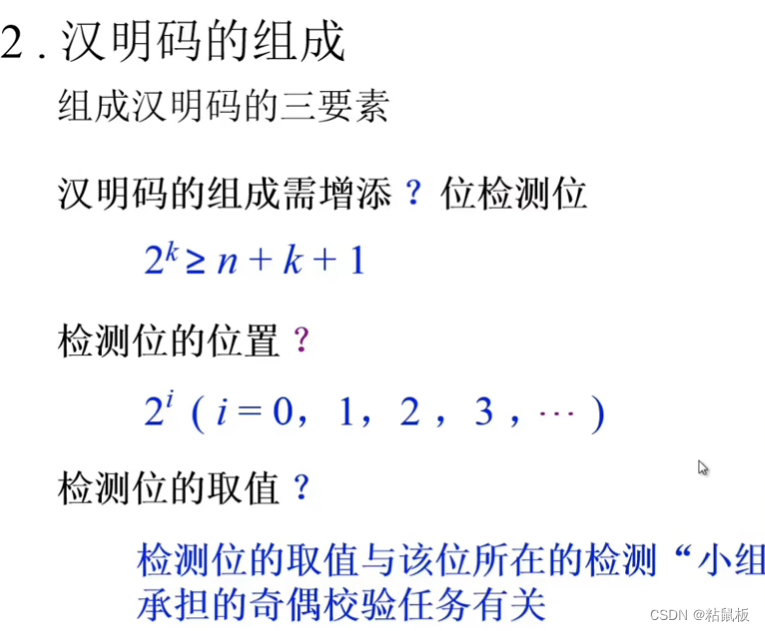

添加?位检测为实际上就是几组

k是校验位,n是原始数据的位数。所以k+n就是原始数据加上校验数的位数。所以k位检验数可以得到2k-1个错误位。为了校验k+n位,所以有 2k-1≥n+k.

C1校验位:包含1、3、5、7;5和7为1,1的个数为偶数个,校验码为0

C2校验位:包含2、3、6、7;只有7为1,1的个数为奇数个,校验码为1

C3校验位:包含4、5、6、7;5和7为1,1的个数为偶数个,校验码为0

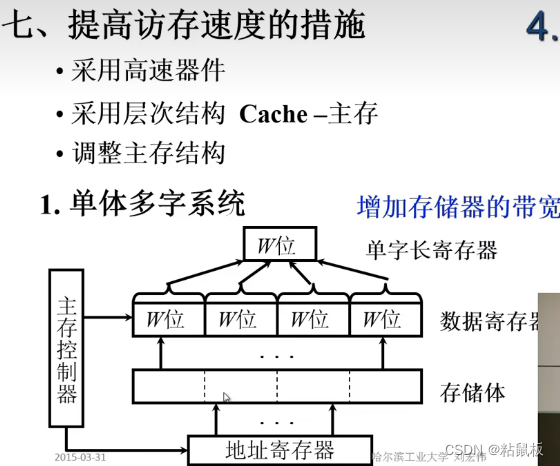

提高访存速度的措施

机器字长:CPU一次能处理二进制数据的位数

缺点:

1、当写入数据时,假如我们只需要写入16位数据,但是数据寄存器中却有16*4位数据,于是其他48位数据也会被写入给定的存储单元中,造成给定的存储字有48位被修改。

2、假如取出数据或指令不连续时,例如取出第一条指令是跳转指令(超出了这4条指令的范围),那么取出的4条指令中只有第一条有效

增加了容量,但带宽(访存速度)没有很大提高

缺点:

1、程序是由指令和数据构成的,假设第一条指令存储在M0的第0号位置,那么按照顺序编址的规则,会造成M0比较繁忙,其余存储体比较闲

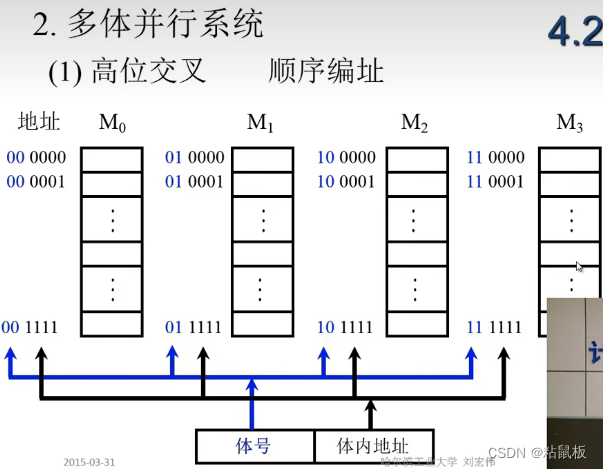

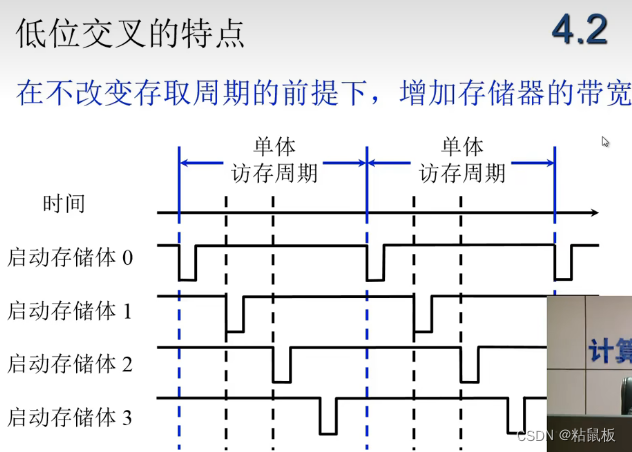

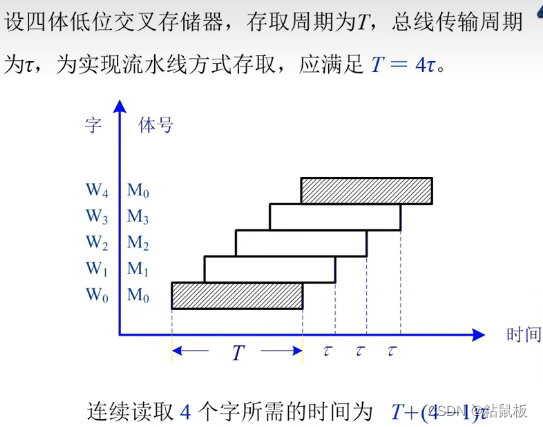

都是流水,高位线性流水,低位并行流水

高位交叉用来提高存储容量,低位交叉用来提高访问速度

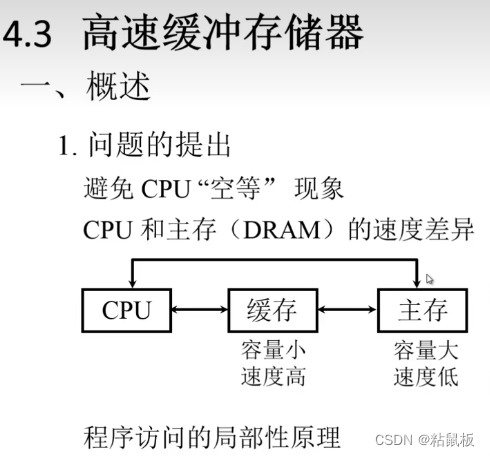

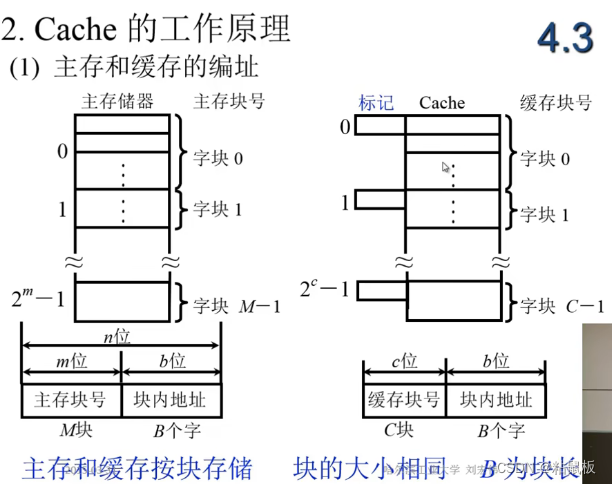

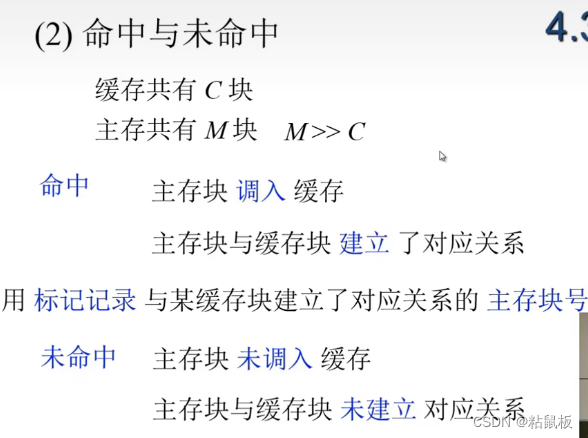

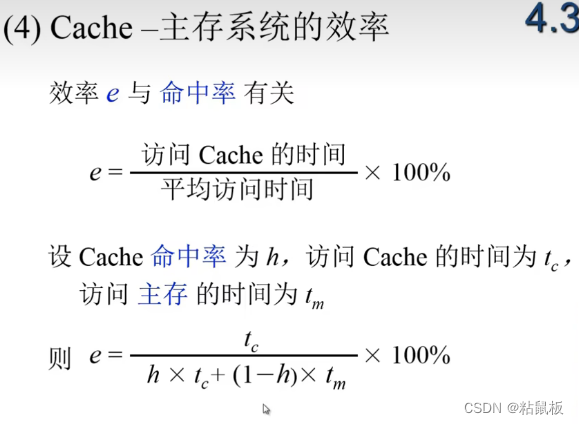

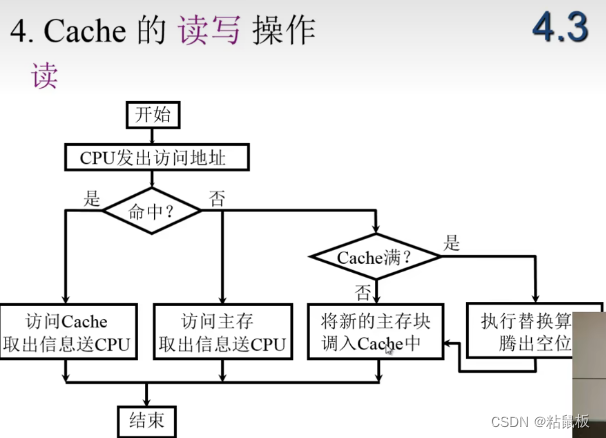

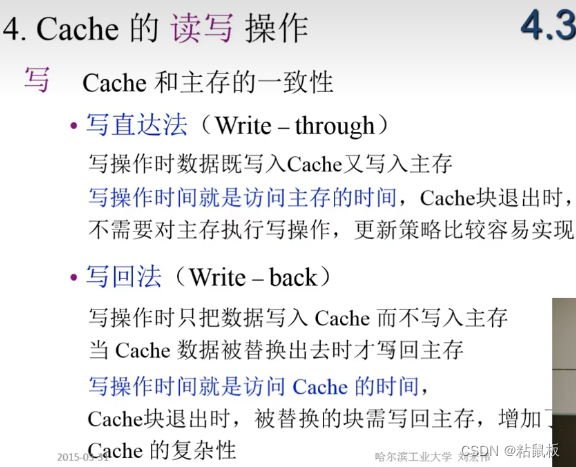

高速缓冲存储器

程序访问的局部性原理:

1、时间局部性:当前访问的数据和指令,在不久的将来还会被访问

2、空间局部性:当前正在使用的指令和数据,相邻的指令和数据可能也会被用到

块太大会导致从主存传输到cache速度变慢;块太小相当于信息用的比较快

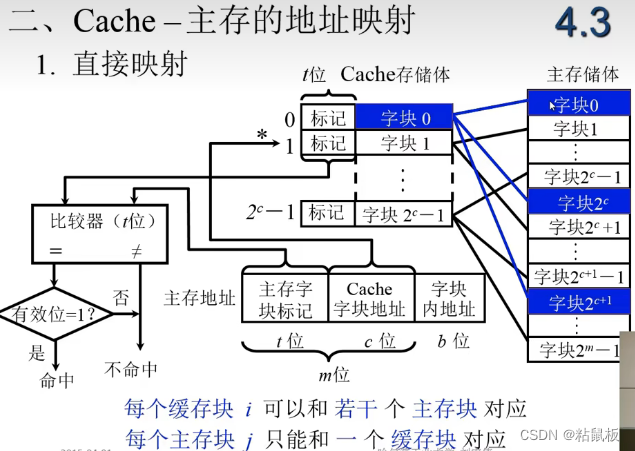

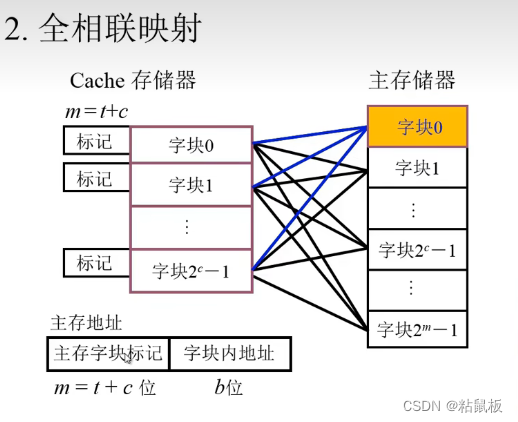

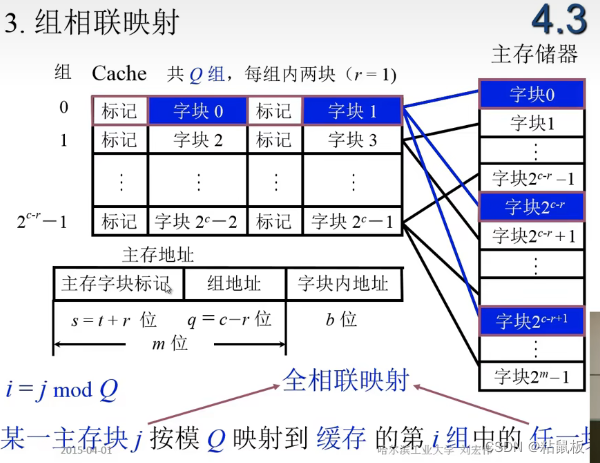

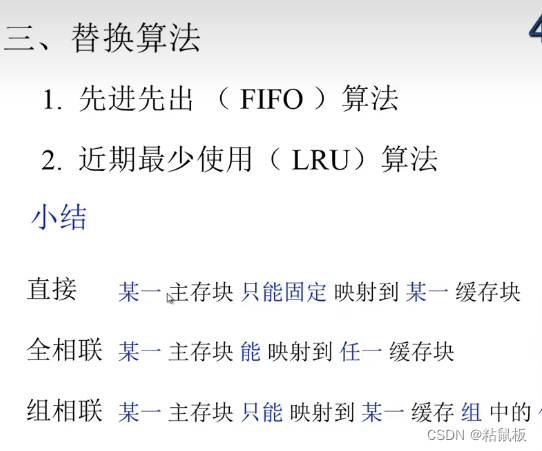

组间直接映射,组内全相联映射;块号对应组号,标记对应区号

就是说cache组中的每一个块的标记只标记主存中的区号,因为存在映射关系,所以在主存中的每一个字块能找到在cache中的对应的组,然后与标记位进行比较。

3322

3322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?