本文参考PCIe协议 5.0:https://download.csdn.net/download/zz2633105/89204842

本文参考intel IP用户指南:https://www.intel.cn/content/www/cn/zh/docs/programmable/683501/23-2-10-0-0/debugging-data-transfer-and-performance-25123.html

本文参考《PCIe体系结构导读》:https://download.csdn.net/download/zz2633105/89363330

如有描述错误地方,欢迎留言指出,拜谢!

AER

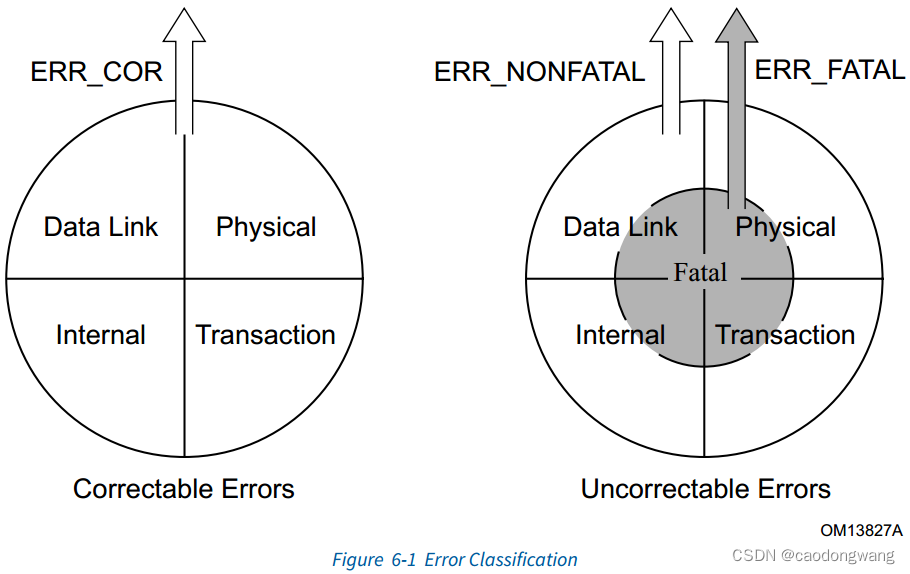

AER(Advanced Error Reporting)是一种用于检测和报告PCIe设备中发生的错误的机制,它允许PCIe设备检测到并报告各种类型的错误。错误类型包含Correctable Errors 和Uncorrectable errors两种,其中Uncorrectable errors下面又分为ERR_FATAL和ERR_NONFATAL。

Correctable Errors:可纠正错误是指错误发生后,硬件可以自动恢复,不影响正常业务。

Uncorrectable errors:错误发生后,影响设备功能,硬件不能自动恢复

- ERR_FATAL:致命错误,此错误类型影响了PCIe link链路,为了防止错误扩散,通常会由错误设备的上游桥对错误设备进行复位操作

- ERR_NONFATAL:指影响了设备功能,但是PCIe link还是稳定的

AER功能启动条件:

- 对于EP设备和RC都应该启动Command Register寄存器中SERR#Enable;

- 对于EP设备,需要将AER中不可纠正错误掩码和可纠正错误掩码清空;

- 对于EP设备,需要将Device Control Register寄存器中Correctable Error Reporting Enable、Non-Fatal Error Reporting Enable、Fatal Error Reporting Enable、Unsupported Request Reporting Enable功能打开;

- 对于RC,需要将AER Root Error Command Register寄存器中Correctable Error Reporting Enable、Non-Fatal Error Reporting Enable、Fatal Error Reporting Enable功能打开。

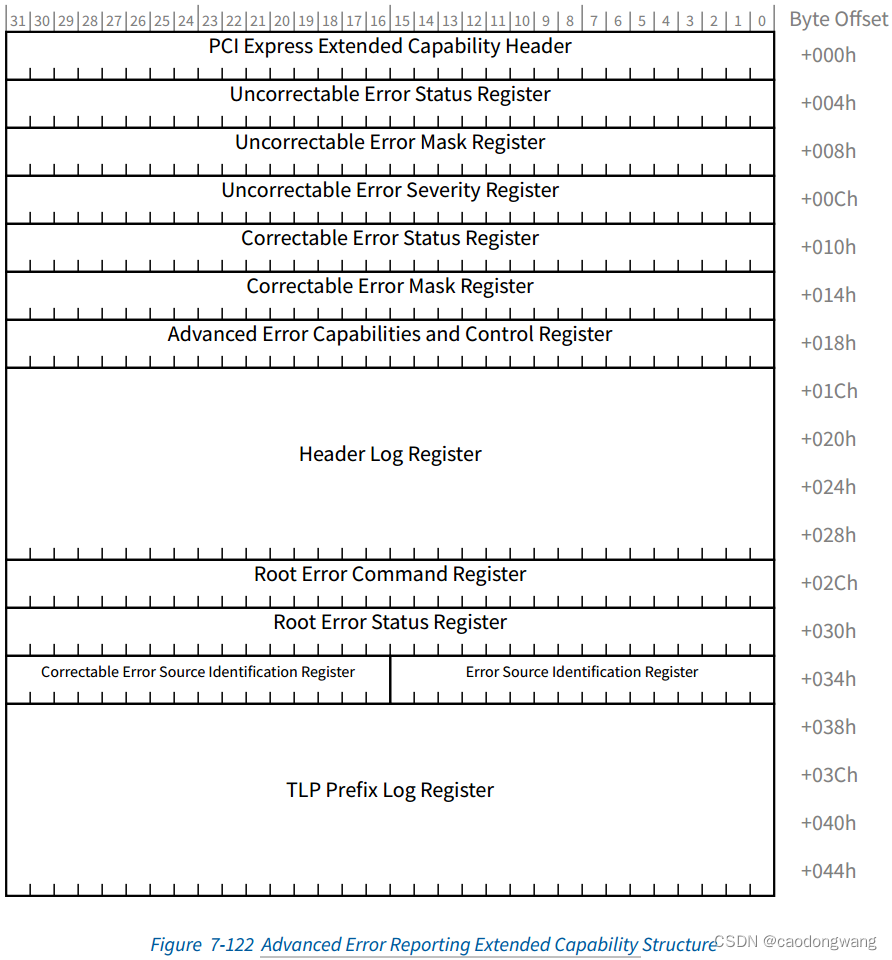

AER相关寄存器

当Uncorrectable Error Status Register寄存器对应Bit为1时,Uncorrectable Error Severity Register寄存器对应Bit为1表示ERR_FATAL,为0表示ERR_NONFATAL。

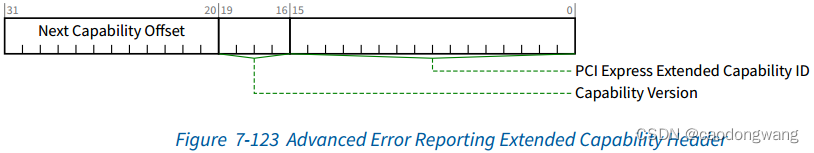

Advanced Error Reporting Extended Capability Header (Offset 00h)

| Bit Location | Register Description |

|---|---|

| 15:0 | PCI Express Extended Capability ID,PCIe扩展Cap的ID,对于AER功能,其ID为0x0001. |

| 19:16 | Capability Version,对于支持End-End TLP Prefix的设备,这个必须为2,其他设备可填1或2. |

| 31:20 | Next Capability Offset,下一个Cap的偏移地址。 |

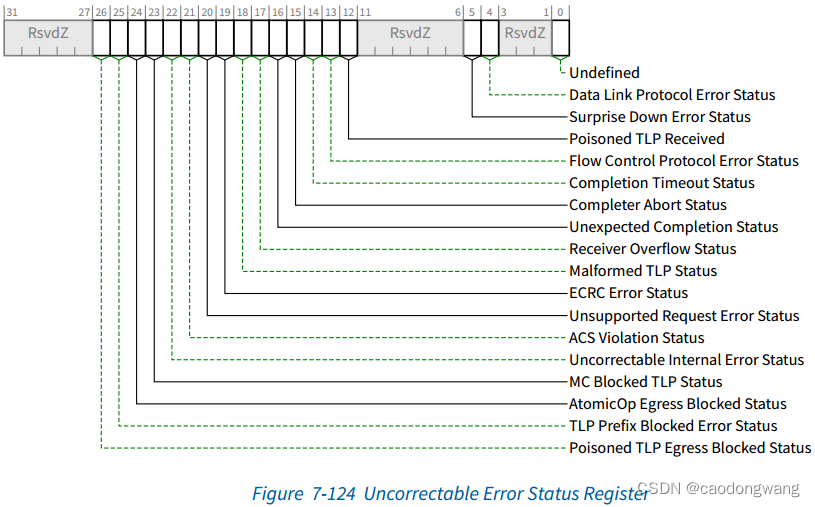

Uncorrectable Error Status Register (Offset 04h)

不可纠正错误状态寄存器表示PCI Express设备上单个错误的错误检测状态。该寄存器不同Bit置1表示检测到特定错误,软件可以通过向相应的位写入1b来清除错误状态,寄存器含义如下:

[0] Undefined

Undefined-从该位读取的值是未定义的。

[3:1] Reserve

[4] Data Link Protocol Error Status

可能原因:发送端数据链路层收到了预期之外的ACK或NAK。

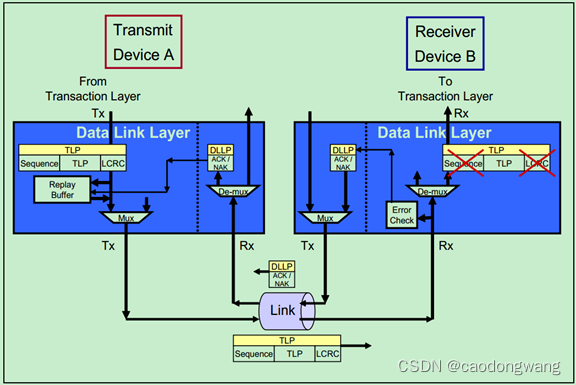

数据链路层在发送TLP之前,发送端会将TLP封装,加上Sequence前缀和LCRC后缀,用于保障数据链路层两端报文完整性,如下图所示。

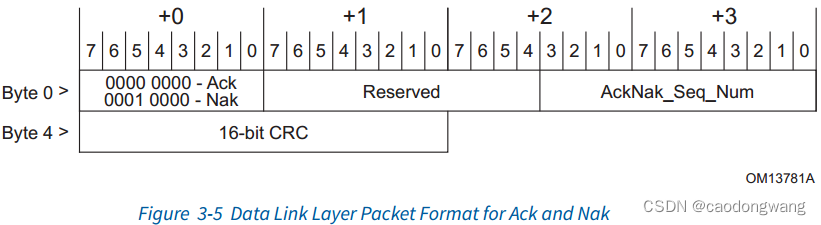

假设上电协商之后发送端只发送了Sequence=1的一个报文,那么发送端就预期接收Sequence=1的ACK或NAK。接收端接收到这个报文之后,应该回复一个ACK或NAK报文(假设不聚合),这个回复的报文中Sequence也必须为1。ACK/NAK的报文格式如下。

当接收端接收到的ACK或NCK的Sequence不等于1,那么将产生Data Link Protocol Error,如果Data Link Protocol Error Status位对应的mask不为1,则将Data Link Protocol Error Status位置1,并上报错误。

数据链路层更详细的交互流程可参考网址或查看PCIe体系结构导读第7.2章节。

[5] Surprise Down Error Status (Optional)

该状态为可选,如果硬件不支持,则应硬连接至0。

由link up状态在L0期间突然被置位,表示物理链路层意外断开。这个功能一般是桥设备支持的功能,也就是说,桥下面的EP意外链路断开时,桥设备可以将该Bit置1,并上报给系统软件。设备未插好、暴力热插拔都可能产生该错误。

当桥设备Slot Capabilities Register的Hot-Plug Surprise bit置1时(表示支持热插拔),桥设备将不会上报这个错误。

[11:6] Reserve

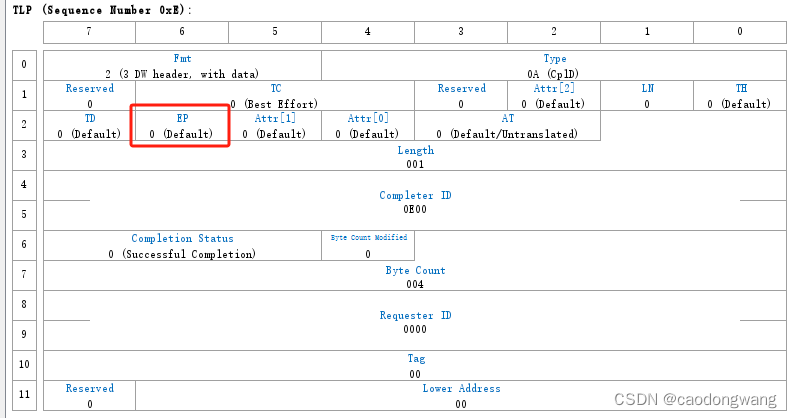

[12] Poisoned TLP Received Status

在TLP报文中,有一个EP Bit表示这个报文是否为Poisoned TLP,当该Bit为1时,表示这个报文携带的Date已经不可靠,注意,这个EP只是表征报文携带的数据不可靠了,与报文的Header无关。

当设备收到一个Poisoned TLP时,需要上报Poisoned TLP Received error。注意,部分主机的RC接收到Poisoned TLP报文会重启。

[13] Flow Control Protocol Error Status (Optional)

接收端一段时间未收到更新Credit的报文或更新Credit超过限制。

[14] Completion Timeout Status

一个经常碰到的错误。请求端发出的Non-post请求(cfg read与memory read)在规定时间内未收到完成报文。可通过修改请求端的Device Capabilities

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4837

4837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?