一、前言

1.LVDS输出接口概述

液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

2.LVDS接口电路的组成

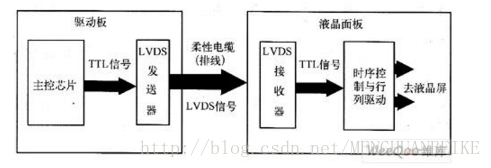

在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图

3.LVDS输出接口电路类型

与TTL输出接口相同,LVDS输出接口也分为以下四种类型:

(l)单路6位LVDS输出接口

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bit LVDS接口。此,也称18位或18bit LVDS接口。

(2)双路6位LVDS输出接口

这种接口电路中,采用双路方式传输,每个基色信号采用6位数据,其中奇路数据为18位,偶路数据为18位,共36位RGB数据,因此,也称36位或36bit LVDS接口。

(3)单路8位1TL输出接口

这种接口电路中,采用单路方式传输,每个基色信号采用8位数据,共24位RGB数据,因此,也称24位或24bit LVDS接口。

(4)双路8位1TL输出位接口

这种接口电路中,采用双路方式传输,每个基色信号采用8位数据,其中奇路数据为24位,偶路数据为24位,共48位RGB数据,因此,也称48位或48bit LVDS接口

4. LVDS发送芯片输出信号的格式

LVDS发送芯片输出信号的格式,即LVDS发送芯片输入的RGB数据,以及行同步信号HS、场同步信号VS、有效显示数据使能信号DE在各个输出通道中数据位的排列顺序。

由于几个大的LYDS芯片生产厂家制定了不同的标准,因此,存在着几种不同的LVDS发送芯片数据输出格式,在更换液晶显示器驱动板或更换液晶面板时,必须弄清LVDS接口液晶面板所要求的LVDS信号格式,使液晶显示器驱动板侧LVDS发送芯片的输出数据格式与液晶面板LVDS接收芯片所要求的数据格式相同。

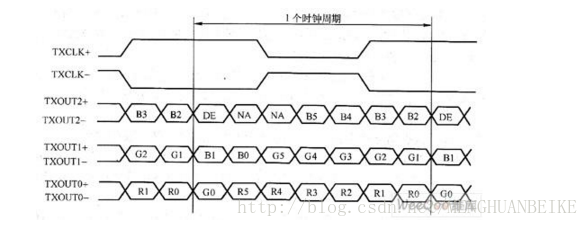

①单路6bit LVDS发送芯片数据输出格式:单路6bit LVDS发送电路使用四通道LVDS发送芯片,输出信号格式如图6所示。

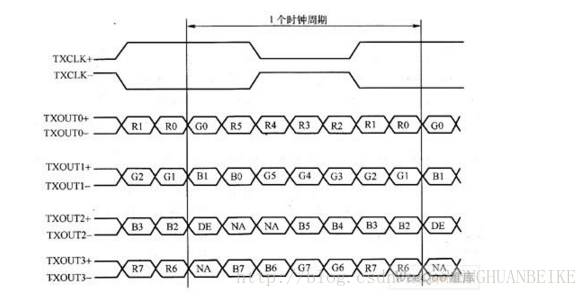

②单路8bit LVDS发送芯片数据输出格式:单路8bit LVDS发送电路使用五通道LVDS发送芯片,输出信号格式有多种,下面只介绍其中的两种。图8所示是其中的一种输出信号格式。图9所示是产生这种数据信号格式的电路接法。

二、LCD数据手册的解释

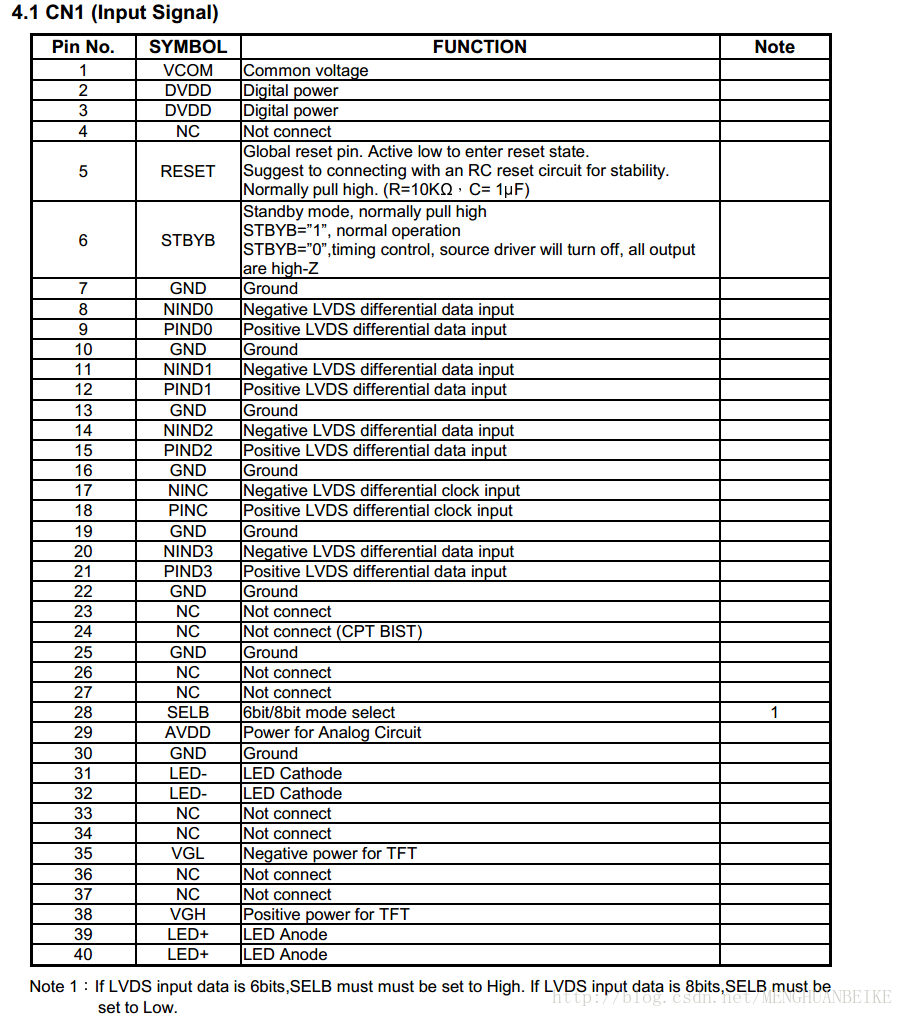

1.引脚图说明

1. “RESET”引脚用于控制LCD的启动。

2. “STBYB”引脚控制LCD的待机模式,正常情况是高电平,待机的时候低电平。

3. “NINDO”引脚是LVDS的信号传输线TXOUT0-。

4. “PINDO”引脚是LVDS的信号传输线TXOUT0+。

5. “NIND1”引脚是LVDS的信号传输线TXOUT1-。

6. “PIND1”引脚是LVDS的信号传输线TXOUT1+。

7. “NIND2”引脚是LVDS的信号传输线TXOUT2-。

8. “PIND2”引脚是LVDS的信号传输线TXOUT2+。

9. “NIND3”引脚是LVDS的信号传输线TXOUT3-。

10. “PIND3”引脚是LVDS的信号传输线TXOUT3+。

11. “SELB” 引脚是用于选择8bit/6bit模式。

12. “LED-”和“LED+”引脚是背光灯电源输入。

2.时序图说明

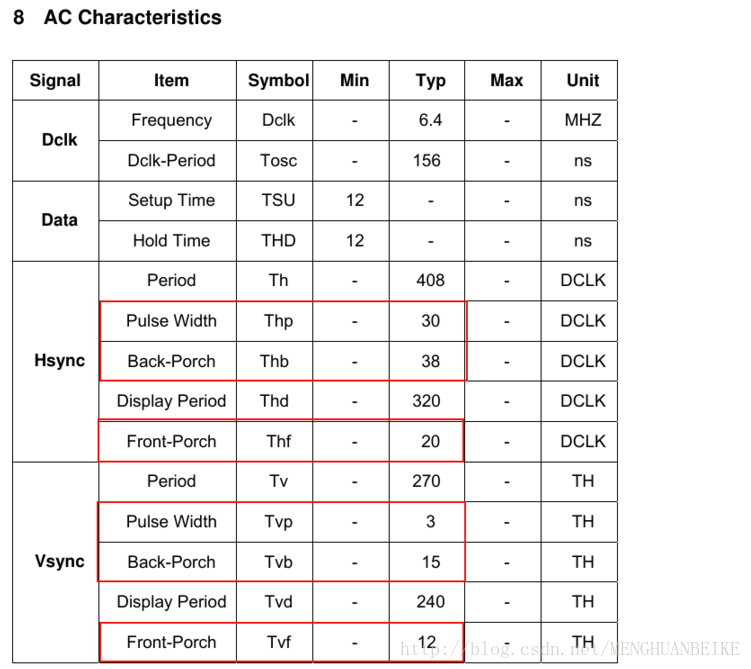

时序图这里就有点让人费解了,其他LCD都多了很多参数:

(1)、上面时序图上各时钟延时参数的含义如下:这些配置可以在LCD规格书中查取

VBPD(vertical back porch):表示在一帧图像开始时,垂直同步信号以后的无效的行数

VFBD(vertical front porch):表示在一帧图像结束后,垂直同步信号以前的无效的行数VSPW(vertical sync pulse width):表示垂直同步脉冲的宽度,用行数计算

HBPD(horizontal back porch):表示从水平同步信号开始到一行的有效数据开始之间的VCLK的个数HFPD(horizontal front porth):表示一行的有效数据结束到下一个水平同步信号开始之间的VCLK的个数

HSPW(horizontal sync pulse width):表示水平同步信号的宽度,用VCLK计算

(2)、帧的传输过程

VSYNC信号有效时,表示一帧数据的开始, 信号宽度为(VSPW +1)个HSYNC信号周期,即(VSPW +1)个无效行;

VSYNC信号脉冲之后,总共还要经过(VBPD+ 1)个HSYNC信号周期,有效的行数据才出现; 所以,在VSYNC信号有效之后,还要经过(VSPW +1 + VBPD + 1)个无效的行;

随即发出(LINEVAL + 1)行的有效数据;

最后是(VFPD + 1)个无效的行;

(3)、行中像素数据的传输过程

HSYNC信号有效时,表示一行数据的开始,信号宽度为(HSPW+ 1)个VCLK信号周期,即(HSPW +1)个无效像素;

HSYNC信号脉冲之后,还要经过(HBPD +1)个VCLK信号周期,有效的像素数据才出现;

随后发出(HOZVAL+ 1)个像素的有效数据;

最后是(HFPD +1)个无效的像素;

(4)、将VSYNC、HSYNC、VCLK等信号的时间参数设置好之后,并将帧内存的地址告诉LCD控制器,它即可自动地发起DMA传输从帧内存中得到图像数据,最终在上述信号的控制下出现在数据总线VD[23:0]上。用户只需要把要显示的图像数据写入帧内存中。

而我手上的时序图是如下图所示:

少了很多参数,我开始还以为VBPD,VFBD,HBPD,HSPW这些参数是从数据手册里面推导出来的,后来看到其他LCD手册里面标明这些参数的值,才知道这些参数可能是只适用于RGB屏幕,LVDS屏幕不需要这类参数。为了验证这个问题,我参数修改LCD的内核驱动(drivers/video/samsung/s3cfb_wa101s.c):

.timing = {

.h_fp = 100,//30,

.h_bp = 100,//30,

.h_sw = 100,//9, //100

.v_fp = 100,//10,

.v_fpe = 100,//0,

.v_bp = 100,//6,

.v_bpe = 100,//0,

.v_sw = 100,//7,

},修改后重新烧录内核,发现屏幕显示依然正常,那这就验证了这些时序参数对于LVDS屏幕是无效的。

6748

6748

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?