一 exynos 4412 时钟模块介绍

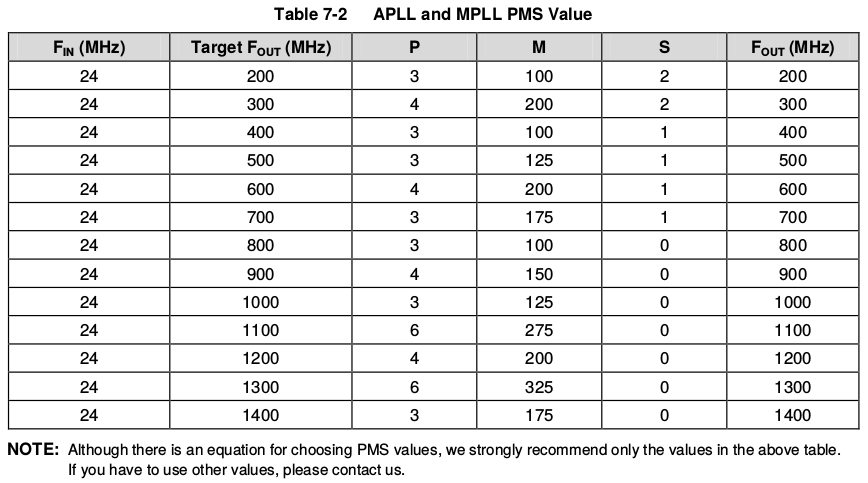

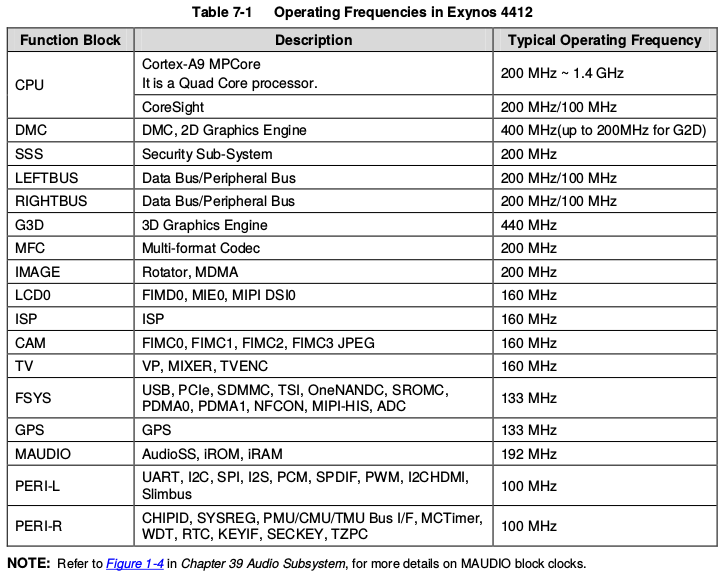

各个模块的时钟如下图所示

关于各个模块的介绍见下表

1.1 顶层时钟

由

- clocks from clock pads

XRTCXTI, XXTI, and XUSBXTI - clocks from CMUs

ARMCLK, ACLK, HCLK, and SCLK - clocks from USB phy

- clocks from HDMI_PHY

- clocks from GPIO pads

五部分构成

1.2 clocks from clock pads

由三部分构成

- XRTCXTI

输入源为32.768 KHz晶振,RTC的时钟源。 - XXTI

输入源为12MHz~50MHz晶振

没有USB Phy的话, CMU,PLL时钟源都从这里供。 - XUSBXTI

建议24MHz晶振,提供USB Phy时钟和iROM时钟源,以及PLL时钟源。

1.3 Clocks from CMU

CMUs产生内部时钟,这些内部时钟的源来自

- Clock pads, namely, XRTCXTI, XXTI, and XUSBXTI

- Four PLLs, namely, APLL, MPLL, EPLL, and VPLL

- USB PHY and HDMI PHY

手册建议用24MHz的时钟作为APLL,MPLL,EPLL和VPLL的输入源。

APLL,MPLL,EPLL和VPLL都产生22~1400MHz的时钟,其中EPLL产生192MHz的时钟提供给音频子系统。

VPLL产生54MHz时钟给G3D。

USB Device PHY 使用XUSBXTI 产生 30 and 48 MHz 的时钟。

HDMI PHY 使用 XUSBXTI 产生 54 MHz 的时钟。

1.4 典型应用配置:

- A9 MPCore,CoreSight,HPM使用APLL

- DRAM, system bus clocks,其他外设例如audio IPs和SPI使用MPLL和EPLL

- Video时钟使用VPLL

- G3D使用MPLL或VPLL作为输入时钟源

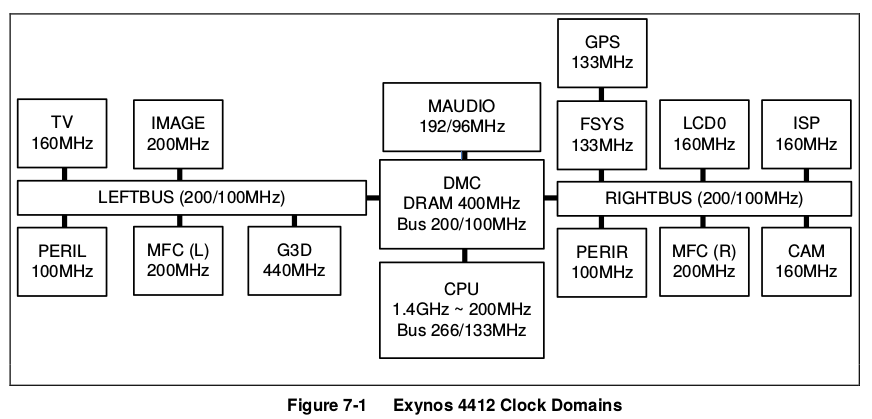

PLL分频计算公式

常用PLL分频配置如下表所示

1.5 命名规则

FINpll

: pll的输入时钟

FOUTpll

: pll的输出时钟

MOUTxpll

: xpll经过mux的输出时钟

SCLKxpll

: pad上的xpll时钟,可能经过了dividor,也可能就是

MOUTxpll

,譬如

MUX_MPLL

的输出,刚看的时候可能会疑惑。

DOUTxxx

: dividor的输出时钟

二 UART时钟配置

2.1 GPIO MUX配置

/* set GPIO to enable UART */

@ GPIO setting for UART0/1

ldr r0, =0x11400000

ldr r1, =0x22222222

str r1, [r0]

@ GPIO setting for UART2/3

ldr r0, =0x11400020

ldr r1, =0x222222

str r1, [r0]2.2 时钟源

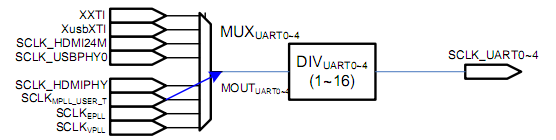

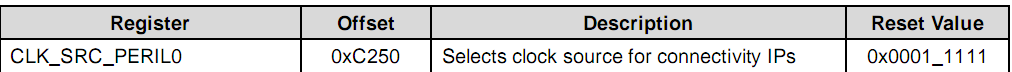

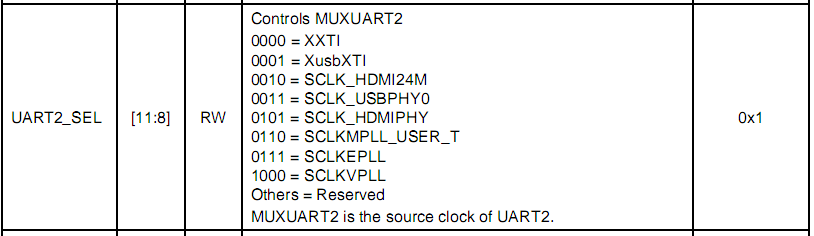

这里通过设置[11:8] = 0x0110选择 SCLKMPLL_USER_T 作为UART2的时钟源。

ldr r0, =CMU_BASE @0x1003_0000

ldr r1, =CLK_SRC_PERIL0_VAL @0x666666

ldr r2, =CLK_SRC_PERIL0_OFFSET

str r1, [r0, r2]

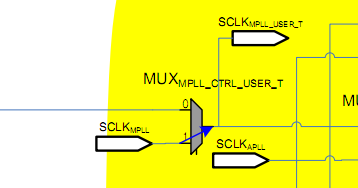

SCLKMPLL_USER_T

来自SCLKMPLL,此时,前面MUX=1,为0则是bypass了MPLL,如下图所示

MUXMPLL_SEL_T

在

CLK_SRC_TOP1

中设置

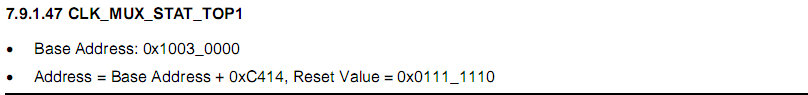

在

CLK_MUX_STAT_TOP1

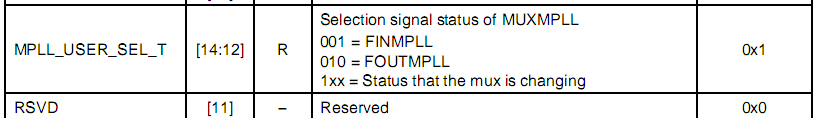

中检测状态,如下图所示

对应比特位为[14:12]

ldr r2, =CLK_MUX_STAT_TOP1_OFFSET

ldr r3, =0x01122110

bl wait_mux_state此处为2,所以

SCLKMPLL_USERT=FOUTMPLL

MPLL的配置见补充,最终MPLL输出时钟频率为800MHz。

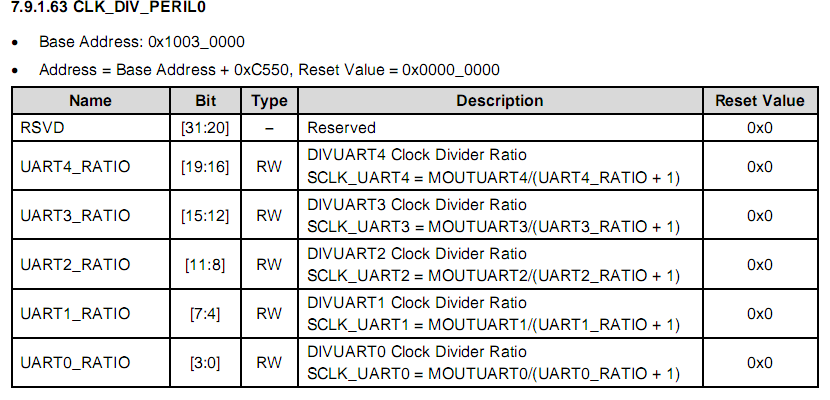

2.3 分频比

这里dividor设置为7

ldr r1, =CLK_DIV_PERIL0_VAL @0x777777

ldr r2, =CLK_DIV_PERIL0_OFFSET

str r1, [r0, r2]所以UART时钟频率为100MHz。

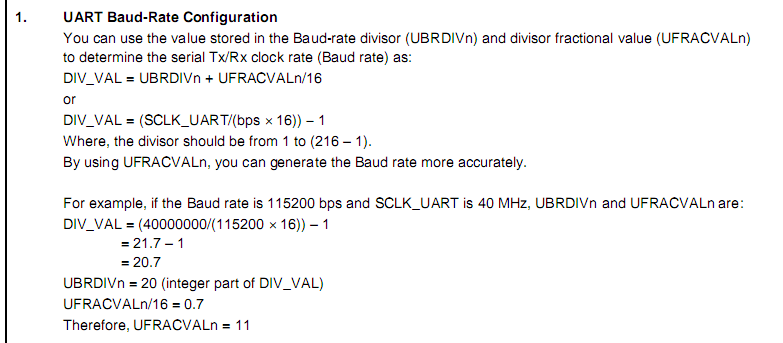

2.4 波特率和时钟频率的关系

其中SCLK_UART = 100MHz,根据波特率为115200,计算UBRDIVn和UFRACVALn

计算结果如下:

#define UART_UBRDIV_VAL 0x35

#define UART_UDIVSLOT_VAL 0x3按照这个设置,成功在minicom打印出了’OK’

2.5 补充:

MPLL配置为800MHz

/* 24MHz */

#define MPLL_MDIV 0x64

#define MPLL_PDIV 0x3

#define MPLL_SDIV 0x0

/* UART */

#define SCLK_UART MPLL_DEC/ (UART1_RATIO+1)

#define UART_UBRDIV_VAL 0x35

#define UART_UDIVSLOT_VAL 0x3

/* check MPLL and if MPLL is not 400 Mhz skip MPLL resetting for C2C operation */

ldr r2, =MPLL_CON0_OFFSET

ldr r1, [r0, r2]

ldr r3, =0xA0640301

cmp r1, r3

bne skip_mpll

@ Set MPLL

ldr r1, =MPLL_CON1_VAL

ldr r2, =MPLL_CON1_OFFSET

str r1, [r0, r2]

ldr r1, =MPLL_CON0_VAL

ldr r2, =MPLL_CON0_OFFSET

str r1, [r0, r2]

skip_mpll:

480

480

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?