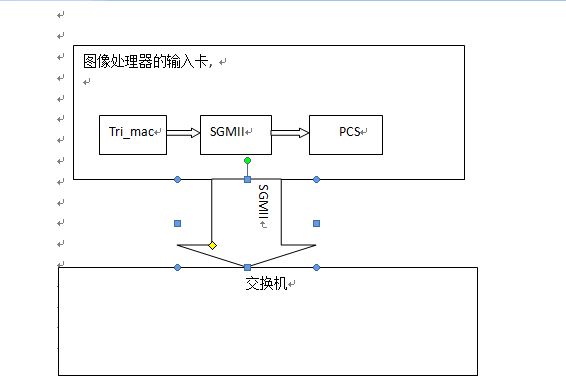

最近调试lattice 的sgmii接口。 项目最初的架构大概是这样的,用于调试。

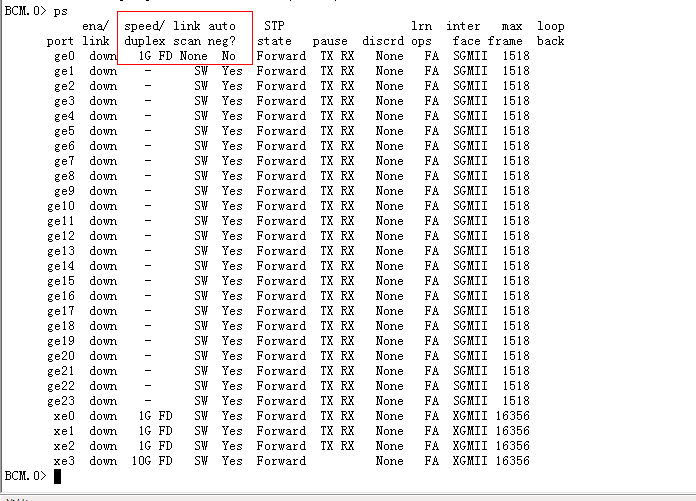

FPGA这边的架构,就是 Tri_mac 转为 sgmii,然后再通过pcs出去。其实sgmii核自带了一个pcs核,最坑人的是PCS必须是外部时钟,最后没有办法只能自己生成一个pcs核和sgmii核对接起来。由于MDIO,我们这边没有去使用。使用的是强制输出。我调试了两天才发现可能是交换机这边设置可能有问题,这边使用的 BCM56634,一开始也不熟悉,最后去请教了别人才把自动连接把它关了。然后ok了。我把交换机芯片这边的配置如下:

最后附上我serdes这边的代码;

`timescale 1ns/100ps

module top_hb (

// G/MII Interface

data_in_mii,

en_in_mii,

err_in_mii,

data_out_mii,

dv_out_mii,

err_out_mii,

col_out_mii,

crs_out_mii,

// GB Timing References

in_clk_125,

in_ce_sink,

in_ce_source,

out_clk_125,

out_ce_sink,

out_ce_source,

// SERIAL GMII Interface

refclkp,

refclkn,

hdinp0,

hdinn0,

hdoutp0,

hdoutn0,

// Control Interface

gbe_mode,

sgmii_mode,

rst_n,

// Host Bus

hclk,

hcs_n,

hwrite_n,

haddr,

hdatain,

hdataout,

hready_n,

//Debug Port

debug_link_timer_short,

mr_an_complete

);

// I/O Declarations

input rst_n; // System Reset, Active Low

input hclk;

input gbe_mode ; // GBE Mode (0=SGMII 1=GBE)

input sgmii_mode ; // SGMII PCS Mode (0=MAC 1=PHY)

input in_clk_125 ; // GMII Input Data Path clock 125Mhz

input in_ce_sink ;

output in_ce_source ;

input [7:0] data_in_mii; // G/MII Incoming Data

input en_in_mii; // G/MII Incoming Data Valid

input err_in_mii; // G/MII Incoming Error

input out_clk_125 ; // GMII Output Data Path clock 1

本文记录了在调试Lattice FPGA中SGMII接口遇到的问题与解决过程,包括如何处理SGMII与PCS核对接、外部时钟问题以及BCM56634交换机的配置调整。

本文记录了在调试Lattice FPGA中SGMII接口遇到的问题与解决过程,包括如何处理SGMII与PCS核对接、外部时钟问题以及BCM56634交换机的配置调整。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1518

1518

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?