时钟产生-PLL

PLL(锁相环)合成器是一种更为复杂的系统时钟源,通用PLL合成器需要一个外部晶体并包含一个能够对晶体的特定频率加倍或分频的集成锁相环(PLL)电路

S3C2440存在两个锁相环(PLL):MPLL和UPLL,UPLL专用于USB设备。

MPLL会产生三个部分的时钟频率FCLK,HCLK,PCLK

FCLK用于cpu核

HCLK用于AHB(高速外部的总线比如sdram)

PCLK用于PHB(低速的外设总线比如UART)

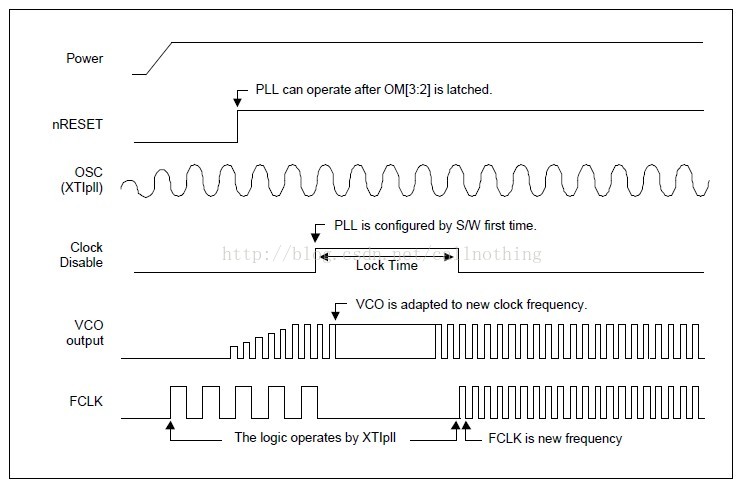

通过上面时序图发现刚上电时FCLK就是外部晶振频率,12MHZ,但是运行一段时间后,通过程序改变其频率设置,但是会有一个锁定时间Lock Time,这个时间也是可以调节的,过来这个时间后FCLK才变成用户想要的频率

设置S3C2440的时钟频率的3几个寄存器

1.LOCKTIME寄存器

2.MPLLCON寄存器

3.CLKDIVN寄存器

LOCKTIM寄存器

就是前面的locktime

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

700

700

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?