组理学习笔记之寄存器

存储器的基本:

-

基本操作 读写

-

数据存放 为读出和写入的数据设置"数据缓冲寄存器"MDR

-

操作控制 读、写 控制线路(R/W控制)

-

-

基本结构

-

存储体(由存储单元构成)

-

地址寄存器

-

地址译码器

-

数据缓冲寄存器

-

读写控制线路

-

-

存储介质分类

存储介质 | 存取方式 | 存储作用 |

半导体存储(ROM,RAM) | 随机存取 | 主存储器 |

磁性存储器 | 串行存取 | 辅助存储器 |

光存储器 | 告诉缓冲存储器 |

-

存储器

-

主存储器

-

RAM

-

SRAM 静态

-

DRAM 动态

-

-

ROM

-

MROM(掩膜ROM)

-

PROM(一次可编程ROM)

-

EPROM(多次可编程)

-

FLASH Memory 闪速存储器

-

-

-

高速缓冲存储器 (Cache)

-

辅助存储器 (磁盘、磁带、光盘)

-

-

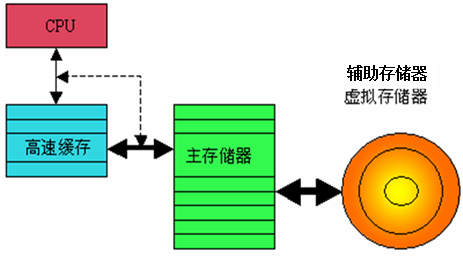

三级存储系统

-

由高速缓冲存储器、主存储器、辅助存储器组成三级结构的存储器,由系统统一调度、统一管理。

-

名称 | 简称 | 用途 | 特点 |

高速缓冲存储器 | Cache | 高速存取正在执行的指令和数据(半导体存储器) | 存取速度快, 但存储容量小。 |

主存储器 | 主存 /内存 | 存取正在执行的指令和数据(半导体存储器) | 存取速度较快, 存储容量较大。 |

辅助存储器 | 辅存 (硬盘) | 持久存取所有程序和大型数据(磁性光敏) | 存取速度慢, 存储容量大。 |

-

高速缓冲分两种

-

一种在CPU内部, CPU通过内部总线访问,比较贵,效率高 (一级CACHE)

-

一种在CPU外,主板上(二级CACHE) CPU通过存储总线访问

-

现在CPU有三级缓存机制

-

-

-

三级存储系统可以实现的前提: 程序运行时的局部性。

-

时间局部性:在一小段时间内,最近被访问过的程序和数据很可能再次被访问。

-

空间局部性:在空间上,这些被频繁访问的程序和数据往往集中在一小片存储区。

-

访问顺序局部性:在访问顺序上,指令顺序执行比转移执行的可能性大(约5:1)

-

-

三级存储系统所遵循的规则

-

内层数据(靠近CPU)一定被包含在其外层的存储器中,即是外层的复制品

-

复制之间及与原数据之间数据必须保持一致

-

-

主存储器组成

-

存储体(存储芯片):存储单元的集合,通常用X地址线和Y地址线交叉点

-

选择所需的存储单元。

-

地址译码器:将地址信号转换成输出端的存储单元选择信号,

用来驱动相应的读写电路,访问选中的存储单元。

-

驱动器: 双译码结构中,在译码器输出后加驱动器,驱动挂在各条X方向

选择线上的所有存储元电路。

-

I/O电路:在数据总线和被选存储单元之间,控制被选中的存储单元读出

或写入,并放大数据信号。

-

片选信号/CS: 在选择地址时,首先要选片,只有当片选信号有效时,

该存储芯片才有效。

-

输出驱动电路:为了扩展存储器的容量,常需要将几个芯片的数据线并联

使用;另外,存储器的读出数据或写入数据都放在双向的数

据总线上,这就用到三态输出缓冲器。

一道题

例:某RAM芯片,其存储容量为16K*8位,问:

(1)该芯片引出线的最小数目应为多少(不考虑电源线、接地线)?

(2)存储器芯片的地址范围是什么?

答案:

(1)16K = 214,所以地址线14根,存储字长8位,所以数据线8根,

加上芯片的片选信号线1、读写控制信号线1、

该芯片引出线最少: 14+8+1+1=24 条。

(2)存储器芯片的地址范围

0000H ~ 3FFFH

给定的数字中,只是看:"16K",就能看出地址信息.

16K = 16 * 1024 = 2^4 * 2^10 = 2^14

所以,写出这16K的地址,需要 14 位二进制数.

一般,用16位数,那么,前面再加上两个0.

0000 0000 0000 0000 假设这是起始地址

0000 0000 0000 0001 这就第二个单元的地址

……

0011 1111 1111 1111 这最后单元的地址

把上述数字,写成16进制,就是0000H---3FFFH.

3732

3732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?