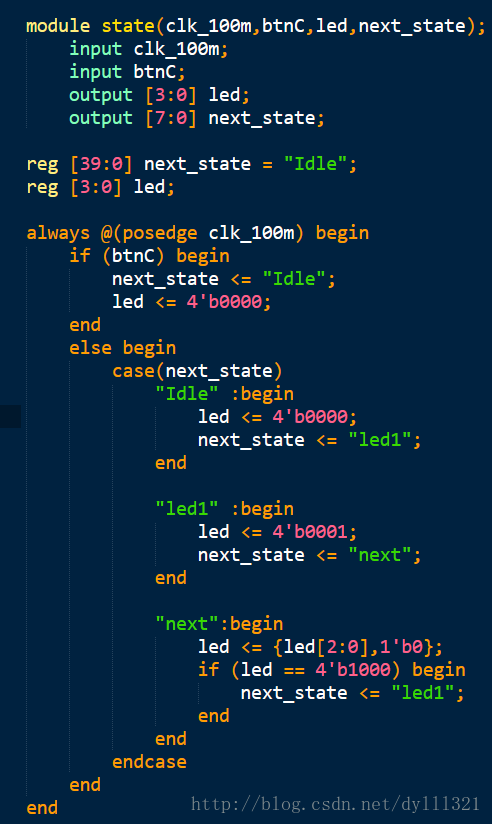

一种新的状态机写法。用“字符串”替代4'd0,4'd1等等。但要注意,reg [39:0] next_state 只能有五个字符(5*8=40),比较耗费寄存器资源。

状态机源代码:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2017/03/23 20:33:42

// Design Name:

// Module Name: state

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module state(clk_100m,btnC,led,next_state);

input clk_100m;

input btnC;

output [3:0] led;

output [7:0] next_state;

reg [39:0] next_state = "Idle";

reg [3:0] led;

always @(posedge clk_100m) begin

if (btnC) begin

next_state <= "Idle";

led <= 4'b0000;

end

else begin

case(next_state)

"Idle" :begin

led <= 4'b0000;

next_state <= "led1";

end

"led1" :begin

led <= 4'b0001;

next_state <= "next";

end

"next":begin

led <= {led[2:0],1'b0};

if (led == 4'b1000) begin

next_state <= "led1";

end

end

endcase

end

end

/*

reg [7:0] next_state = 8'd0;

reg [3:0] led;

always @(posedge clk_100m) begin

if (btnC) begin

next_state <= 8'd0;

led <= 4'b0000;

end

else begin

case(next_state)

8'd0 :begin

led <= 4'b0000;

next_state <= 8'd1;

end

8'd1 :begin

led <= 4'b0001;

next_state <= 8'd2;

end

8'd2 :begin

led <= {led[2:0],1'b0};

if (led == 4'b1000) begin

next_state <= 8'd1;

end

end

endcase

end

end

*/

endmodule

仿真代码:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2017/03/23 20:52:29

// Design Name:

// Module Name: sim

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module sim();

//input

reg clk;

reg reset;

//output

wire [3:0] LED;

wire [39:0] State;

state u1(

.clk_100m(clk),

.btnC(reset),

.led(LED),

.next_state(State)

);

//initial

initial begin

clk = 0;

reset = 1;

#10 clk = !clk;

#10 clk = !clk;

#10 clk = !clk;

reset = 0;

forever #10 clk = !clk;

end

endmodule

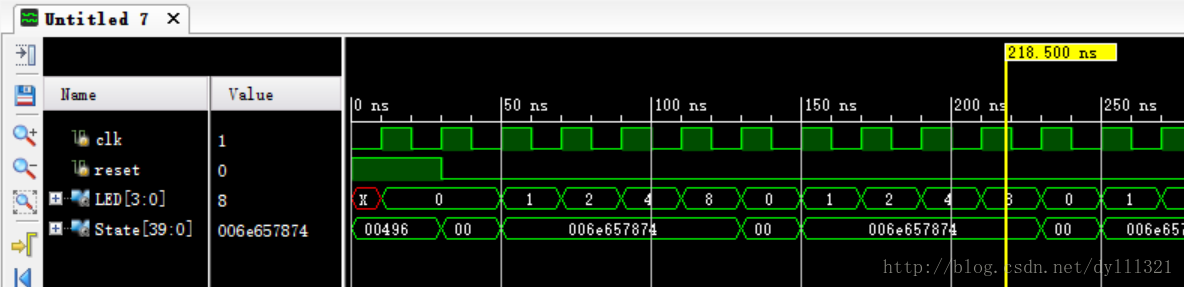

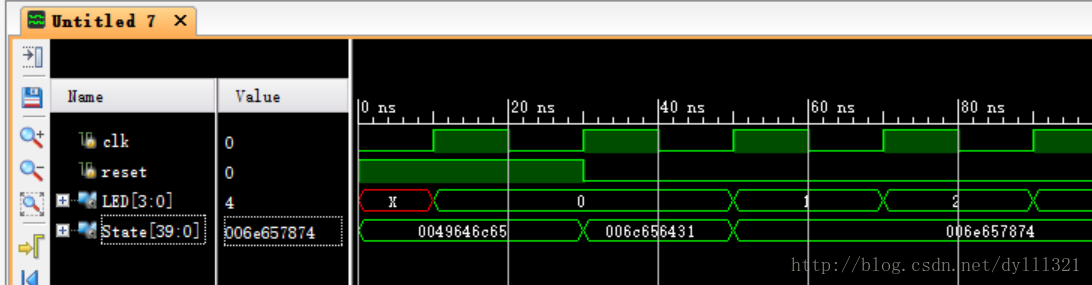

测试:

2083

2083

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?