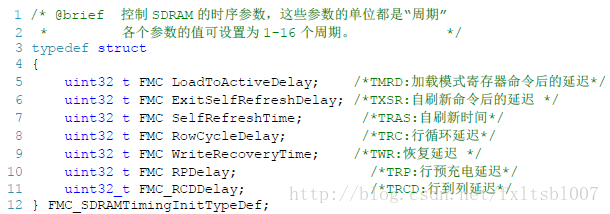

这个结构体里还有几个延时没说到,现在来看一下。

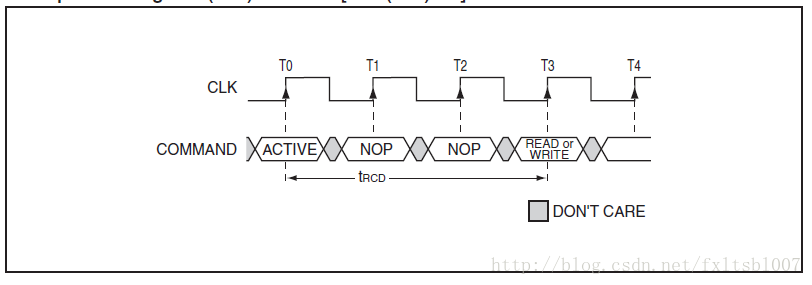

1、TRCD 行到列延迟

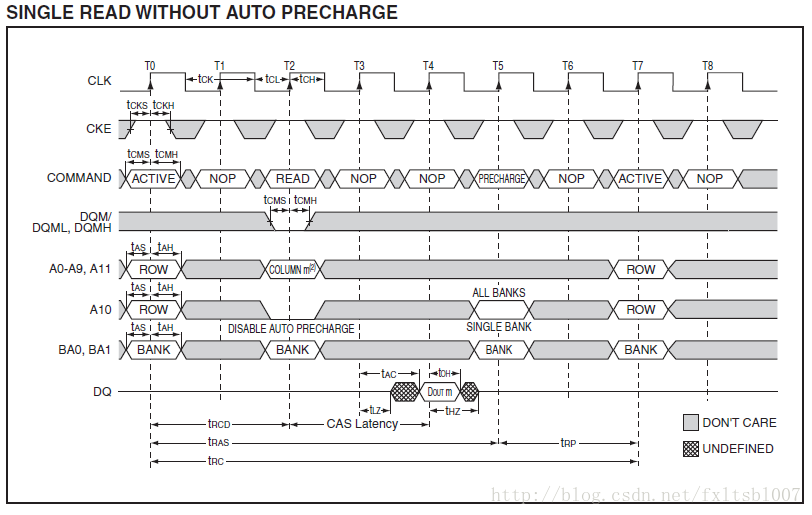

在发送列读写命令时,必须要与行有效命令有一个间隔,这个间隔被定义为TRCD,即RAS to CAS delay,也可以理解为行选通周期,这应该是根据芯片存储阵列电子元件响应时间(从一种状态到另一种状态变化的过程)所制定的延迟。TRCD是SDRAM的一个重要的时序参数。通过查询数据手册可知,tRCD为15ns。

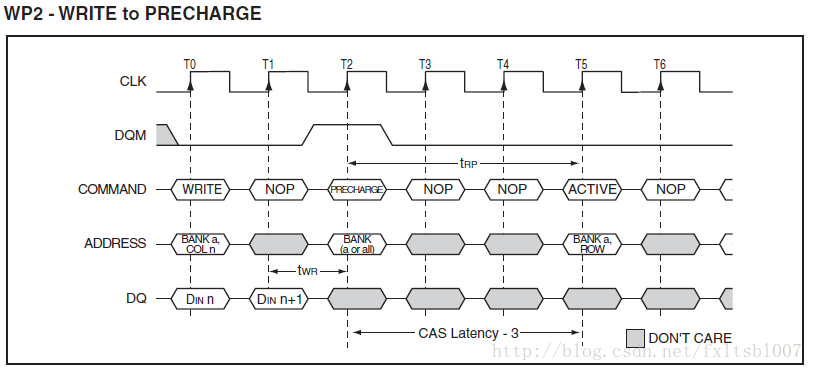

2、tWR 注释写的恢复时间,其实这个应该是写入/校正时间。

为了保证数据的可靠写入,都会留出足够的写入/校正时间,这个操作也被称作

写回(write back),tWR至少占用一个时钟周期或再多一点(时钟频率越高,tWR

占用周期越多)

3、tRAS 自动刷新时间

先来看下《终极内存技术指南》对它的解释:行有效至预充电命令间隔周期。它有一个范围,一般是预充电命令至少要在行有效命令5个时钟周期之后发出,最长间隔视芯片而异(基本在120000ns左右),否则工作行的数据将有丢失的危险。这也意味着一个工作行从选通开始,可以有120000ns的持续工作时间而不用预充电。显然,只要芯片不发出预充电的命令,行打开的状态就会一直保持。在此期间的对该行的任何读写操作也就不会有tRCD的延迟。

4、tXSR 自刷新命令后的延迟,ExitSelf-refresh delay,即退出自我刷新命令后要等待的时间,过了这段时间才可以发送行有效命令。查询手册,这个值在60到70ns之间。

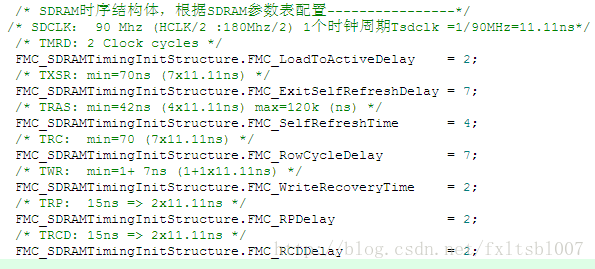

到这里关于时序的几个重要参数就搞清楚了。照着数据手册,就可以完成结构体的初始化。

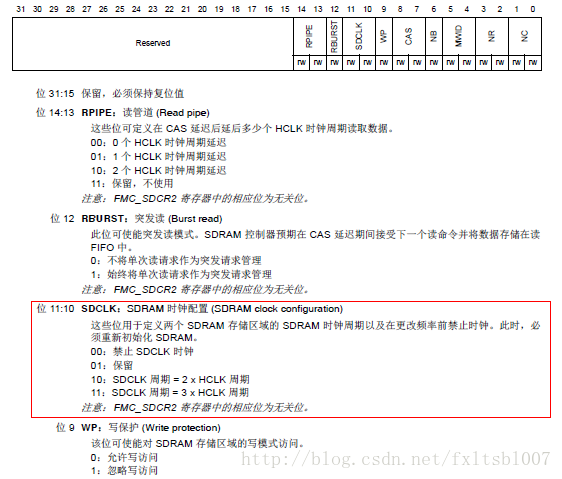

到了这里有一个疑问。为什么SDCLK的时钟是90MHz呢?

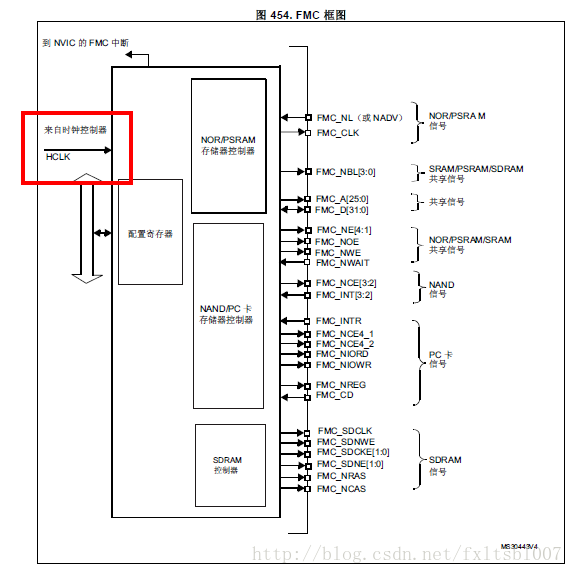

查阅资料可知,FMC外设挂载在AHB3总线上,时钟信号来源于HCLK,SDRAM控制器里面有寄存器来控制SDCLK的分频。如下图,HCLK时钟进入后,再由配置寄存器里的寄存器来控制分频。

PS1:AHB时钟总线的作用:

1.AHB1总线,频率可达180MHz。主要用于连接外设包括GPIO端口,RTC单元,以及两个AHB转APB桥。其中两个APB桥还从两个DMA控制器单独开辟了总线用于DMA传输不用经过AHB1总线,这大大减少了AHB1总线的负担,很好的设计啊!

2.AHB2总线。主要用于连接RNG随机数生成器,摄像头接口和全速USB-OTG单元,因为在图像应用中摄像头接口数据量太大,单独开辟总线避免和其他设备争总线造成系统反应缓慢。则是非常明智的选择。

3.AHB3总线。只连接了FMC单元用于外扩存储器(包括ROM,SRAM和SDRAM等),独立总线可带来快速的存取响应。

PS2:AHB总线和APB总线的区别

AHB,是Advanced High performanceBus的缩写,译作高级高性能总线,这是一种“系统总线”。AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接。AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。

APB,是Advanced Peripheral Bus的缩写,这是一种外围总线。

APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像 AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?