USART功能描述

USART双向通信至少需要两个管脚:Receive Data In(RX) and Transmit Data Out(Tx)。

如果是同步模式(synchronous mode)的话,需要SCLK pin。

SCLK pin:Transmitter clock output. This pin outputs the transmitter data clock for

synchronous transmission corresponding to SPI master mode (no clock pulses on start

bit and stop bit, and a software option to send a clock pulse on the last data bit). In

parallel data can be received synchronously on RX. This can be used to control

peripherals that have shift registers (e.g. LCD drivers). The clock phase and polarity

are software programmable. In smartcard mode, SCLK can provide the clock to the

smartcard.

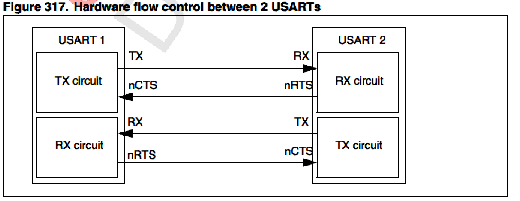

如果是Hardware flow control 模式的话还需要CTS, RTS两个pin。

nCTS: Clear To Send blocks the data transmission at the end of the current transfer

when high

nRTS: Request to send indicates that the USART is ready to receive a data (when

low).

RTS and CTS flow control can be enabled independently by writing respectively RTSE and

CTSE bits to 1 (in the USART_CR3 register).

这两个Pin要互相接,即nCTS要接到对面的nRTS上,nRTS要接到对面的nCTS上。

RTS flow control:

If the RTS flow control is enabled (RTSE=1), then nRTS is asserted (tied low) as long as the

USART receiver is ready to receive a new data. When the receive register is full, nRTS is

deasserted, indicating that the transmission is expected to stop at the end of the current

frame. Figure 318 shows an example of communication with RTS flow control enabled.

**CTS flow control:**If the CTS flow control is enabled (CTSE=1), then the transmitter checks the nCTS input

before transmitting the next frame. If nCTS is asserted (tied low), then the next data is

transmitted (assuming that a data is to be transmitted, in other words, if TXE=0), else the

transmission does not occur. When nCTS is deasserted during a transmission, the current

transmission is completed before the transmitter stops.

When CTSE=1, the CTSIF status bit is automatically set by hardware as soon as the nCTS

input toggles. It indicates when the receiver becomes ready or not ready for communication.

An interrupt is generated if the CTSIE bit in the USART_CR3 register is set. The figure

below shows an example of communication with CTS flow control enabled.

通过Rx, Tx, serial data会被传输。每个帧都会包含如下内容

(1) An Idle Line prior to transmission or reception。

(2) A start bit

(3) A data word (8 or 9 bits) least significant bit first

(4) 0.5,1, 1.5, 2 Stop bits indicating that the frame is complete

(5) This interface uses a fractional baud rate generator - with a 12-bit mantissa and 4-bit

fraction

(6) A status register (USART_SR)

(7) Data Register (USART_DR)

(8) A baud rate register (USART_BRR) - 12-bit mantissa and 4-bit fraction

(9) A Guardtime Register (USART_GTPR) in case of Smartcard mode.

USART介绍

The universal synchronous asynchronous receiver transmitter (USART) offers a flexible

means of full-duplex data exchange with external equipment requiring an industry standard

NRZ asynchronous serial data format. The U SART offers a very wide range of baud rates

using a fractional baud rate generator.

It supports synchronous one-way communication and half-duplex single wire

communication. It also supports the LIN (local interconnection network), Smartcard Protocol

and IrDA (infrared data association) SIR ENDEC specifications, and modem operations

(CTS/RTS). It allows multiprocessor communication.

High speed data communication is poossible by using the DMA for multibuffer configuration.

USART character description

Word length may be selected as being either 8 or 9 bits by programming the M bit in the

USART_CR1 register.

The TX pin is in low state during the start bit. It is in high state during the stop bit.

An Idle character is interpreted as an entire frame of “1”s followed by the start bit of the next

frame which contains data (The number of “1” ‘s will include the number of stop bits).

A Break character is interpreted on receiving “0”s for a frame period. At the end of the

break frame the transmitter inserts either 1 or 2 stop bits (logic “1” bit) to acknowledge the

start bit.

Transmission and reception are driven by a common baud rate generator, the clock for each

is generated when the enable bit is set respectively for the transmitter and receiver.

The details of each block is given below.

Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status.

When the transmit enable bit (TE) is set, the data in the transmit shift register is output on

the TX pin and the corresponding clock pulses are output on the SCLK pin.

Character transmission

During an USART transmission, data shifts out least significant bit first on the TX pin. In this

mode, the USART_DR register consists of a buffer (TDR) between the internal bus and the

transmit shift register (see Figure 296 ).

Every character is preceded by a start bit which is a logic level low for one bit period. The

character is terminated by a configurable number of stop bits.

Note: The TE bit should not be reset during transmission of data. Resetting the TE bit during the

transmission will corrupt the data on the TX pin as the baud rate counters will get frozen.

The current data being transmitted will be lost.

An idle frame will be sent a fter the TE bit is enabled.

Configurable stop bits

The number of stop bits to be transmitted with every character can be programmed in

Control register 2, bits 13,12.

● 1 stop bit: This is the default value of number of stop bits.

● 2 Stop bits: This will be supported by normal USART, single-wire and modem modes.

● 0.5 stop bit: To be used when receiving data in Smartcard mode.

● 1.5 stop bits : To be used when transmitting and receiving data in Smartcard mode.

An idle frame transmission will include the stop bits.

A break transmission will be 10 low bits followe d by the configured number of stop bits

(when m = 0) and 11 low bits followed by the configured number of stop bits (when m = 1). It

is not possible to transmit long breaks (break of length greater than 10/11 low bits).

Procedure:

1. Enable the USART by writing the UE bit in USART_CR1 register to 1.

2. Program the M bit in USART_CR1 to define the word length.

3. Program the number of stop bits in USART_CR2.

4. Select DMA enable (DMAT) in USART_CR3 if Multi buffer Communication is to take

place. Configure the DMA register as explained in multibuffer communication.

5. Select the desired baud rate using the USART_BRR register.

6. Set the TE bit in USART_CR1 to send an idle frame as first transmission.

7. Write the data to send in the USART_DR register (this clears the TXE bit). Repeat this

for each data to be transmitted in case of single buffer.

8. After writing the last data into the USART_ DR register, wait until TC=1. This indicates

that the transmission of the last frame is complete. This is required for instance when

the USART is disabled or enters the Halt mode to avoid corrupting the last

transmission.

Single byte communication

Clearing the TXE bit is always performed by a write to the data register.

The TXE bit is set by hardware and it indicates:

● The data has been moved from TDR to the shift register and the data transmission has

started.

● The TDR register is empty.

● The next data can be written in the USART_DR register without overwriting the

previous data.

This flag generates an interrupt if the TXEIE bit is set.

When a transmission is taking place, a write instruction to the USART_DR register stores

the data in the TDR register and which is copied in the shift register at the end of the current

transmission.

When no transmission is taking place, a write instruction to the USART_DR register places

the data directly in the shift register, the data transmission starts, and the TXE bit is

immediately set.

If a frame is transmitted (after the stop bit) and the TXE bit is set, the TC bit goes high. An

interrupt is generated if the TCIE bit is set in the USART_CR1 register.

After writing the last data into the USART_DR register, it is mandatory to wait for TC=1

before disabling the USART or causing the microcontroller to enter the low power mode (see

Figure 299: TC/TXE behavior when transmitting).

The TC bit is cleared by the following software sequence:

1. A read from the USART_SR register

2. A write to the USART_DR register

Note: The TC bit can also be cleared by writing a ‘0 to it. This clearing sequence is recommended

only for Multibuffer communication.

Break characters

Setting the SBK bit transmits a break character. The break frame length depends on the M

bit (see Figure 297 ).

If the SBK bit is set to ‘1 a break character is sent on the TX line after completing the current

character transmission. This bit is reset by ha rdware when the break character is completed

(during the stop bit of the break character). The USART inserts a logic 1 bit at the end of the

last break frame to guarantee the recognition of the start bit of the next frame.

Note : If the software resets the SBK bit before the commencem ent of break transmission, the

break character will not be tran smitted. For two consecutive breaks, the SBK bit should be

set after the stop bit of the previous break.

Idle characters

Setting the TE bit drives the USART to send an idle frame before the first data frame.

Receiver

The USART can receive data words of either 8 or 9 bits depending on the M bit in the

USART_CR1 register.

Start bit detection

The start bit detection sequence is the same when oversampling by 16 or by 8.

In the USART, the start bit is detected when a specific sequence of samples is recognized.

This sequence is: 1 1 1 0 X 0 X 0 X 0 0 0 0.

Character reception

During an USART reception, data shifts in least si gnificant bit first through the RX pin. In this

mode, the USART_DR register consists of a bu ffer (RDR) between the internal bus and the

received shift register.

Procedure:

1. Enable the USART by writing the UE bit in USART_CR1 register to 1.

2. Program the M bit in USART_CR1 to define the word length.

3. Program the number of stop bits in USART_CR2.

4. Select DMA enable (DMAR) in USART_CR3 if multibuffer communication is to take

place. Configure the DMA register as explained in multibuffer communication. STEP 3

5. Select the desired baud rate using the baud rate register USART_BRR

6. Set the RE bit USART_CR1. This enables the receiver which begins searching for a

start bit.

When a character is received

● The RXNE bit is set. It indicates that the content of the shift register is transferred to the

RDR. In other words, data has been received and can be read (as well as its

associated error flags).

● An interrupt is generated if the RXNEIE bit is set.

● The error flags can be set if a frame error, noise or an overrun error has been detected

during reception.

● In multibuffer, RXNE is set after every byte received and is cleared by the DMA read to

the Data Register.

● In single buffer mode, clearing the RXNE bit is performed by a software read to the

USART_DR register. The RXNE flag can also be cleared by writing a zero to it. The

RXNE bit must be cleared before the end of the reception of the next character to avoid

an overrun error.

Break character

When a break character is received, the USART handles it as a framing error.

Idle character

When an idle frame is detected, there is the same procedure as a data received character

plus an interrupt if the IDLEIE bit is set.

Overrun error

An overrun error occurs when a character is received when RXNE has not been reset. Data

can not be transferred from the shift register to the RDR register until the RXNE bit is

cleared.

The RXNE flag is set after every byte received. An overrun error occurs if RXNE flag is set

when the next data is received or the previous DMA request has not been serviced. When

an overrun error occurs:

● The ORE bit is set.

● The RDR content will not be lost. The previous data is available when a read to

USART_DR is performed.

● The shift register will be overwritten. After that point, any data received during overrun

is lost.

● An interrupt is generated if either the RXNEIE bit is set or both the EIE and DMAR bits

are set.

● The ORE bit is reset by a read to the USART_SR register followed by a USART_DR

register read operation.

Note: The ORE bit, when set, indicates that at least 1 data has been lost. There are two

possibilities:

● if RXNE=1, then the last valid data is stored in the receive register RDR and can be

read,

● if RXNE=0, then it means that the last valid data has already been read and thus there

is nothing to be read in the RDR. This case can occur when the last valid data is read in

the RDR at the same time as the new (and lost) data is received. It may also occur

when the new data is received during the reading sequence (between the USART_SR

register read access and the USART_DR read access)

1150

1150

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?