这是翻译TI官方文档《KeyStone Architecture Universal Parallel Port (uPP)》SPRUHG9有关通用并行端口uPP的内容(除寄存器部分),寄存器部分大家可以自己看,现在手头上正在做uPP与FPGA的图像数据通信。等程序调通了,会贴出部分来分享一下开发与调试经验。

转载请注明出处:http://blog.csdn.net/hw5226349/

1.1 外设的功能

通用并行端口外设(uPP)是一种专用数据线和最小的控制信号的多通道高速并行接口。设计用于每通道高达16bits数据宽度的ADCs、DACs传输,也可以用于FPAG和其他uPP外设。它可以工作在接收模式下,发射模式,或双工模式,其中,在它的各个通道操作相反的方向的传输。

1.2 功能

UPP外设提供一个高速并行数据总线的几个重要特点:

•两个独立的通道带独立的数据总线

•通道可在相同或相反的方向同时工作

•I / O速度高达75 MHz的每个通道8-16位数据宽度

•内部DMA - 离开CPU EDMA免费

•简单的协议与几个控制引脚(配置:2-4每通道)

•单和双数据速率(使用一个或时钟信号的两个边)

•双倍数据速率规定的37.5 MHz的最大时钟速度

•多种数据打包格式9-15位数据宽度

•I / O速度高达75 MHz的每个通道8-16位数据宽度

•内部DMA - 离开CPU EDMA免费

•简单的协议与几个控制引脚(配置:2-4每通道)

•单和双数据速率(使用一个或时钟信号的两个边)

•双倍数据速率规定的37.5 MHz的最大时钟速度

•多种数据打包格式9-15位数据宽度

•数据交错模式(单信道只)

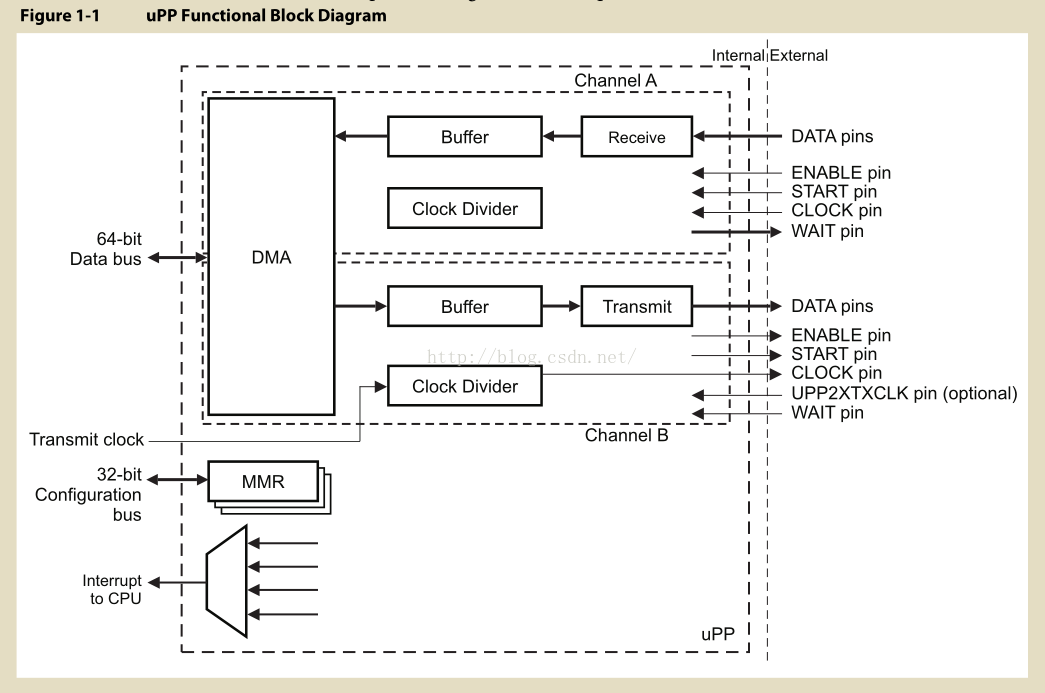

请注意,图1-1显示了一个特定的配置:通道A接收通道B传输。但是,每个信道可以操作在任何一个方向。

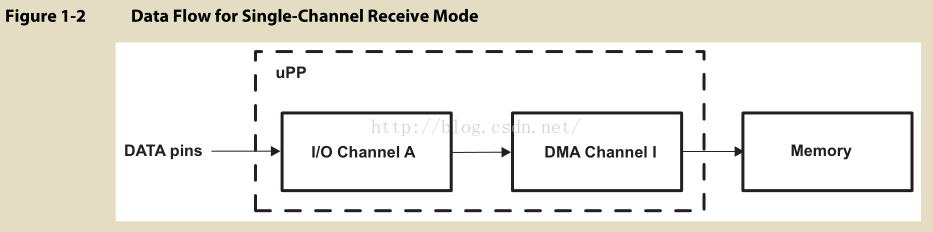

单通道接收模式

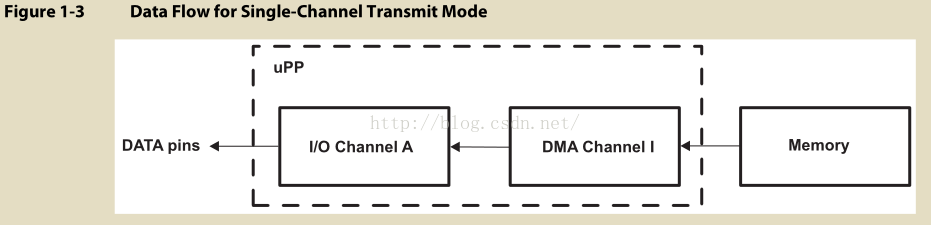

单通道发送模式

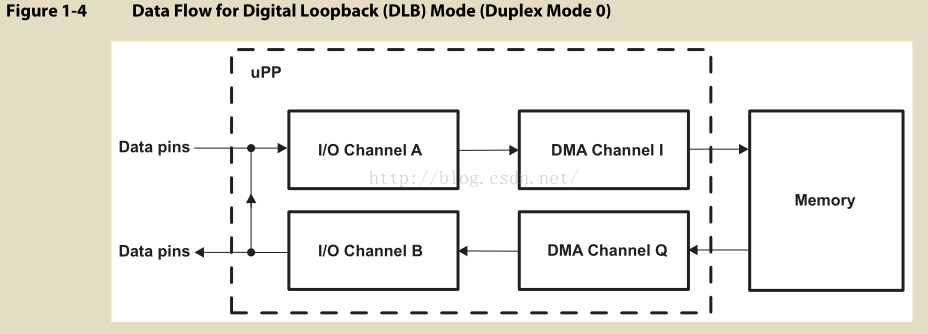

数字回环模式(用于自测)

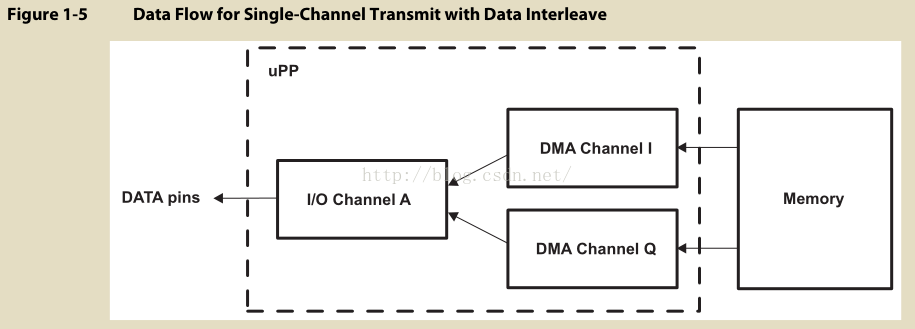

数据交叉单通道发送模式

图1-2,图1-3,图1-4,图通过UPP周边的各种配置1-5显示了简化的数据路径。注意,这些图是示例,并不代表所有可能的配置。

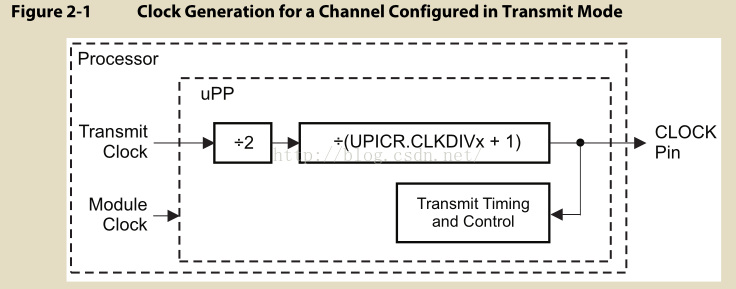

2.1 时钟产生与控制

uPP外设使用两个单独的时钟:模块时钟(控制其内部逻辑),以及运行在发送模式或者接口通道的发送时钟。这些时钟都是可配置的。不管是模块时钟,还是发送时钟都能可以比二分之一的设备CPU时钟速度更快。请参见特定器件的数据手册,了解更多信息。

各通道的时钟引脚,I / O时钟,独立地得到根据它的操作方向。

2.1.1 发送模式(单倍速率)

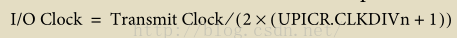

I/O时钟计算公式:

![]()

固定除数

本文档翻译了TI官方文档关于KeyStone架构下通用并行端口uPP的内容,介绍了uPP作为一种高速多通道并行接口,适用于ADCs、DACs和FPGA等设备的数据传输。uPP支持双向传输、多种数据宽度及协议,具有内部DMA控制器,详细阐述了其时钟控制、信号描述、数据交错模式、初始化配置和中断处理。文档还涵盖了uPP的复位、电源管理和仿真注意事项。

本文档翻译了TI官方文档关于KeyStone架构下通用并行端口uPP的内容,介绍了uPP作为一种高速多通道并行接口,适用于ADCs、DACs和FPGA等设备的数据传输。uPP支持双向传输、多种数据宽度及协议,具有内部DMA控制器,详细阐述了其时钟控制、信号描述、数据交错模式、初始化配置和中断处理。文档还涵盖了uPP的复位、电源管理和仿真注意事项。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1082

1082

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?