S3C2410/S3C2440的存储控制器有如下特性:

1.每个BANK的地址空间为128MB,总共1GB(8 BANKs);

2.可编程控制总线位宽(8/16/32-bit),不过BANK0只能选择两种位宽(16/32-bit);

3.总共8个BANK,BANK0~BANK5可以支持外接ROM、SRAM等,BANK6~BANK7除可以支持ROM、SRAM外,还支持SDRAM等。

4.BANK0~BANK6共7个BANK的起始地址是固定的。

5.BANK7的起始地址可编程选择。

S3C2410/S3C2440对外引出的27根地址线ADDR0~ADDR26的访问范围只有128MB,CPU还引出了8根片选信号nGCS0~nGCS7,对应于BANK0~BANK7,当访问BANKx的地址空间时,nGCSx引脚输出低电平用来选中外接设备。这样每个nGCSx对应128MB地址空间,8个nGCSx信号总共就对应了1GB的地址空间。地址如下:

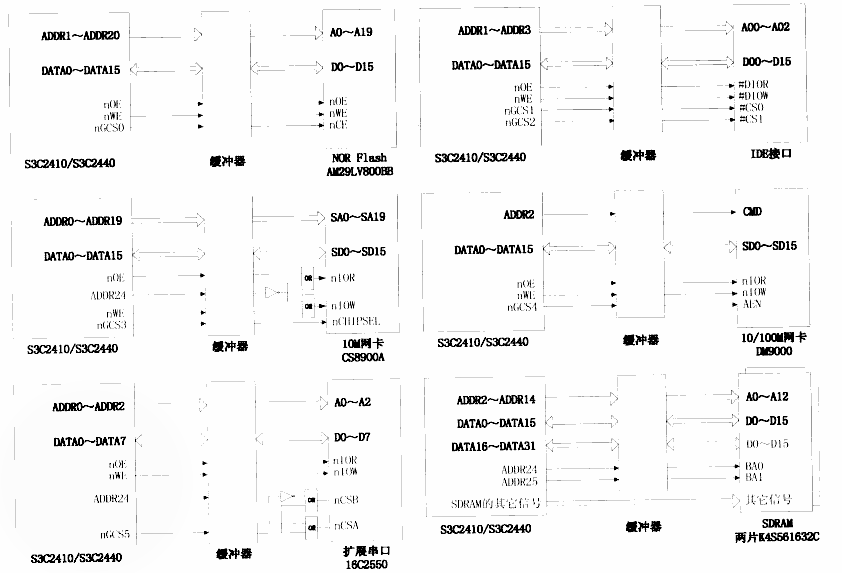

开发板上与外设的连接关系如图:

从第一个图可以知道各个BANK的起始地址,再结合第二个图用到的地址线就可以确定相关的外设访问地址了。

比如:

判断的时候注意外设用到了哪些ADDR线。

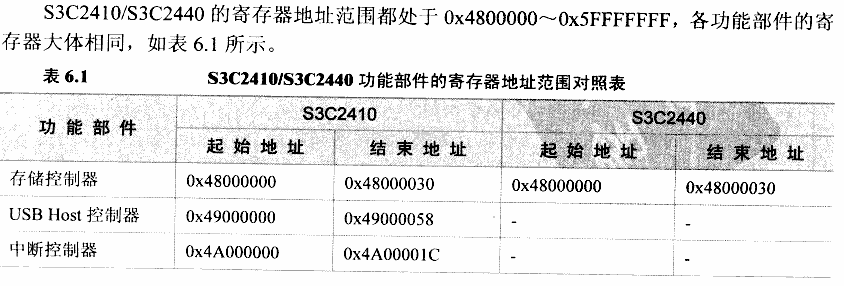

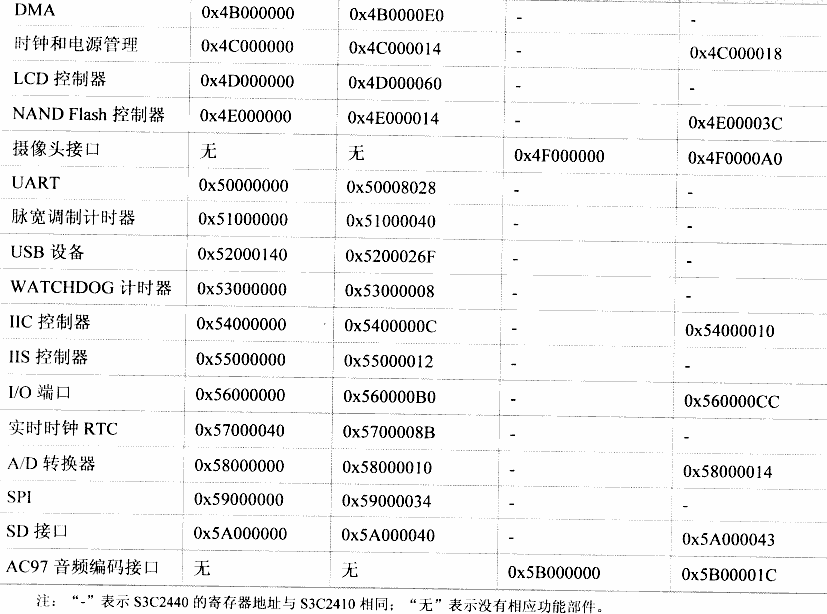

再附上两个图:

910

910

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?