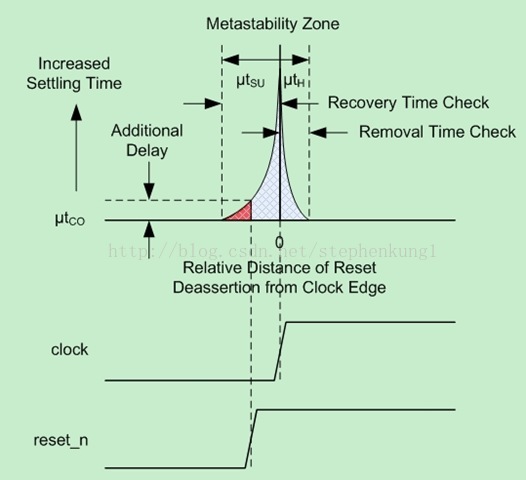

如图是器件工作时的电压变化,当reset_n在Recovery Time Check+Removal Time Check时间段内发生变化时会产生一个非高非低的信号,称之为亚稳态。如果电路有亚稳态存在会对之后的电路产生无法预测的错误,通过比较可得在各模块之间使用异步电路可以使电路简单化但会产生亚稳态,在各模块内部使用同步电路以便对电路性能进行测试有利于验证。因此要在各模块中涉及一个可以有效消除亚稳态的电路。现在比较通用的是异步复位同步释放(所谓异步复位,就是复位信号可以直接不受时钟信号影响,在任意时刻只要是低电平就能复位(假如约定低电平复位),也就是说,复位信号不需要和时钟同步。而同步释放就很有意思了,它的意思是让复位信号取消的时候,必须跟时钟信号同步,也就是说正好跟时钟同沿。)

下面是一个比较通用异步复位同步释放的verilog代码:

module prac (

clk,

reset_n,

dataa,

datab,

outa,

outb

);

input clk;

input reset_n;

input dataa;

input datab;

output outa;

output outb;

reg reg1;

reg reg2;

reg reg3;

reg reg4;

assign outa = reg1;

assign outb = reg2;

assign rst_n = reg4;

always @ (posedge clk or negedge reset_n) //“异步复位同步释放”的复位模块

begin

if (!reset_n)

begin

reg3 <= 1'b0;

reg4 <= 1'b0;

end

else

begin

reg3 <= 1'b1;

reg4 <= reg3;

end

end

always @ (posedge clk or negedge rst_n) //功能模块,注意rst_n是沿变驱动。

begin

if (!rst_n)

begin

reg1 <= 1'b0;

reg2 <= 1'b0;

end

else

begin

reg1 <= dataa;

reg2 <= datab;

end

end

endmodule

综合后的RTL图表如下:

这里的reg1,reg2时域DP实际上是经过reg3,reg4处理过的时域,假设reg3内rese_n与clk产生了亚稳态,由于已知亚稳态产生的电流是一个很小且短暂的信号那么当亚稳态的产生电流传到reg4时因为clk的限制导致传不到reg1,2,从而达到消除亚稳态的目的(reg4比reg3传导信号有一个周期的延迟)或许有人会说如果只加一个触发器由于clk的限制在reg1,2同样可以消除亚稳态,为什么要加两个?假设亚稳态在传到reg1,2时正好在clk的上升沿附近那么此时的亚稳态是没有办法消除的,而增加相同时域的D触发器就是避免此类现象的产生。实际上随着D触发器个数的增加亚稳态产生的概率是成平方倍的减少的,根据大量的工作经验一般在使用两个触发器后基本上就能避免亚稳态的产生。

(本文参考:《FPGA异步复位同步释放解析》作者:verilogic点击打开链接

203

203

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?