从零开始的FPGA学习5-同步复位D触发器、异步复位D触发器

原理

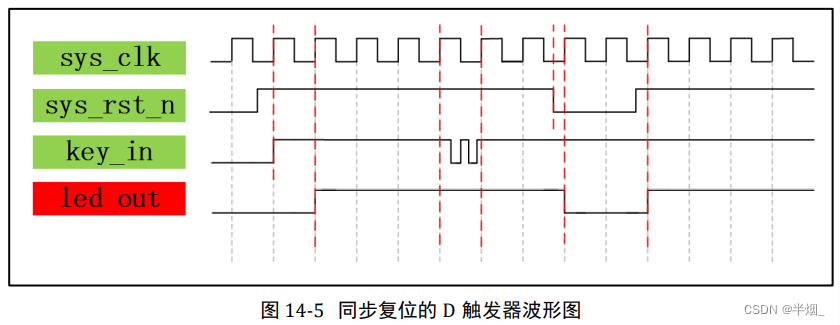

同步复位的 D 触发器

同步复位的 D 触发器中的“同步”是和工作时钟同步的意思,也就是说,当时钟的上升沿(也可以是下降沿,一般习惯上为上升沿触发)来到时检测到按键的复位操作才有效,否则无效。

如图 14-5 所示最右边的三根红色的竖线表达的就是这种效果,sys_rst_n 被拉低后 led_out 没有立刻变为 0,而是当 syc_clk 的上升沿到来的时候 led_out 才复位成功,在复位释放的时候也是相同原因。

异步复位的 D 触发器

异步复位的 D 触发器中的“异步”是和工作时钟不同步的意思,也就是说,寄存器的复位不关心时钟的上升沿来不来,只要有检测到按键被按下,就立刻执行复位操作。

如图14-6 所示最右边的两根红色的竖线表达了这种效果,sys_rst_n 被拉低后 led_out 立刻变为0,而不是等待 syc_clk 的上升沿到来的时候 led_out 才复位,而在复位释放的时候 led_out不会立刻变为 key_in 的值,因为还要等待时钟上升沿到来到时才能检测到 key_in 的值,此时才将 key_in 的值赋值给 led_out。

本文详细介绍了同步复位和异步复位D触发器的工作原理,强调了它们在处理毛刺和时序逻辑上的特点。同步复位在时钟上升沿检测复位,而异步复位则即时响应。同时,文中通过代码展示了如何实现这两种触发器,突显了时序电路在提高数据可靠性和屏蔽干扰方面的重要性。

本文详细介绍了同步复位和异步复位D触发器的工作原理,强调了它们在处理毛刺和时序逻辑上的特点。同步复位在时钟上升沿检测复位,而异步复位则即时响应。同时,文中通过代码展示了如何实现这两种触发器,突显了时序电路在提高数据可靠性和屏蔽干扰方面的重要性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?