引言

前面我们分析了ORPSoC的整体架构,并对其子系统进行了深入的分析和了解。但对于ORPSoC的核心模块or1200_top及其内部的core--or1200_cpu模块却鲜有涉及,算是ORPSoC分析的盲区,也是蒙在我心里的一片乌云。

本小结就对这两个模块的整体架构进行分析,扫除这块所谓的‘盲区’和‘乌云’。

1,a general picture

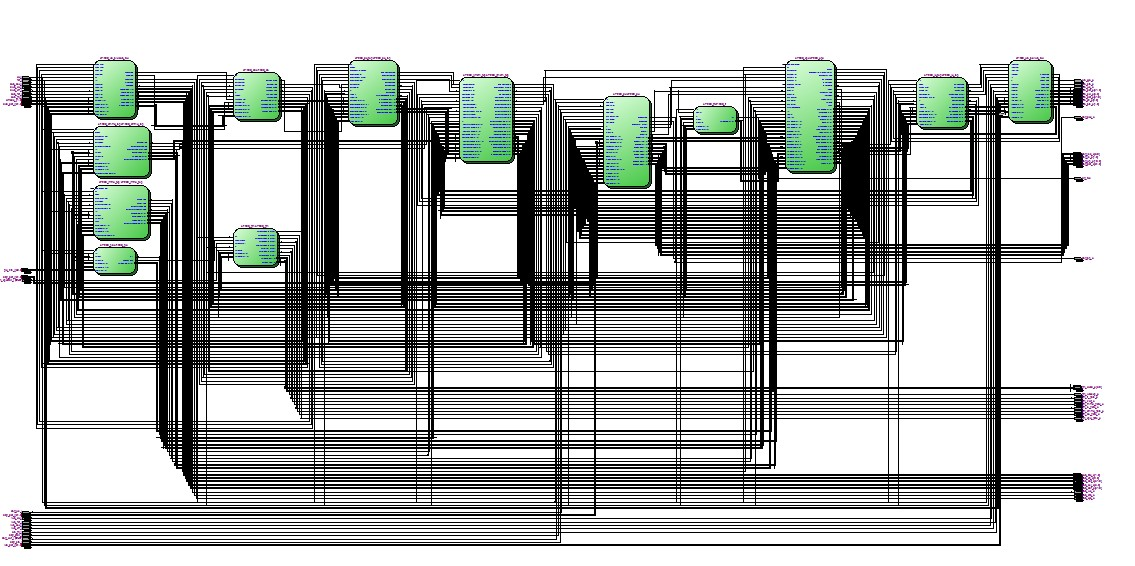

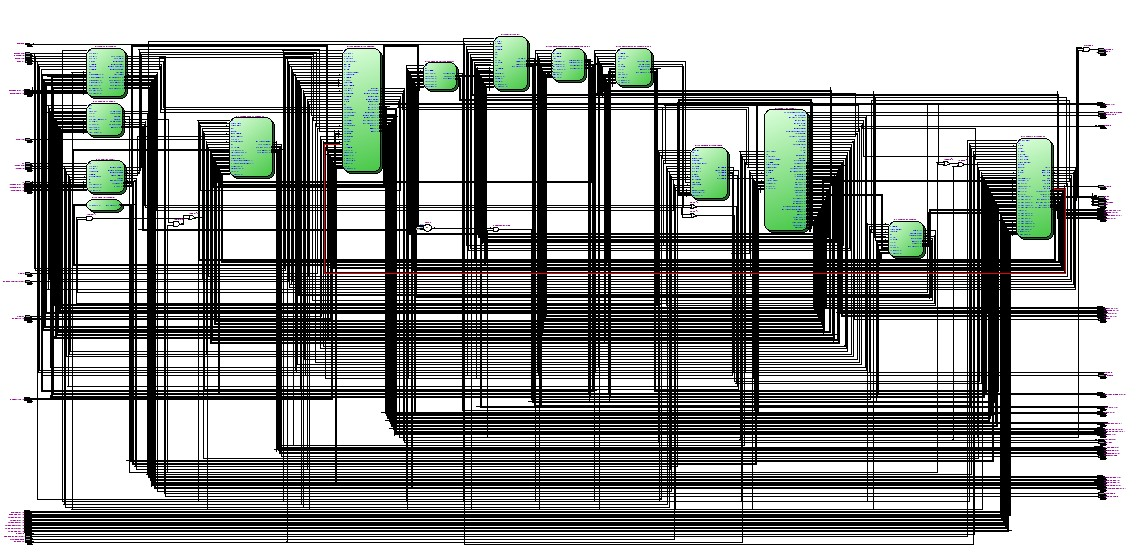

按照惯例,还是先对这两个模块有一个感性认识。下面就是or1200_top和or1200_cpu的模块连接图。

CPU模块:or1200_top

core模块:or1200_cpu

2,CPU整体架构

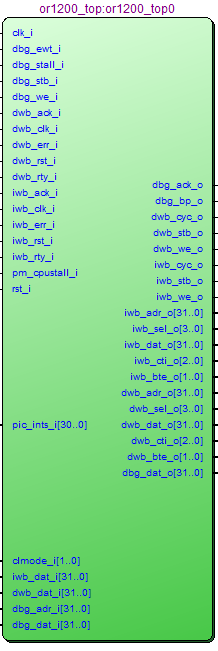

1>模块接口

下面就是CPU的实际模块接口图,从中我们可以清晰的看到一个CPU的外部接口。

2>模块整体架构图

上面我们了解了CPU的模块接口,但是其接口比较多,我们需要对这些接口进行分类,画出其接口简图,如下:

从中我们可以看出CPU与外部进行数据交换和控制的接口,以及其模块组成。

经过分析对应的RTL代码,我们可以知道:默认配置下&#x

本文深入分析了OpenRISC的CPU模块or1200_top和core模块or1200_cpu的整体架构,包括模块接口、数据流图和执行过程。详细解释了load/stor指令的执行流程,并探讨了CPU的Harvard结构和5级流水线设计。通过对RTL代码的研究,揭示了CPU的内部工作机制,从而全面理解OpenRISC 1200的处理器设计。

本文深入分析了OpenRISC的CPU模块or1200_top和core模块or1200_cpu的整体架构,包括模块接口、数据流图和执行过程。详细解释了load/stor指令的执行流程,并探讨了CPU的Harvard结构和5级流水线设计。通过对RTL代码的研究,揭示了CPU的内部工作机制,从而全面理解OpenRISC 1200的处理器设计。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3656

3656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?